声明

下面的题目作答都是自己认为正确的答案,并非官方答案,如果有不同的意见,可以评论区交流。

这些题目也是笔者从各个地方收集的,感觉有些题目答案并不正确,所以在个别题目会给出自己的见解,欢迎大家讨论。

题目

1.standard cell库中寄存器的D pin的setup required time 既可以是正值可以是负值()

答案:对

2.为了降低功耗,在某个状态下,对不关心的存器的输出值(即对系统运行没有影响的寄存器),优化的低功耗设计方法是将其固定为0或者1()

答案:错

解析:将其值保持不变,降低翻转。

3.关于时钟门控描述错误的是()

A模块级时钟门控可以手动例化

B代码书写风格(codingstyle)会影响时钟门控的插入

C插入时钟门控会导致静态功耗增加

D为降低动态功耗,应尽量多的插入时钟门控

答案:C

解析:门控时钟降低静态功耗

5.I2C协议采用推挽(push-pul)输出,输出1和输出0时分别由MOS管驱动输出高电平和低电平()

答案:错

解析:I2C协议采用开漏输出,输出1时由上拉电阻上拉为1。

6.有符号数右移需要使用哪种操作符()

解析:使用>>>进行算数右移,左侧扩位符号位n位,右侧删除n位即进行除n运算。

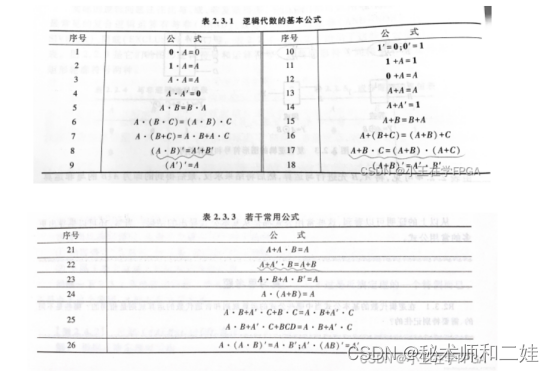

7.逻辑化简Y=ABC+AB+B C+BD结果为()

8.时序逻辑中case分支未写全时,可以不用加default分支()

答案:正确

解析:组合逻辑未写defalut会生成锁存器,时序逻辑不会。

9.在DC优化timing的时候,工具采用下面那个命令可以通过移动寄存器来达到调整时序优化的目的()

A. compile_ultra -retime

B. compile ultra -timing high effort

C.compile ultra -incremental

D.compile ultra -piple

在DC(Design Compiler)优化时,通过移动寄存器来进行时序优化的命令是:

A. compile_ultra -retime

选项A中的命令compile_ultra -retime用于启用寄存器重定位(retiming)操作,它会尝试重新安排逻辑和寄存器的位置,以改善时序性能。该命令会对设计进行全局的时序优化,并通过移动寄存器来调整时序。

选项B的命令compile ultra -timing high effort没有明确的指令来移动寄存器来达到调整时序优化的目的。该命令中的"-timing high effort"参数表示对时序约束进行更高的优化尝试。

选项C的命令compile ultra -incremental用于增量编译,它并不是针对移动寄存器进行时序

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

3923

3923

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?