FPGA建立时间、保持时间原理总结

FPGA时序分析的前提是充分理解建立时间、保持时间等基本参数的由来,下面将FPGA中D触发器(FF)的Tco、Tsetup(建立时间)、Thold(保持时间)基于原理总结如下。

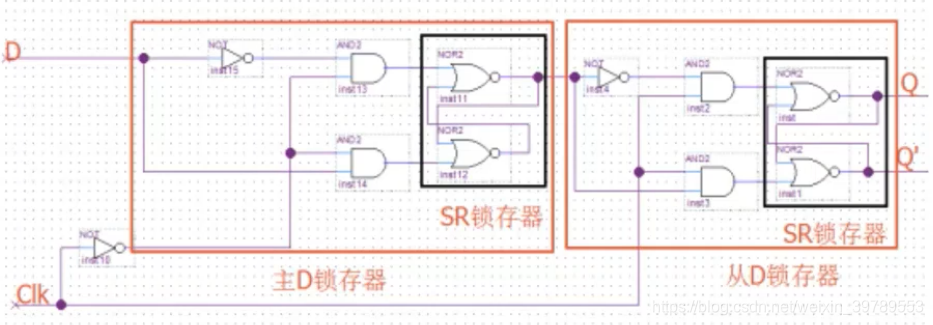

一、D触发器内部组成

D触发器主要由主锁存器和从锁存器组成,在时钟信号CLK上升沿时,将输入端信号D输出到Q端。基本工作过程是:当CLK为低电平时,将输入信号D锁存到主锁存器中,当CLK由低电平转变为高点平时,将主锁存器中的值通过从锁存器输出到Q端。

二、参数的基本概念

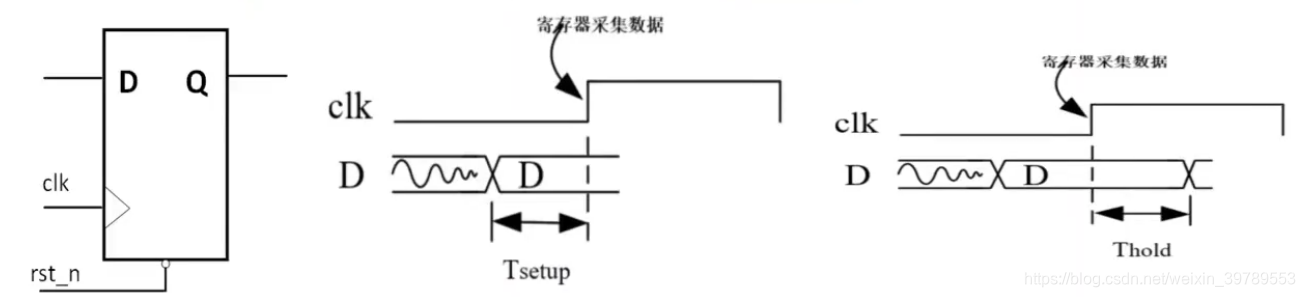

如下图,建立时间Tsetup是CLK采样前输入信号D需要提前维持的时间,保持时间Thold是CLK采样后输入信号D需要继续保持的时间,注意:这个需要关注的是输入信号D的变化。

三、参数的基本原理

Tco

Tco是D触发器的固有延时,是从D触发器的时钟端检测到时钟信号CLK的跳变沿,到D触发器的输出信号稳定下来的时间。当时钟信号CLK为0时,输入信号D被所存到主锁存器中,当时钟信号CLK由0变为1时,在主锁存器中的信号将通过Tco延时从锁存器输出到Q端。

Tsetup(建立时间)

Tsetup是D触发器输入数据的建立时间。当时钟信号CLK为0时,主锁存器开启,从锁存器关闭,输入信号D将被锁存到主锁存器中,由于在锁存的过程中经过了主锁存器的组合逻辑延时,在这个过程中,需要保持输入信号D不变,因此会有Tsetup建立时间。

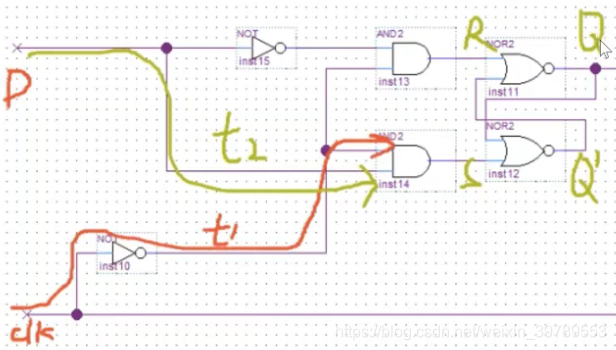

Thold(保持时间)

Thold是D触发器输入数据的保持时间。时钟信号CLK由0变为1是需要一定延时的,CLK变为1之前,主锁存器还是处于开启状态,输入信号D的任何变化都会影响到中间锁存的数值(主锁存器的输出值),并且CLK由0变为1中间有一个反相器的延时t1,该延时大于输入信号路径的延时t2,因此需要输入信号D保持一段时间,因此会有Thold保持时间。

4万+

4万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?