首先需要明确,无论是组合逻辑还是时序逻辑,在always块中的变量在声明时都必须为reg类型。

但是对于两种情况,综合器会将二者都综合成同一类型吗?下面以实际例子分析:

在下面的Verilog中,a_temp由组合逻辑产生,b_temp由时序逻辑产生:

module full_add(

input clk,

input [3:0]a,

input [3:0]b,

output [7:0]c,

output [3:0] d

);

reg [3:0]a_temp;

reg [3:0]b_temp;

always@(*)

begin

a_temp=a;

end

assign c=a_temp;

always@(posedge clk)

begin

b_temp<=b;

end

assign d=b_temp;

endmodule

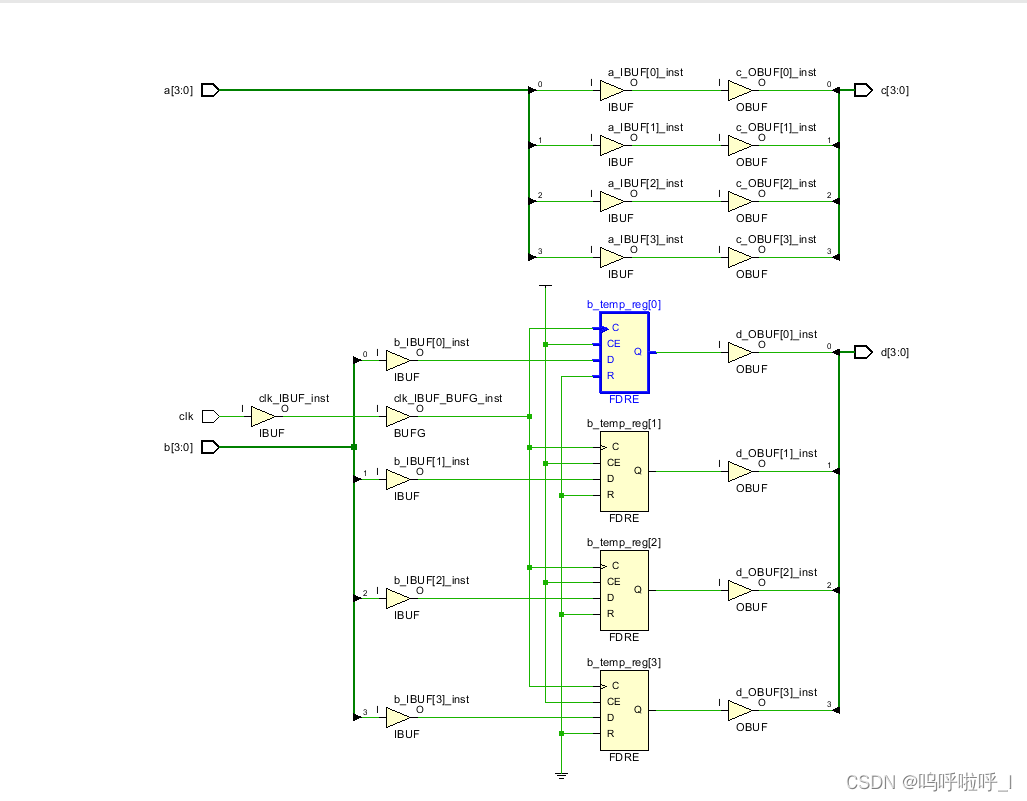

二者的综合的结果如下:

我们可以发现,在综合结果中,a_temp被综合为wire型,b_temp被综合为触发器。因此即使二者在声明时都被声明为寄存器,但也会根据其是组合逻辑还是时序逻辑得到不同的综合结果。

下面再介绍一种情况:

module full_add(

input en,

input [3:0]a,

input [3:0]b,

output [3:0]c,

output [3:0]d

);

reg [3:0]a_temp;

reg [3:0]b_temp;

always@(*)

begin

if(en)

a_temp<=a;

end

assign c=a_temp;

always@(*)

begin

if(en)

b_temp<=b;

else

b_temp<=0;

end

assign d=b_temp;

endmodule

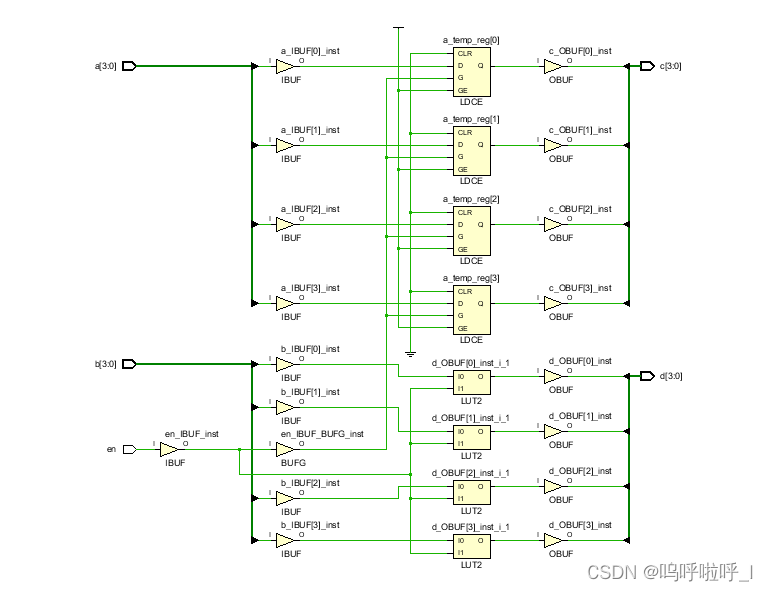

我们可以发现对于未完整赋值的情况,会将reg综合成锁存器;而完整赋值的情况reg会被综合为wire连线。

总结如下:

描述组合逻辑的always块中,寄存器被综合成wire型;如果存在不完整的赋值的情况,则被综合成锁存器。在描述时序逻辑的always块中,寄存器则根据语句块的内容被综合成触发器。

2602

2602

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?