BiSS-C 协议(Bi-directional Synchronous Serial-C)是一种用于高精度工业控制中的开放式双向同步串行通信协议,常用于位置传感器、编码器和控制系统之间的数据交换。BiSS 协议的特点是支持高分辨率的实时数据传输,并具备误差检测功能,适用于工业自动化、机器人、机床和精密运动控制领域。BiSS-C 是 BiSS 协议的其中一个版本,主要有以下几个关键特性:

1)双向通信,BiSS-C 支持全双工(Full Duplex)通信,这意味着主机(Master)可以同时向从设备(Slave)发送控制命令,同时接收从设备的反馈数据。这样允许传感器设备可以在同一个时钟周期内进行数据的读写。

2)同步数据传输,BiSS-C 是同步协议,数据传输与时钟同步,因此不需要单独的时钟线。它采用同步串行通信方式,时钟线由主设备提供,数据线用于在主设备与从设备之间传递数据。

3)高精度和实时性,BiSS-C 支持多达 48 位的数据位宽,满足高精度位置和速度测量的需求,同时能够在较高的频率下运行,通常达到 10 MHz 以上的传输速率,确保了数据的实时性。

4)误差检测和校验,BiSS-C 协议包含错误检测机制,例如 CRC 校验,能够检测传输过程中的数据错误。此外,BiSS-C 还支持安全模式,可以识别数据完整性并在通信错误时报警。

5)开放性和兼容性,BiSS-C 是一个开放协议,不受专利限制,可以在多种硬件平台和不同制造商的设备上实现。这使得 BiSS-C 被广泛应用于工业自动化领域。

17.1 硬件协议

BISS-C协议的硬件,兼容422、485、UART、SPI、TTL,不过在控制器和外部设备之间的通信,通常使用422和485的接口,因为其使用差分进行数据传输,有较强的抗干扰能力。

17.2 软件协议

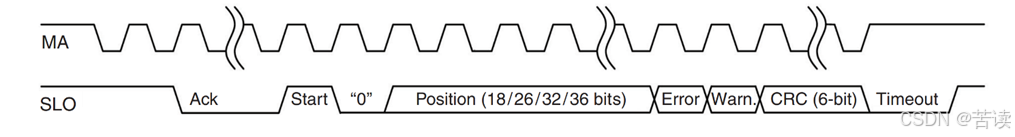

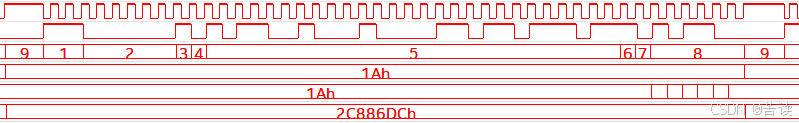

BISS-C协议的软件,和IIC有异曲同工之妙,都是,一根时钟线和一根数据线,其协议的帧结构如下图所示。

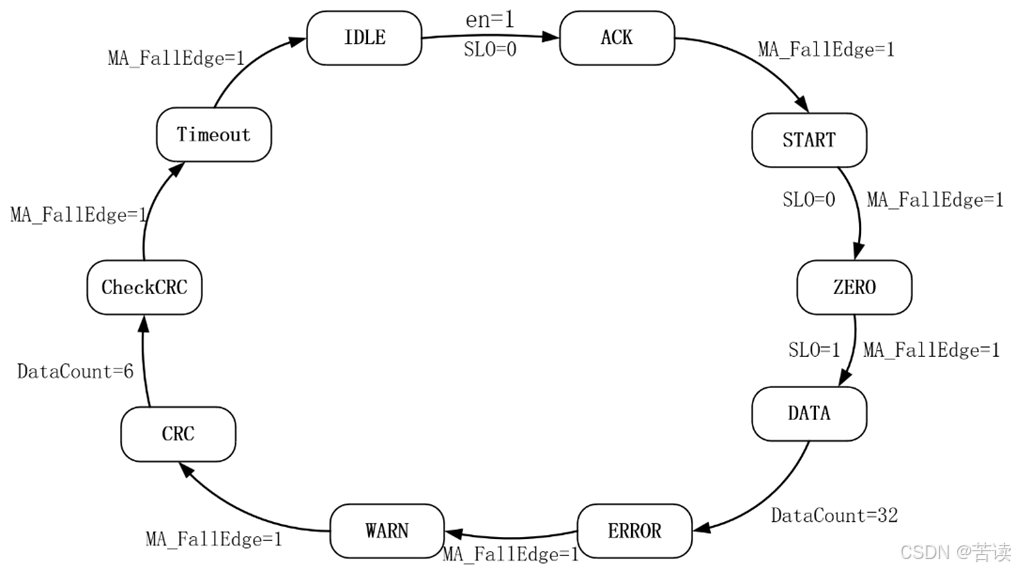

根据上图,可以画出状态转移图,如下图所示。

在协议中有提到:

“MA”:transmits position acquisition requests and timing information (clock) from master to encoder。

“SLO”:transfers position data from encoder to master, synchronised to MA。

翻译一下就是,MA时钟由FPGA发出,SLO数据由外设发送到FPGA。那么,第一步,首先是设计MA的时钟,MA时钟关系着传输速率,最高速率为10M,但通常系统时钟为50M,100M甚至更高,因此,要输出MA时钟是需要先对系统时钟进行降频处理的。

根据上述的帧结构示意图来看,MA时钟并不是所有时间线都有的,整个BISS-C协议就是从MA时钟信号的下拉开始的,也就是说,MA开始下拉就是使能信号有效的时刻,然后,MA就以最大值为SYSCLK / MASPEED的计数器进行高低电平变换,MA时钟在何时上拉?根据帧结构示意图看,MA在校验数据接收完成后,即状态TIMEOUT时上拉。代码如下:

assign MA = (en && (next_state<TIMEOUT) ) ? MA_reg : 'b1; //需要请求数据的时候,再发送MA时钟,其他时刻,MA置1完成MA时钟的设计之后,我们的BISS-C解码模块就可以往外发送MA时钟信号了,当编码器或传感器收到FPGA发来的时钟信号,就可以进行响应和数据发送了。

正常情况下,由编码器发送的SLO信号,应该是默认上拉的,也就是说,在没有收到MA时钟的时候,SLO保持上拉,;收到MA时钟后,SLO会产生一个低电平的响应,这个响应,就是上述帧结构图里面的ACK,有一点需要注意,ACK的持续时间(第一个低电平的持续时间)是不固定的,和MA时钟的频率有关,,MA频率越快,ACK所占的MA周期越多,所以,是不是因为编码器的响应时间是固定的?

接下来可以根据上述的状态转移图来实现,逻辑代码的状态转移,如下图所示:

// 状态转移表(次态)

always @(*) begin

if (!rst_n) begin

next_state <= IDLE;

end

else begin

case (state)

IDLE : next_state <= (en&&(!SLO)) ? ACK : IDLE;

ACK : next_state <= ((SLO)) ? START : ACK;

START : next_state <= ((!SLO)) ? ZERO : START;

ZERO : next_state <= ((SLO)) ? DATA : ZERO;

DATA : next_state <= (MA_RiseEdge_Count == DATA_BIT + 'd1) ? ERROR : DATA;

ERROR : next_state <= (MA_RiseEdge) ? WARN : ERROR;

WARN : next_state <= (MA_RiseEdge) ? CRC : WARN;

CRC : next_state <= (MA_RiseEdge_Count == CRC_BIT + 'b1) ? TIMEOUT : CRC;

TIMEOUT : next_state <= (SLO) ? IDLE : TIMEOUT;

default : next_state <= IDLE;

endcase

end

end在上图中的ACK,START和ZERO状态中,因为这三个状态的电平是确定的,因此,只需要从SLO信号的电平即可完美的进行状态转移,但开始接收数据和警告错误码之后,并不能从‘0’‘1’状态明显的判断出逻辑状态。因此,需要一个MA上升沿的时候,进行状态转移的判断,将MA进行上升沿判断,判断出来后,输出一个MA_RiseEdge信号,根据该信号来进行状态转移即可。

实现了状态转移后,就可以在各个状态进行数据输出,在DATA状态计数满DATA_BIT后,就进入下一状态,同时输出收到的data。data,error,warn,CRCdata这几个数据的接收都是如此。

17.3 CRC校验

校验是常用的一种验证数据传输是否正确的方法,常见的校验方法有奇偶校验,CRC校验等方法。奇偶校验在传输数据的每一组(通常是一个字节或多个比特)中加入一个校验位,使得整个组的1的数量保持为偶数或奇数。但又一个缺陷就是,如果我出错的位数是两个的时候,该方法就检验不出来了。但该方法开销少,实现简单,适合数据量少,误码率低的情况。

CRC校验基于多项式除法,将数据视为一个二进制多项式,通过与一个预定义的生成多项式(生成多项式的长度决定了 CRC 位数)进行模 2 除法,得到一个校验码。发送时,将该校验码附加到数据后面,接收方则对接收的整个数据(含校验码)重新进行 CRC 运算,若结果为零,则数据无误;否则,表示发生了错误。还有种方法就是,只对数据位进行模2除法,比较接收到的CRC数据和接收端自己计算的数据进行比较,若一致,则数据无误。

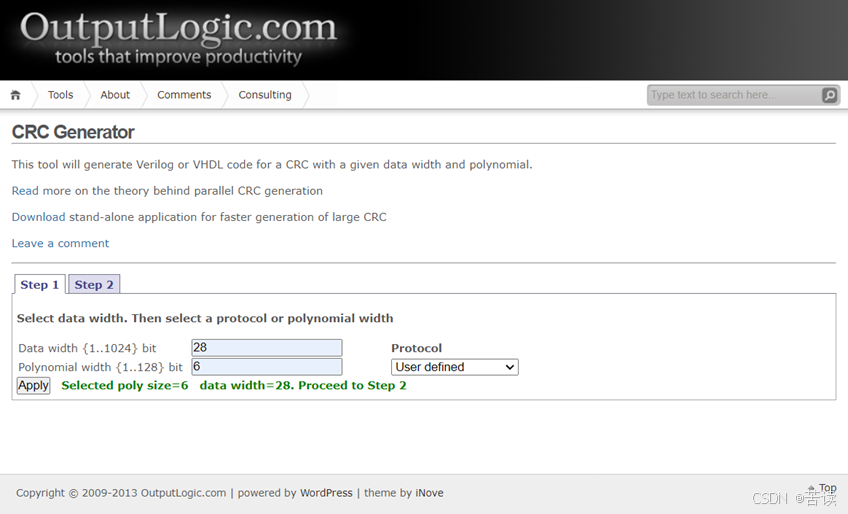

CRC的FPGA实现,关键在于理解多项式,BISS-C中,校验的多项式如下。

用二进制表示就是1000011,因为6-0是七个数字,所以是7位二进制码。

手动计算的方法很简单,在数据位后面添6个0(最高位为6),然后用数据对1000011进行短除(异或)处理,最后的余数,就是校验结果。有在线计算的网站可以帮忙计算CRC余数(http://www.ip33.com/crc.html)。

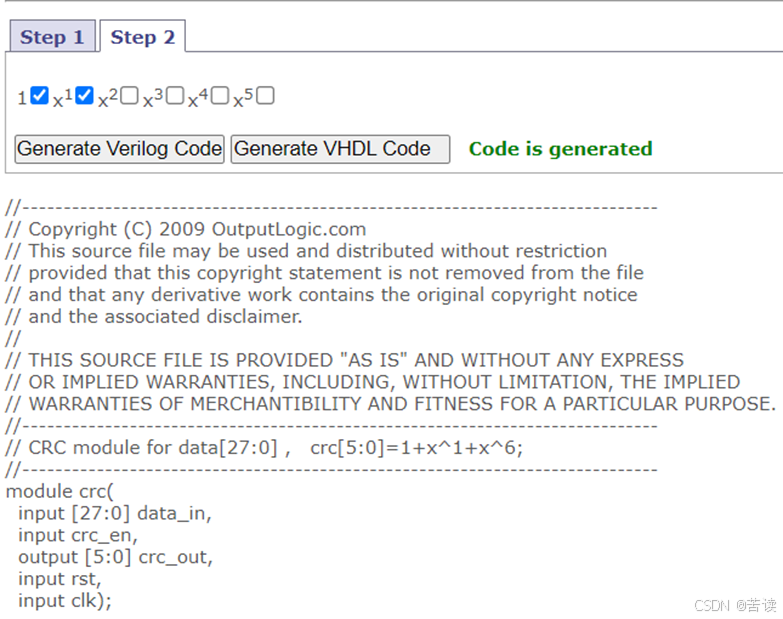

此外,CRC校验的Verilog代码,可以直接生成(http://outputlogic.com/?page_id=321)。

选好之后,就进入第二步,需要注意的是,我们通常,多项式,不用选择最高项,因为CRC 多项式的最高位可以忽略是因为在CRC运算中,最高位始终是隐含的且为1,用于保证多项式的阶数。

将生成的CRC校验模块放入工程中,在top.v中进行例化,就可以将计算的CRC校验码和收到的CRC校验码进行比较,若相等,则说明校验通过,输出数据和数据有效信号。除此之外,需要注意,BISS-C协议中的并不是用数据位进行校验的,而是用数据位加上错误位和警告位再进行CRC校验的。

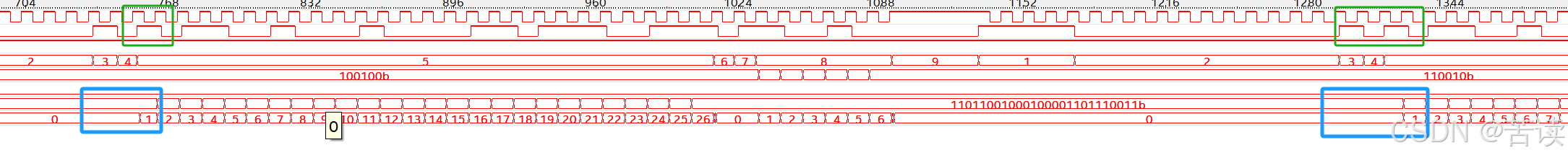

最终通过片上逻辑分析仪可以抓取的波形如下图所示。

至此,就完成了BISS-C协议的解析,但仍有以下几点需要特别注意或改善的点:

- MA时钟发送到编码器再到接收到SLO信号其实是有一定的延迟的,这个延迟抛开编码器上的反应延迟之外,还有 线缆长度/光速 这样的一个传输延迟,这个延迟会影响SLO数据的接收,有的时候,会接收少一个位。可以在数据接收状态使用计数器进行计数,每满 SYSCLK/MASPEED 则表示接收到一个数据,这样可以完美的匹配数据接收后的每一个电平。

- 根据逻辑状态图来进行逻辑设计,输出信号的逻辑,通常根据next_state的状态来确定,这是因为next_state的状态会在下一时刻展示在state上,而根据next_state来做出设计的输出逻辑,就也能和state进行同样的变化。

- 当前代码在MA时钟最大时,偶尔逻辑分析仪抓取不到SLO信号,但根据电流,422指示灯等来观察,确认SLO是在往外发送信号的。

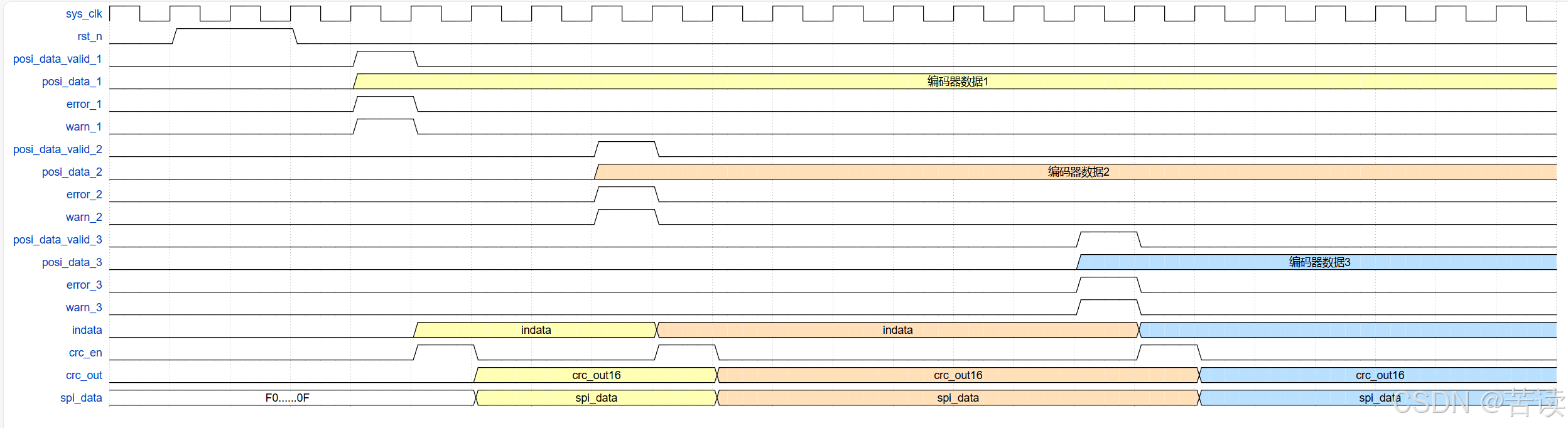

17.4 改进点

本设计思路过于臃肿,且存在状态和SLO无法一一对应导致接收数据发生跳变的问题,尤其在上位机上的角度增长图中出现较为明显的跳变(如图17.4.1所示),因此,主要针对该问题进行改进,首先,数据位,错误位,警告位和校验位的数据接收可以放到一起接收26+2+6的数据,然后再从总的接收数据里面接收就行,此外,优化了时钟结构,取消对时钟上升沿的判断,采用时钟计数的方式来实现对上升沿的判定。

17.4.1 信号异常

此外,仅保留6个状态机来进行处理,也加强了数据处理的速度,改进的模块时序逻辑图如下图17.4.2所示。

17.4.2 时序逻辑图

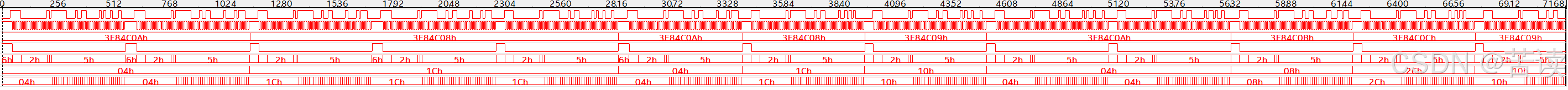

根据该方法来实现的BISSC解码器,可解决接收数据偶发跳变问题且优化了代码结构,实现编码器数据的稳定接收。信号探测仪抓取到的数据如下图17.4.3所示。

17.4.3 信号探测仪抓取到的编码器位置数据

2万+

2万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?