6.FPGA(MIG)与DDR3连接示意图

6.1 DDR端口介绍

| 符号 | 类型 | 功能 |

| CK、CK# | 输入 | 时钟:CK和CK#是差分时钟输入。所有地址和控制输入信号均为在CK的上升沿和CK#的下降沿的交点上采样 |

| CKE,(CKE0),(CKE1) | 输入 | 时钟使能。使能(高)和禁止(低)内部电路和DRAM上的时钟。由DDR3SDRAM配置和操作模式决定特定电路被使能和禁止。CKE为低,提供PRECHARGE POWER-DOWN和SELF REFRESH操作(所有Bank都处于空闲),或者有效掉电(在任何bank里的行有效)。CKE与掉电状态的进入退出以及自刷新的进入同步。CKE与自刷新的退出异步,输入Buffer (除了CK、CK#、RESE T#和ODT)在POWER-DOWN期间被禁止。输入Buffer (除了CKE和RESET#)在SEL _F REFRESH期间被禁止。CKE的参考是VREFCA |

| CS#,(CS0#),(CS1#),(CS2#),(CS3#) | 输入 | 片选:当CS#为高时,所有命令均被屏蔽。CS#提供外部 具有多个等级的系统上的等级选择。CS#被视为命令代码的一部分。 |

| ODT,(ODT0),(ODT1) | 输入 | 片上终端使能:ODT使能(高)和禁止(低)片内终端电阻 |

| RAS#,CAS#.WE# | 输入 | 命令输入:RAS#,CAS#和WE#(以及CS#)定义了要输入的命令。 |

| DM.(DMU),(DML), | 输入 | 数据输入屏蔽:DM是用于写入数据的输入掩码信号。 在写访问期间采样到的高电平,输入数据被屏蔽 |

| BA0-BA2 | 输入 | BANK址输入:BA0-BA2定义ACTIVATE、读取、写入或PRECHARGE是对哪个BANK操作的。 |

| A0-A15 | 输入 | 地址输入:为ACTIVATE命令提供行地址,为读取/提供列地址 编写命令以从相应存储体的存储器阵列中选择一个位置。。地址输入还提供操作码 在模式寄存器设置命令期间。 |

| A10-AP | 输入 | 自动预充位:A10在PRECHARGE命令期间被采样,已确定PRECHARGE是否应用于某个BANK;A10为低,这个BANK由BA[2:0]来选择,A10为高,对所有BANK。 |

| A12/BC# | 输入 | burst chop:在读取和写入命令期间对A12 / BC#进行采样,以确定是否存在burst chop将被执行。(高,无burst chop;低:burst chop)。见命令表以了解详细信息。 |

| RESET# | 输入 | 低电平有效异步复位:当RESET#为低电平时,复位有效。在正常操作期间,RESET#必须为高。 |

| DQ | 输入输出 | 数据输入输出:双向数据总线 |

| DQU,DQL,DQS,DQS#,DQSU,DQSU#,DQSL,DQSL# | 输入输出 | 数据选通:读时输出,边缘与读出的数据对齐,写时输入,中心与写数据对齐。 |

6.2 MIG_UI端口介绍

FPGA的MIG IP核用户界面接口

| app_addr[ADD_WIDTH-1:0] | 输入 | 此输入指示当前提交给UI的请求的地址。 UI聚合外部SDRAM的所有地址字段,并提供平面地址空间(Rank,bank,row,colum) |

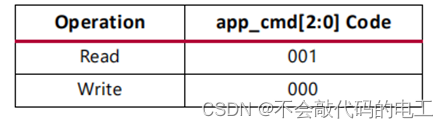

| app_cmd[2:0] | 输入 | 此输入指定当前提交给UI的请求的命令。

|

| app_en | 输入 | 此输入在请求中变化。你必须将所需的值 应用于app_addr[]和app_cmd[2:0],然后断言app_en以将请求提交给UI。这会通过断言app_rdy来启动UI确认的握手 |

| app_wdf_data[APP_DATA_WIDTH-1:0] | 输入 | 在总线提供当前正在写入外部存储器的数据 |

| app_wdf_end | 输入 | 此输入指示当前周期中app_wdf_data[]总线上的数据是当前请求的最后一个数据。 |

| app_wdf_wren | 输入 | 此输入表示app_wdf_data[]总线上的数据有效 |

| app_wdf_rdy | 输出 | 此输出表示写数据FIFO已准备好接收数据。当app_wdf_rdy和app_wdf_wren都被声明时,接受写入数据。 |

| app_wdf_mask[APP_MASK_WIDTH-1:0] | 输入 | 该总线指示app_wdf_data []的哪些字节写入外部存储器以及哪些字节保持其当前状态。 通过将值1设置为app_wdf_mask中的相应位来屏蔽字节。 例如,如果应用程序数据宽度为256,则掩码宽度取值为32. app_wdf_data的最低有效字节[7:0]使用app_wdf_mask的Bit [0]屏蔽,app_wdf_data的最高有效字节[255:248]使用app_wdf_mask的Bit [31]屏蔽。 因此,如果必须屏蔽最后一个DWORD,即app_wdf_data的字节0,1,2和3,则app_wdf_mask应设置为32’h0000_000F。 |

| app_rdy | 输出 | 此输出指示你是否接受当前提交的UI的请求。如果在确认app_en后UI未声明此信号,则必须重试当前请求。如果出现以下情况,则不会声明app_rdy输出:1.PHY/内存初始化尚未完成;2.所有bank都被占用(可以看作命令缓冲区已满);3.请求读取并且读取缓冲区已满;4.正在插入定期读取。 |

| app_rd_data[APP_DATA_WIDTH-1:0] | 输出 | 此输出包含从外部存储器读取的数据。 |

| app_rd_data_end | 输出 | 此输出表示当前周期中app_rd_data[]总线上的数据是当前请求的最后一个数据。 |

| app_rd_data_valid | 输出 | 此输出表明app_rd_data[]总线上的数据有效 |

| ui_clk_sync_rst | 输出 | Reset信号来自于UI,与ui_clk同步 |

| ui_clk | 输出 | 这是UI的输出时钟。 它必须是输出到外部SDRAM的时钟频率的一半或四分之一,这取决于在GUI中选择的2:1或4:1模式。 |

| init_calib_complete | 输出 | 校准完成后,PHY将init_calib_complete置‘1’。 在将命令发送到内存控制器之前,应用程序无需等待init_calib_complete。 |

| app_ref_req | 输入 | 置位时,此高电平有效输入请求内存控制器向DRAM发送刷新命令。 它必须在一个周期内进行脉冲以发出请求,直到app_ref_ack信号被置位以确认请求并指示它已被发送,然后置为无效。 |

| app_ref_ack | 输出 | 置位时,此高电平有效输入确认刷新请求,并指示该命令已从存储器控制器发送到PHY。 |

| app_zq_req | 输入 | 置位时,此高电平有效输入请求存储器控制器向DRAM发送ZQ校准命令。 它必须在一个周期内进行脉冲以发出请求,直到app_zq_ack信号被置位以确认请求并指示它已被发送,然后取消置位。 |

| app_zq_ack | 输出 | 置位时,此高电平有效输入确认ZQ校准请求,并指示该命令已从存储器控制器发送到PHY。 |

519

519

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?