前言

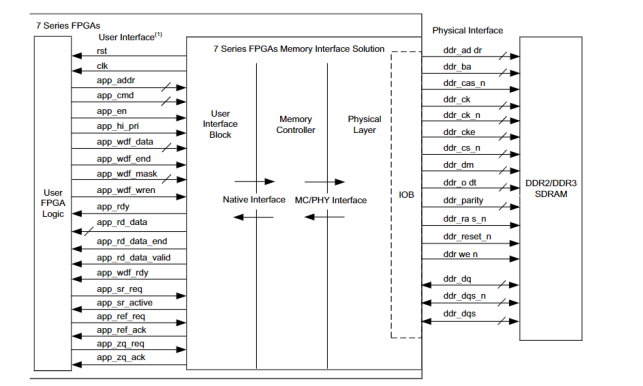

截图取自Xilinx官方手册ug586,figure1-51,MIG IP核是一个逻辑模块,相当于是由它连接了DDR芯片,对内给用户封装了接口(User FPGA Logic),便于用户使用。从图中可以看出,将用户侧和物理侧通过控制器进行了逻辑上的划分,由此也引出来用户侧的一系列问题。下面关于MIG IP核的接口和时序以及MIG IP的配置进行说明。

1.MIG IP接口信号

- init_calib_complete:output信号

板卡上电后,DDR3 IP核会对DDR进行初始化校正。完成之后IP核拉高此信号,因此用户只有在监测到该信号为高电平后,才能对DDR进行读写操作(PHY asserts init_calib_complete when calibration is finished)。

- app_addr:input信号

将DDR实际的行信号,列信号,bank信号转换为逻辑地址信号,这个信号应该等于30bit=1bit rank+3bit bank+16bit row address + 10bit row address(以MT41K512M16HA-125AIT为例),30bit中的最高位rank为是冗余位,并没有用到。

- app_cmd:input信号

3bit的IP核操作码输入,000为写命令,001为读命令

- app_en: input信号

IP核的命令使能输入。这是app_addr[]和app_cmd[2:0]输入的激活高电平触发信号。

- app_rdy: output信号

IP核输出的ready就绪信号。此输出表示UI已准备好接受命令。如果app_en启用时app_rdy被撤销,则必须重试当前的app_cmd和app_addr,直到app_rdy被激活。

- app_rd_data: output信号

当前读取到的数据,与app_rd_data_valid同步。

- app_rd_data_end: output信号

此高电平有效输出指示当前时钟周期是app_rd_data[]上输出数据的最后一个周期。仅当app_rd_data_valid为激活高电平时有效。实际应用过程中,通常不用这个信号。

- app_rd_data_valid: output信号

高电平表示当前的app_rd_data数据有效。

- app_wdf_data: input信号

当前将要写入的数据。这提供了写命令的数据。

- app_wdf_end: input信号

此高电平有效输入指示当前时钟周期是app_wdf_data上输入数据的最后一个周期。应用中通常与app_wdf_wren同步。

>>> assign app_wdf_end = app_wdf_wren; - app_wdf_mask: input信号

当前输入数据的掩码,mask为1的位对应的数据将被屏蔽掉。

- app_wdf_rdy: output信号

该输出表明写数据FIFO已准备好接收数据。当app_wdf_rdy = 1’b1和app_wdf_wren = 1’b1时,接受写入数据。

- app_wdf_wren: input信号

高电平表示app_wdf_data数据有效。

- ui_clk: output信号

MIG输出的用户端时钟(注意与2.3节的核心时钟与工作时钟区分)。在4:1模式下是DDR主频的1/4。这个时钟是由MIG生成的,与同频的其他时钟也要做时钟域的隔离。

- ui_clk_sync_rst: output信号

MIG输出的用户端复位信号,高电平复位。

- sys_clk_i: input信号

输入MIG的时钟(注意区分,此处可以在IP核配置)。

- clk_ref_i: input信号

输入MIG的参考时钟,值固定为200MHz。

- sys_rst: input信号

输入MIG的复位信号,低电平有效。

2.MIG IP接口时序

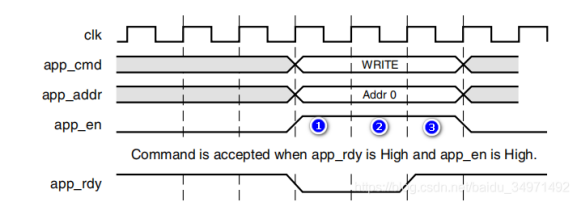

🔊写入addr与cmd:

如上图所示①,②,③情况,只有在③时刻app_en和app_rdy同时为高电平app_cmd(命令)和(app_addr)地址才有效,所以当需要app_cmd,app_addr有效时app_en必须保持到app_rdy为高电平才有效。

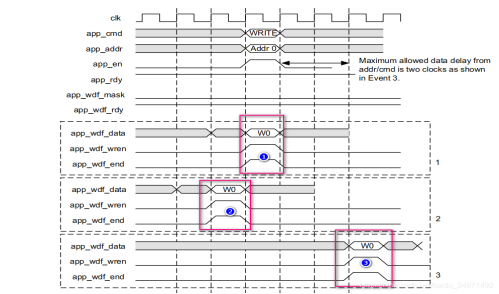

🔊 写时序:

- 如上图所示①,②,③种情况,写命令和写数据直接存在三种逻辑关系。

- 表示写命令(app_cmd),写当前地址(app_addr)和写数据(app_wdf_data)以及写控制信号(app_en,app_rdy,app_wdf_rdy,app_wdf_wren,app_wdf_end)同时有效。推荐采用这种时序。

- 表示写数据(app_wdf_data)和写控制信号(app_wdf_wren,app_wdf_end)先于写命令(app_cmd)和写当前地址(app_addr)以及其他写控制信号(app_en,app_rdy,app_wdf_rdy)一个用户时钟(ui_clk)。

- 表示写数据(app_wdf_data)和写控制信号(app_wdf_wren,app_wdf_end)迟于写命令(app_cmd)和写当前地址(app_addr)以及其他写控制信号(app_en,app_rdy,app_wdf_rdy)。最多两个用户时钟(ui_clk)。

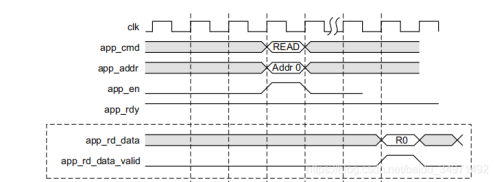

🔊 读时序:

如上图所示,当读命令(app_cmd)和当前读地址(app_addr)以及读控制信号(app_en,app_rdy)同时有效时,等待读数据有效信号(app_rd_data_valid)有效时读数据(app_rd_data)有效。

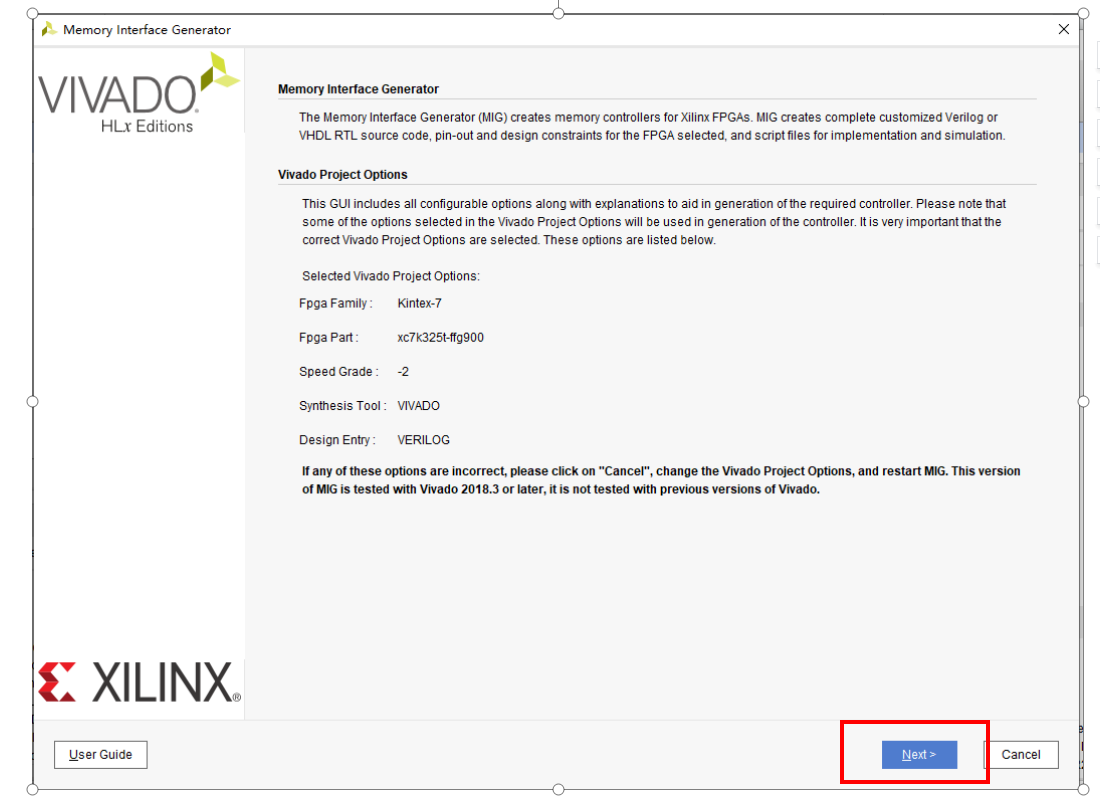

3.MIG IP配置

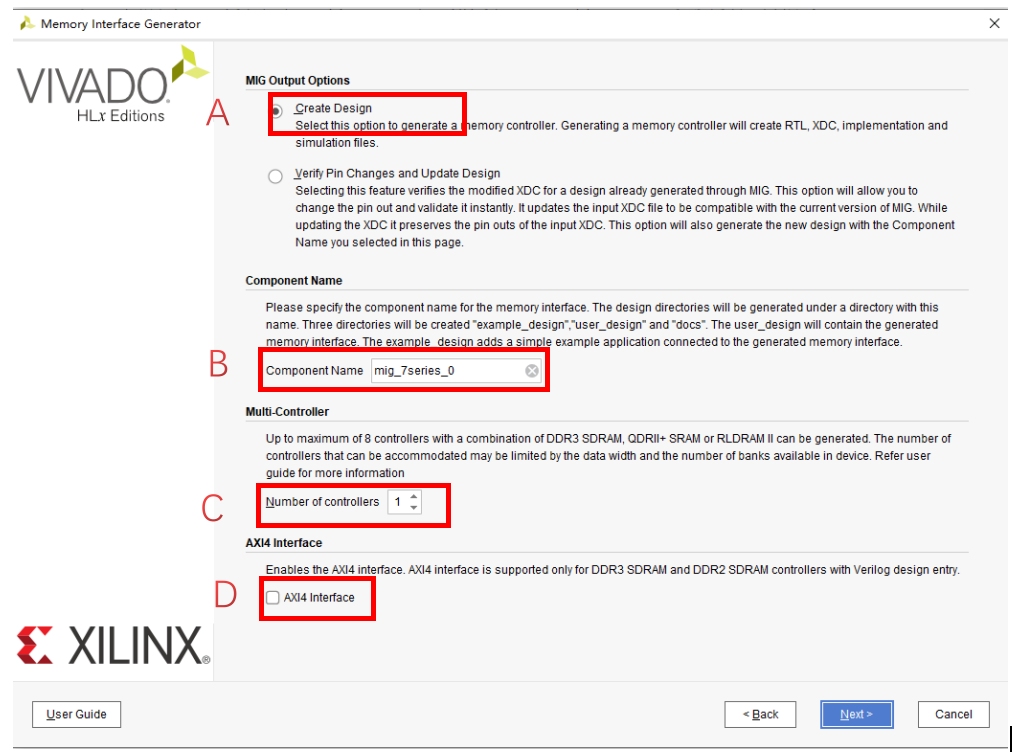

- 在 IP Catalog 中搜索 Memory Interface Generator,双击打开出现以下页面,点击 Next ,出现 MIG Output Options 。

- A 创建设计以创建新的内存控制器设计;

B “Component Name field”一栏中输入IP核组件名称;

C 选择要生成的控制器数量;

D DDR2和DDR3 SDRAM设计支持内存映射的AXI4接口。 AXI4接口仅支持Verilog语言。 如果需要AXI4接口,请在调用MIG工具之前在Vivado Design Suite中将语言选择为“ Verilog”。 如果未选择AXI4界面,则用户界面(UI)是主要界面。

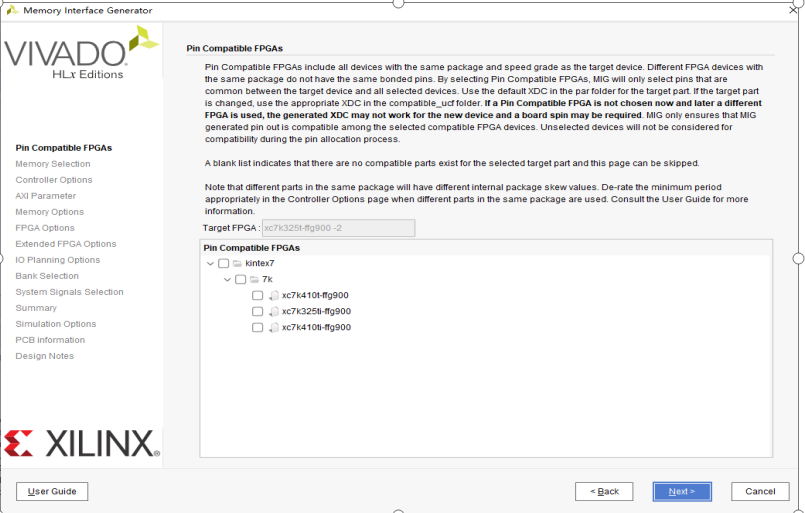

- 引脚兼容的FPGA页面列出了所选系列中具有相同封装的FPGA。 如果从MIG工具生成的引脚需要与其他任何FPGA兼容,则应使用此选项来选择必须与引脚兼容的FPGA。

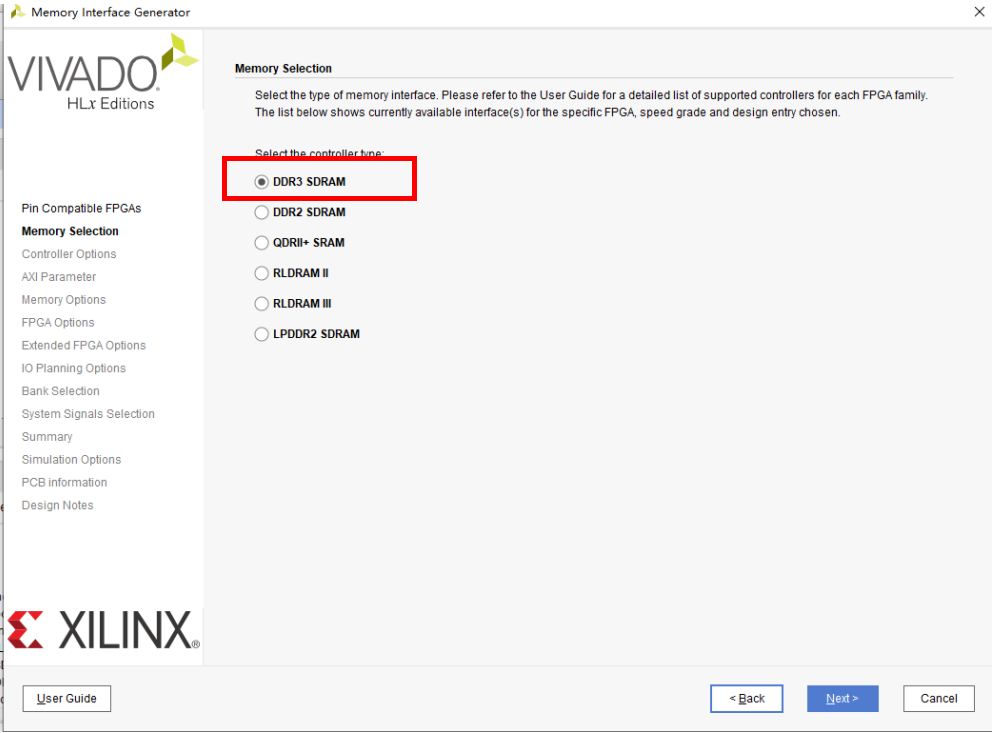

4.此页面显示所选FPGA系列支持的所有存储器类型。选择DDR3 SDRAM控制器类型,单击下一步以显示“控制器选项”页面。7系列的MIG IP核最多支持DDR3,KU系列及性能更高的芯片支持DDR4。

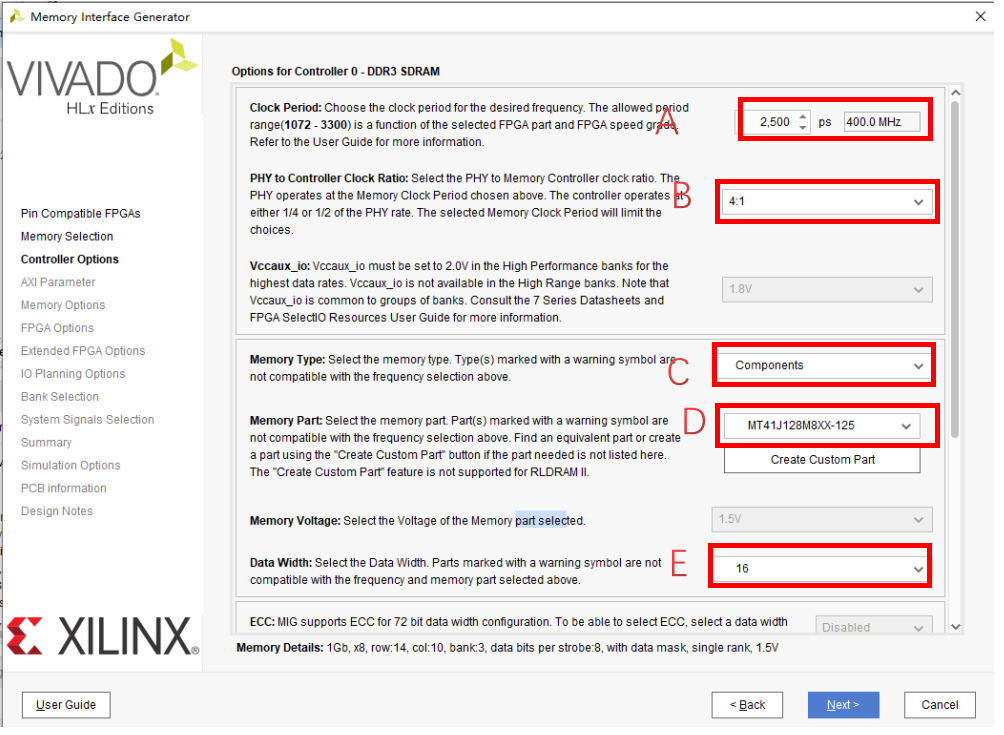

5.此页面显示了可以选择的各种控制器选项。

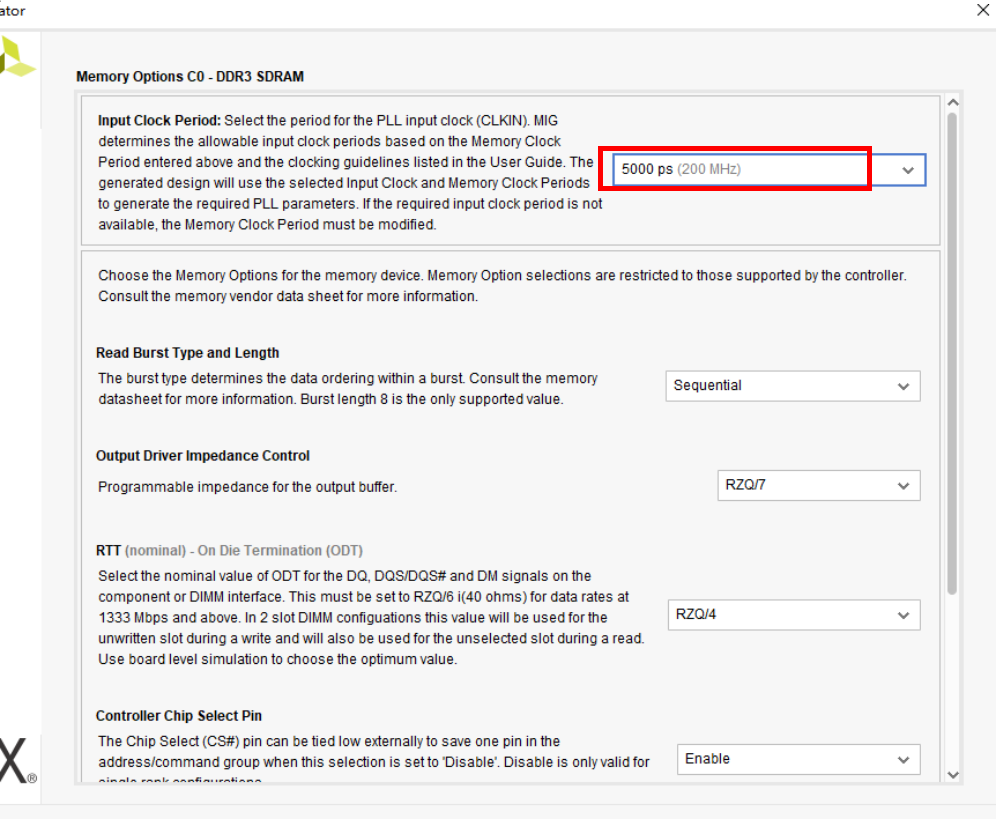

- A.时钟周期,频率范围受所选FPGA和器件速度等级等因素的限制。这里配置为400MHz是DDR3物理引脚的工作频率,即IO缓冲器的工作频率,这里配置为400MHz。

- B.PHY与控制器时钟比率–此功能确定物理层(存储器)时钟频率与用户界面时钟频率的比率,例如选择4:1,工作频率为400MHz,那么用户时钟ui_clk为100MHz。由于FPGA逻辑时序的限制,2:1的比率降低了最大存储器接口频率。2:1比例的用户界面数据总线宽度是物理内存接口宽度的四倍,而4:1比例的总线宽度是物理内存接口宽度的八倍(若设置工作频率为400MHz,因为DDR,所以等效于每一个800MHz周期需要16bit数据,此处设置为2:1,则用户时钟ui_clk为200MHz,那么一个200M周期在时间上等于4个800M周期,由此一个用户时钟周期应提供4倍的16bit数据才能做到匹配,同理,设置为4:1时,那么用户数据应该是8倍的16bit)。2:1的比例具有较低的延迟。4:1的比率对于获得最高数据速率是必要的。通常配做4:1。

- C.此功能选择设计中使用的内存部分的类型。使用默认

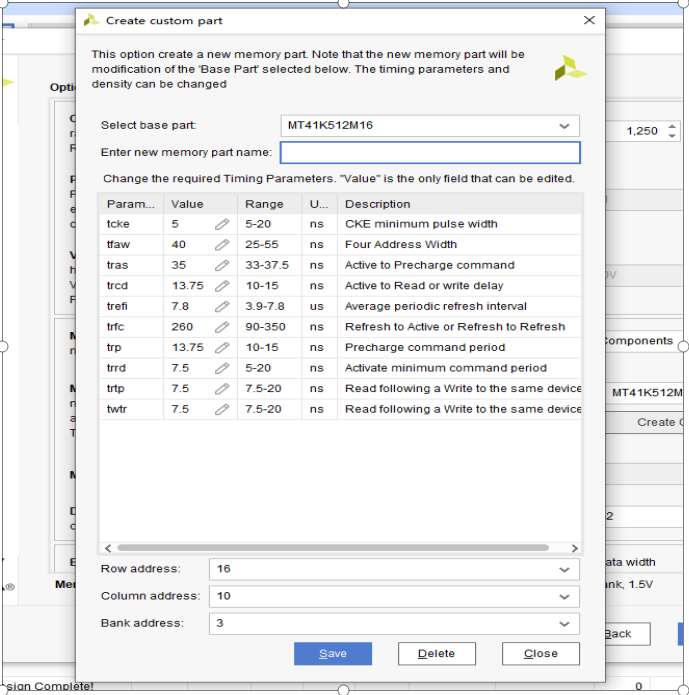

- D.选择器件具体型号数据宽度–可以根据之前选择的存储类型在此处选择数据宽度值。 该列表显示了所选part的所有支持的数据宽度。如果列表中并没有自己的芯片类型,可以选择相似的(指容量、位宽一致),也可以点击下面的creat custom port设置自定义的型号。注意,应在select base part中选择与实际芯片位宽大小一样的已有的型号作为基础,修改以下时序参数(DDR datasheet中提供)以及实际的行列线宽,以及bank位宽,生成自定义的型号。

- E.数据宽度–可以根据之前选择的存储类型在此处选择数据宽度值。 该列表显示了所选part的所有支持的数据宽度。如果只有一颗DDR3,则此处的值应等于颗粒的物理位宽。不由的想,如果有两颗DDR3,如何做呢?请关注后续文章。

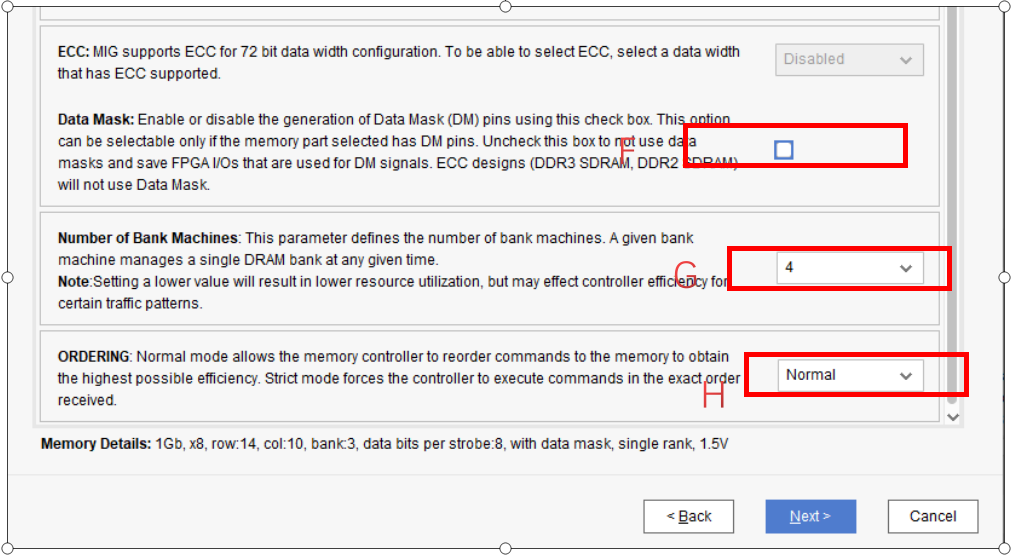

- F.Data mask 视需要而定,是用来屏蔽数据总线上的数据的。

- G.Bank Machines数量–列表显示所选设计配置支持的Bank Machines数量。一般设置为4。

- H.排序–正常模式允许内存控制器将命令重新排序到内存,以获得最高的效率。 严格模式强制控制器以接收到的确切顺序执行命令。一般设置为Normal。

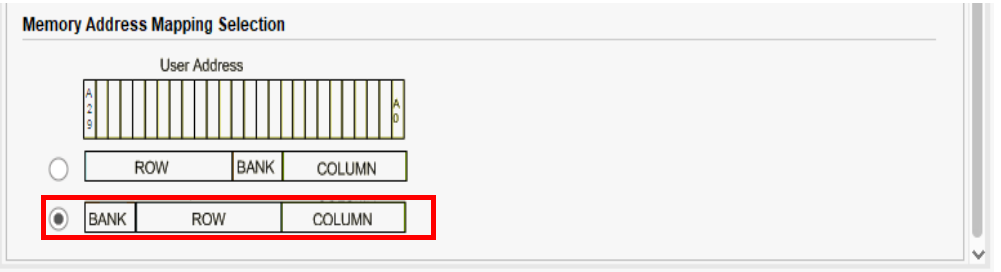

6.除第一个设置输入IP的时钟为200MHz之外(此处设置的是sys_clk_i),其余保持默认。该功能允许选择各种有关存储模式的寄存器值。在初始化期间,将模式寄存器的值加载到加载模式寄存器中。内存地址映射的选择选择红色框中内容。

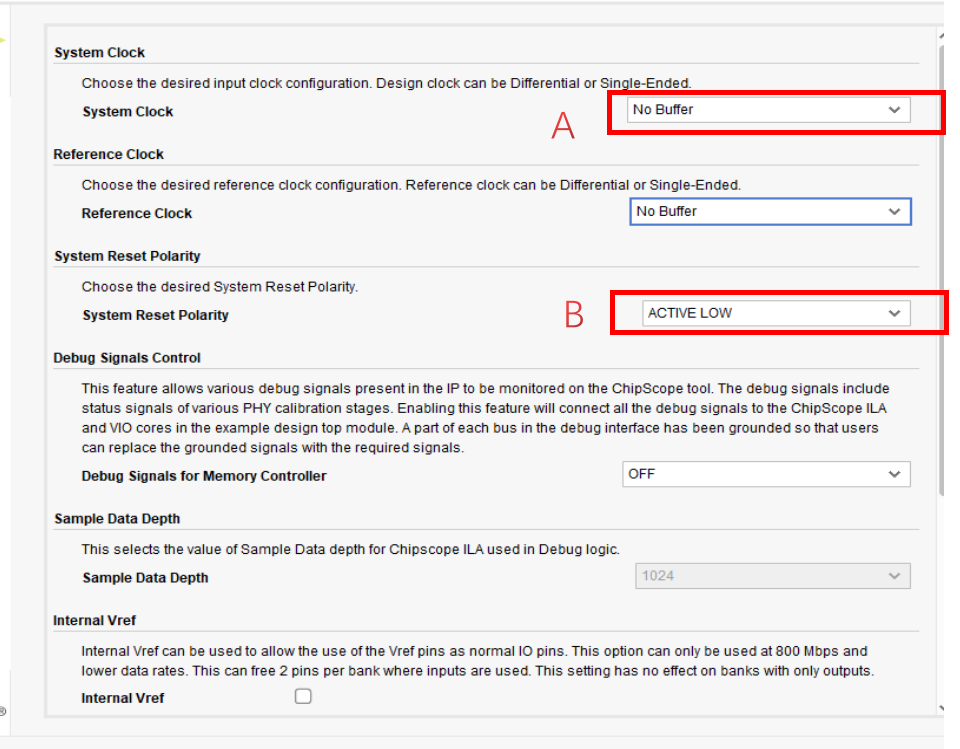

7.除了这两个选择无缓冲区外,其余保持默认。

- A 系统时钟–此选项为sys_clk信号对选择时钟类型(单端,差分或无缓冲区)。 选择“无缓冲区”选项时,不会在RTL代码中实例化IBUF原语,并且不会为系统时钟分配引脚。如果在没有执行更改的情况下实现了从MIG为No Buffer选项生成的设计,则设计可能会由于未针对sys_clk_i信号实例化的IBUF而无法实现。 因此,对于无缓冲区方案,需要将sys_clk_i信号连接到内部时钟。

- B 系统复位电平–可以选择系统复位的电平(sys_rst)。 如果将选项选择为active-Low,则参数RST_ACT_LOW设置为1;如果设置为active-High,则参数RST_ACT_LOW设置为0。

降低I/O功耗–该选项通过在控制器处于空闲状态时自动禁用DQ和DQS IBUF来降低平均I/O功耗。

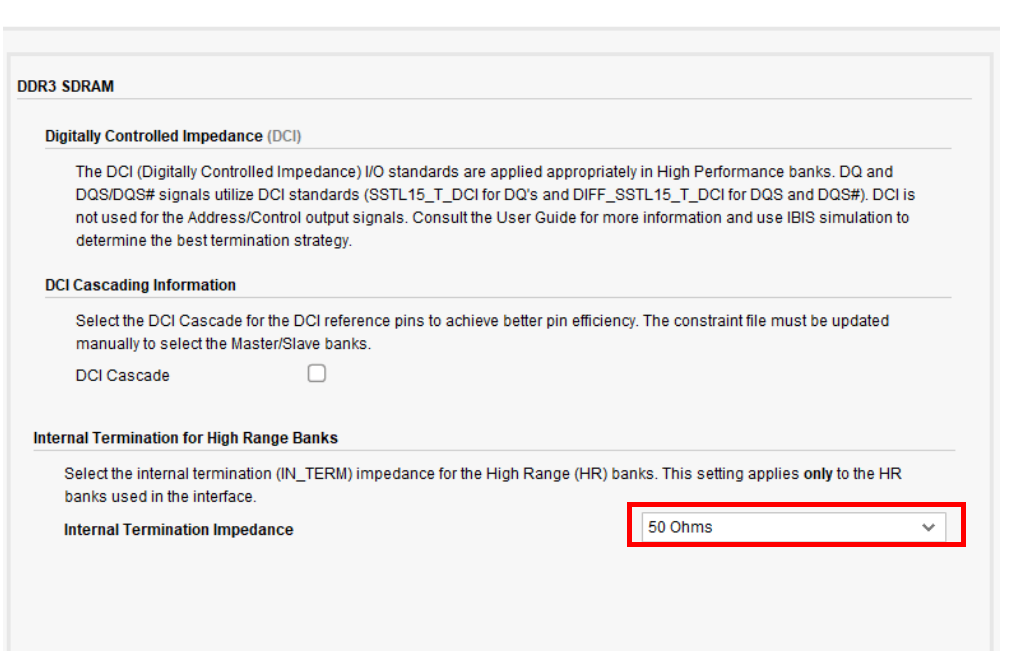

8.HR Bank的内部终端匹配电阻–内部终端选项可以设置为40、50或60Ω或禁用。 此选择仅适用于HR Bank。通常设置为50即可。

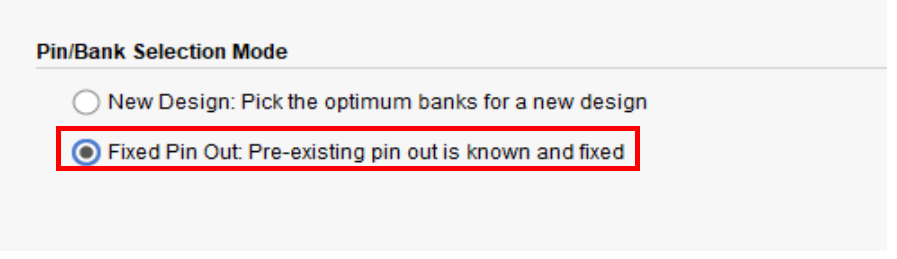

9.引脚模式选择第二个,之后导入UCF文件,进行引脚约束配置。

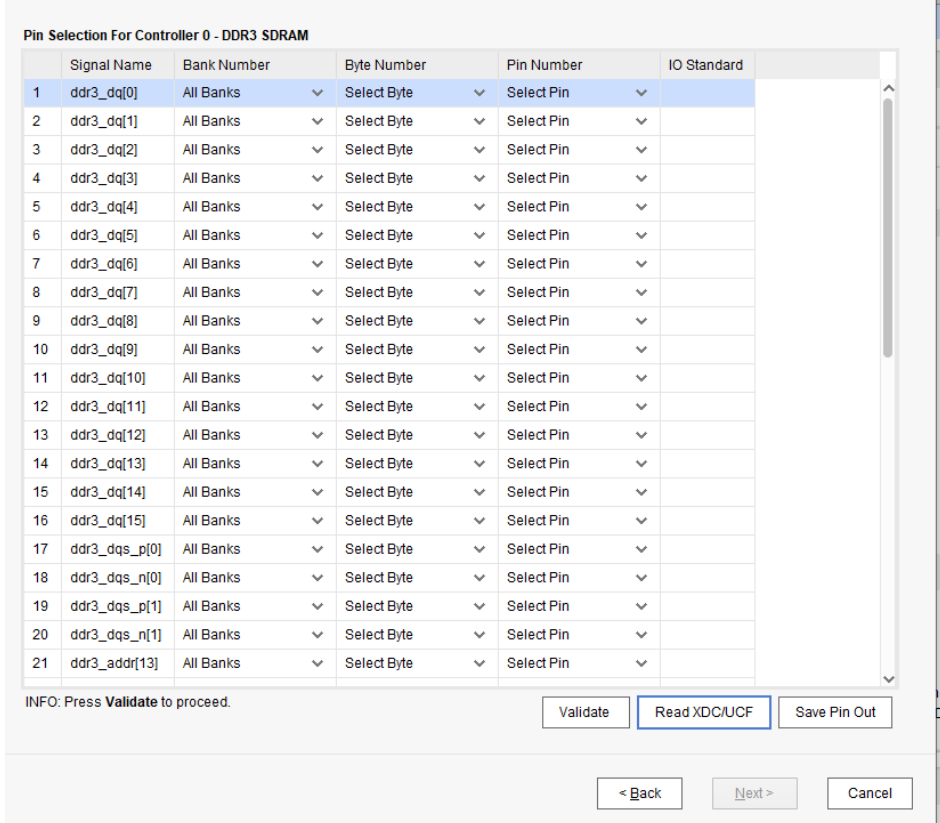

10.开始一个个的输入DDR3信号对应的管脚,如果事先写好了管脚约束文件,也可以直接载入。填写完成后,点击“Validate”检查,看写的是否有误。

其余的点next即可。

注:MIG输入一个200MHz的时钟sys_clk_i,再输入一个200MHz的参考时钟clk_ref_i。倍频出来DDR3的工作时钟400MHz(工作时钟,IO驱动时钟),分频出来一个100MHz的用户时钟ui_clk。加之前面的工作时钟,核心时钟,都务必分清楚。

4.传送门

| END |

🔈文章原创,首发于CSDN论坛。

🔈欢迎点赞❤❤收藏⭐⭐打赏💴💴!

🔈欢迎评论区或私信指出错误❌,提出宝贵意见或疑问❓。

3万+

3万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?