一步一步来搭建一下AXI GPIO

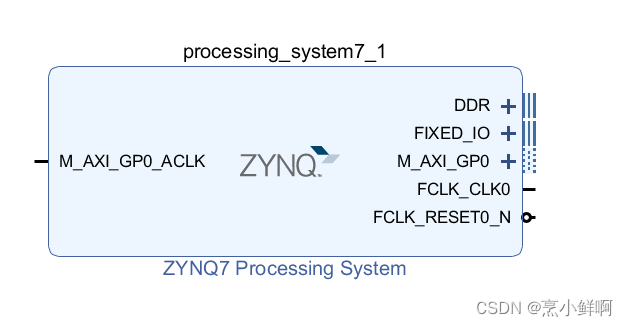

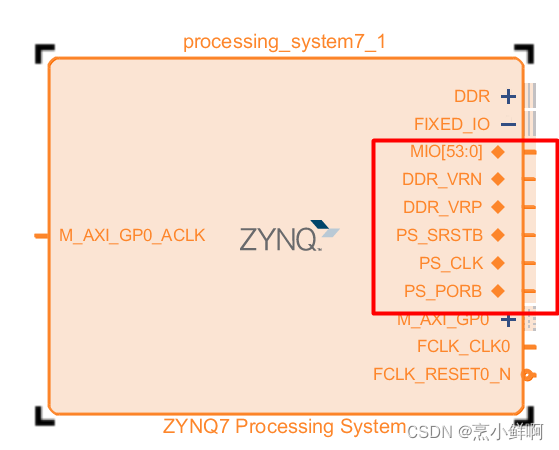

创建ZYNQ 后先来看下各个接口的含义

1.M_AXI_GP0_ACKL和M_AXI_GP0

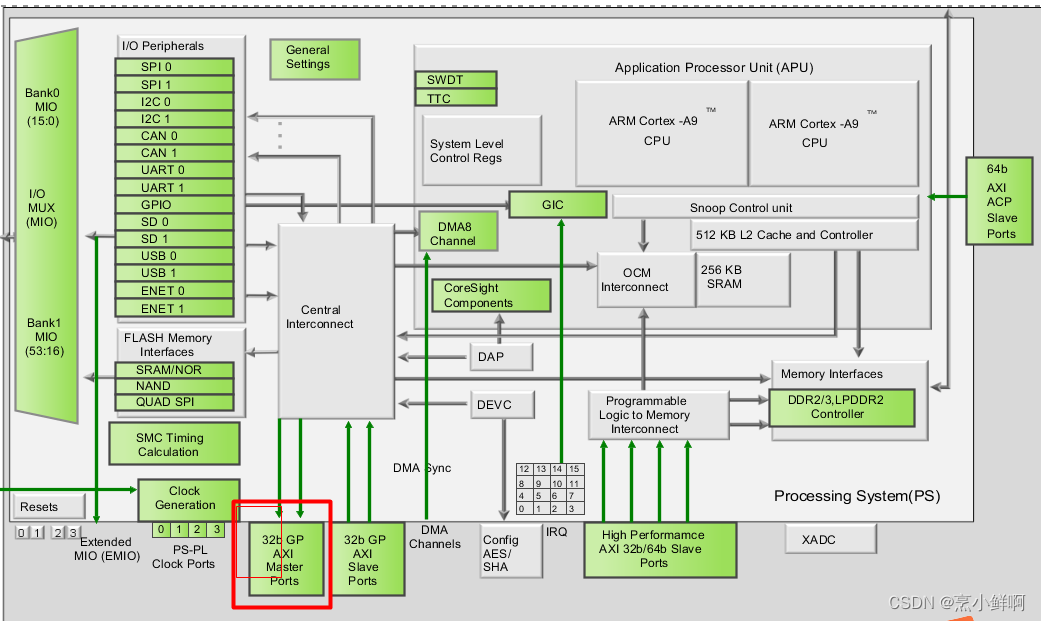

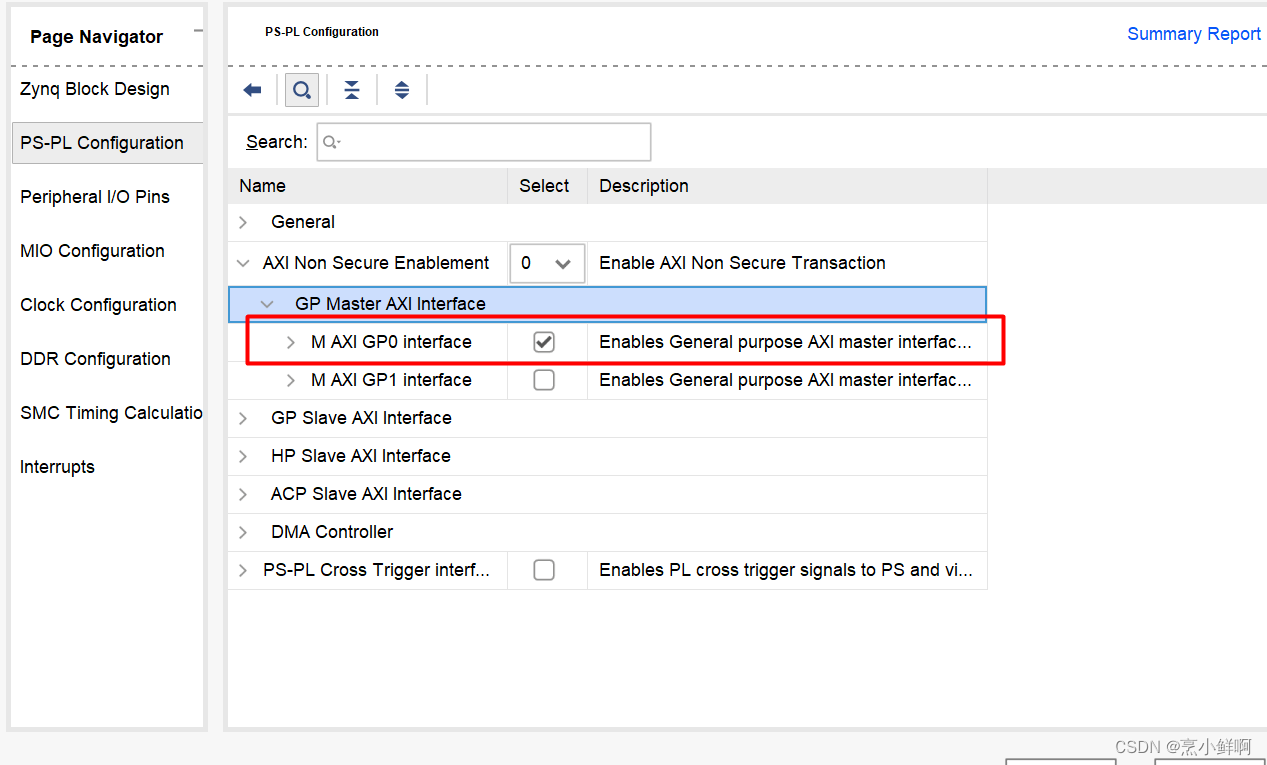

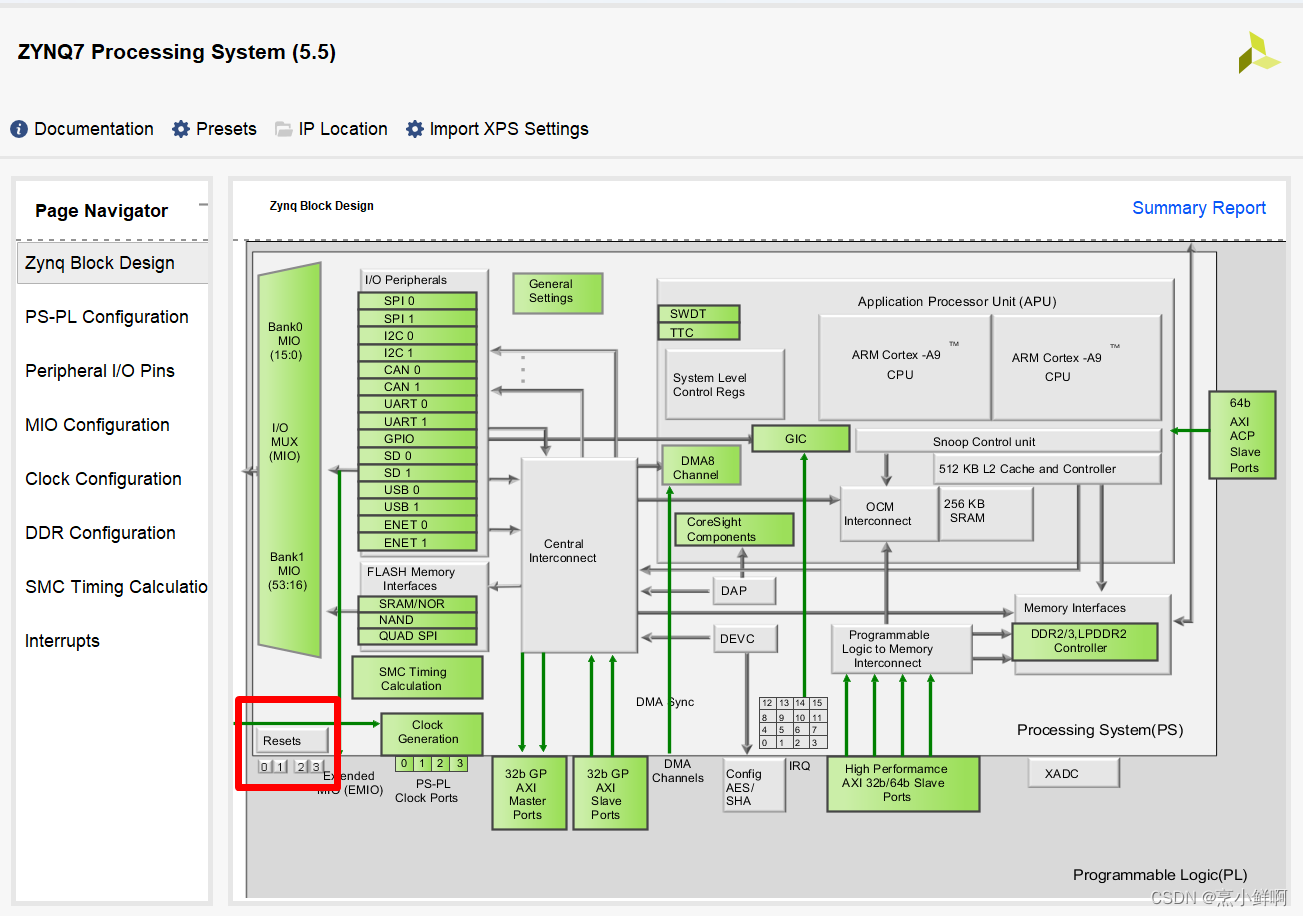

ZYNQ的PS部分是有一个GP接口,32 Bit 的AXI master接口,默认是打开的,如果双击绿框可以看到是打开的

M_AXI_GP0 就是AXI的主机接口,M_AXI_GP0_ACKL是主机接口的时钟。

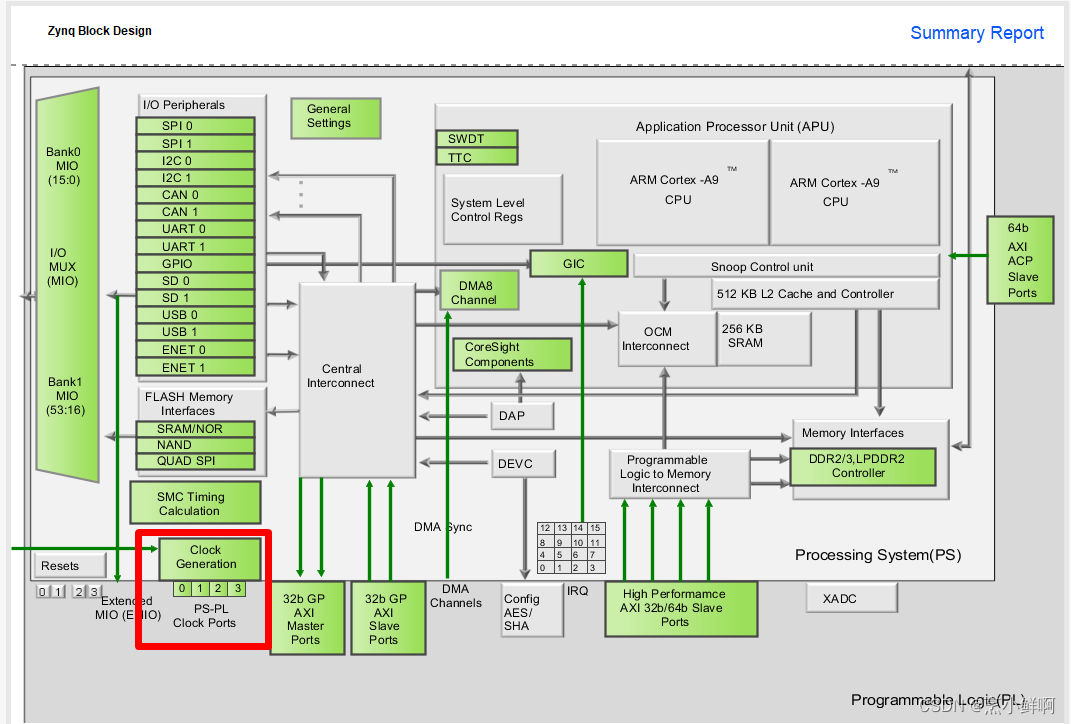

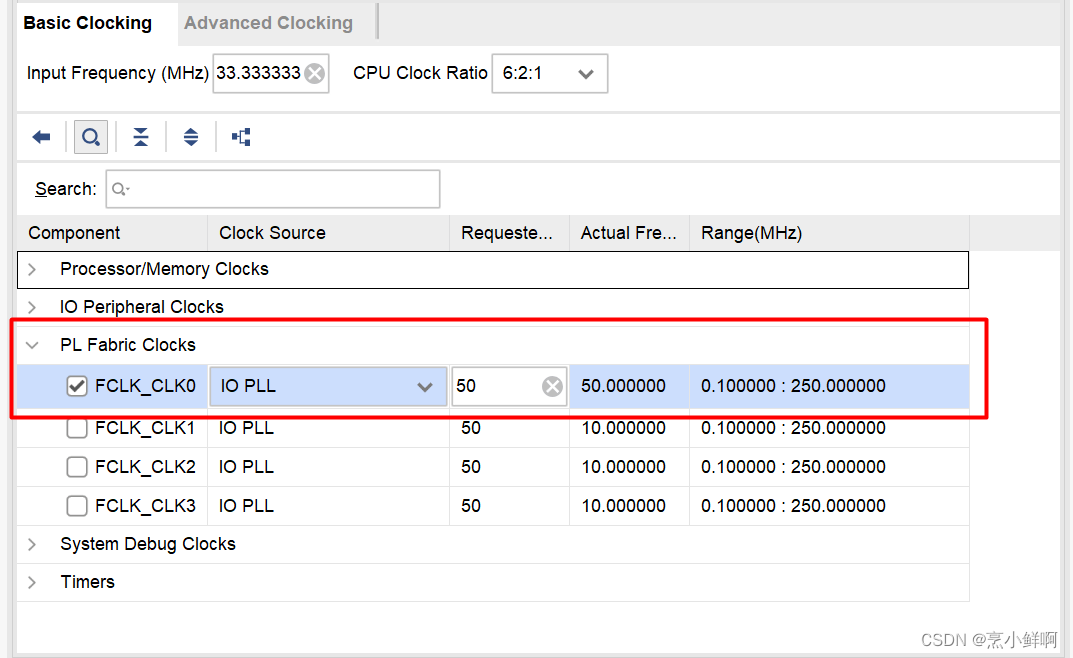

2.FCLK_CLK0

这个信号在上图中可以看到,PS-PL有4路时钟,点击绿框跳转到PS-PL时钟设置界面。

FCLK_CLK0 就是PS-PL时钟信号。

3.FCLK_RESET0_N

PS-PL 处理时钟还有4路复位信号

4.FIXED IO

固定的IO,这里说的是ZYNQ PS最小系统就有的IO。比如说MIO,DDR,PS复位,PS时钟等。这些是固定都有的

只要有PS系统这几个就跑不了。

到这里基本的信号了解完毕。

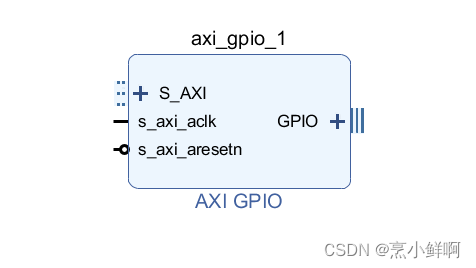

二.AXI GPIO

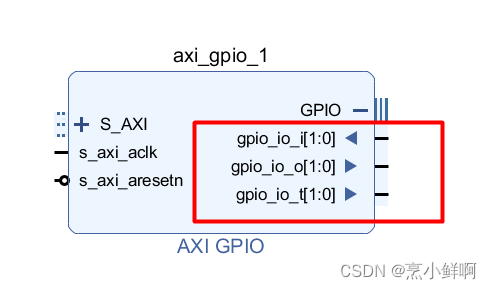

先上一个AXI GPIO IP

从接口,时钟,复位 和GPIO。GPIO说的是引脚

可以设置引脚的个数和方向,输入输出和高组态。

2.1 连接

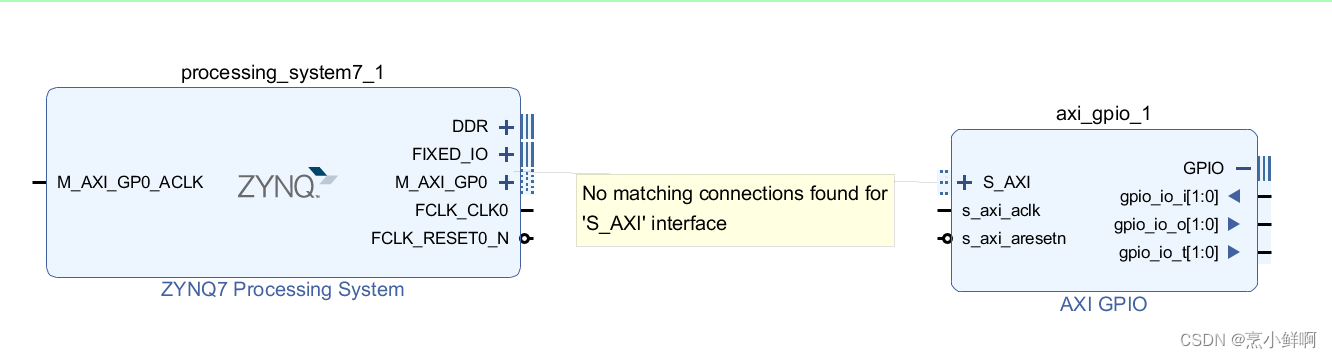

如果尝试的吧AXI GPIO 从接口和ZYNQ的主接口连接的时候,ViVado会提示无法连接。

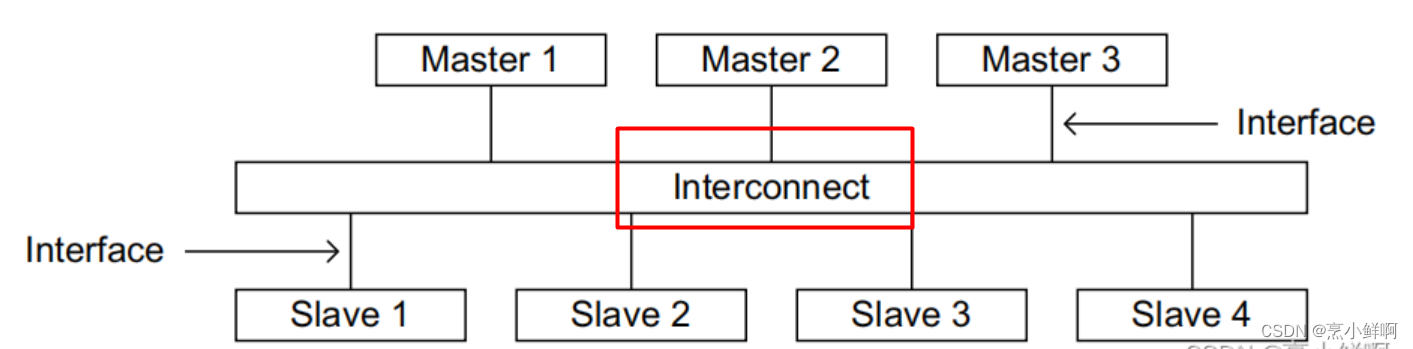

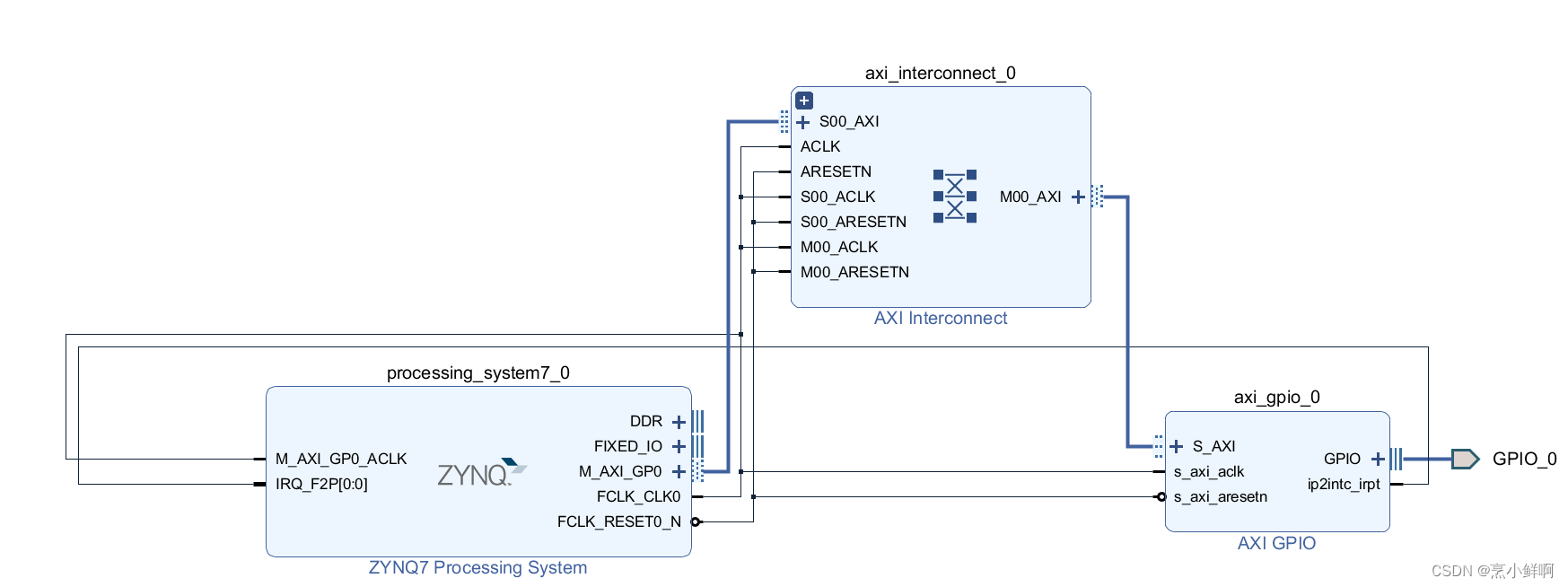

AXI 接口的互联是需要一个叫做Interconnect的结构,也是一个IP核。很好,我们就创建出来,然后按照主从配对连接。

接下来就是把复位连接在一起,就接到PS-PL的复位信号上,时钟都接到PS-PL时钟上来。

整个系统就连接完成了,这个时候我们去校验链接会提示加入system reset的IP.

这里我们不考虑同步复位的问题。直接忽略问题。

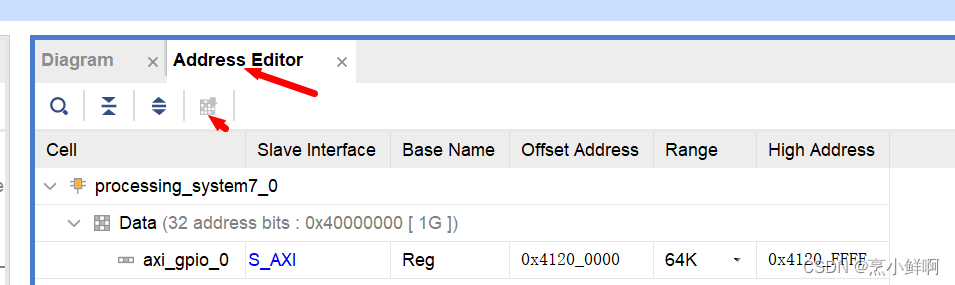

然后进行地址分配,AXI是地址到地址的通讯。

注意0x4120_0000这个地址。

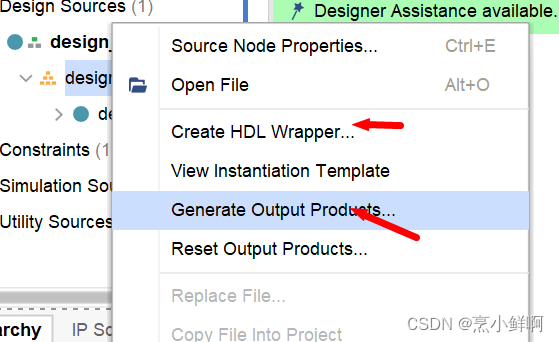

然后进行常规操作

然后进行综合,IO引脚分配。完事后导入到SDK。

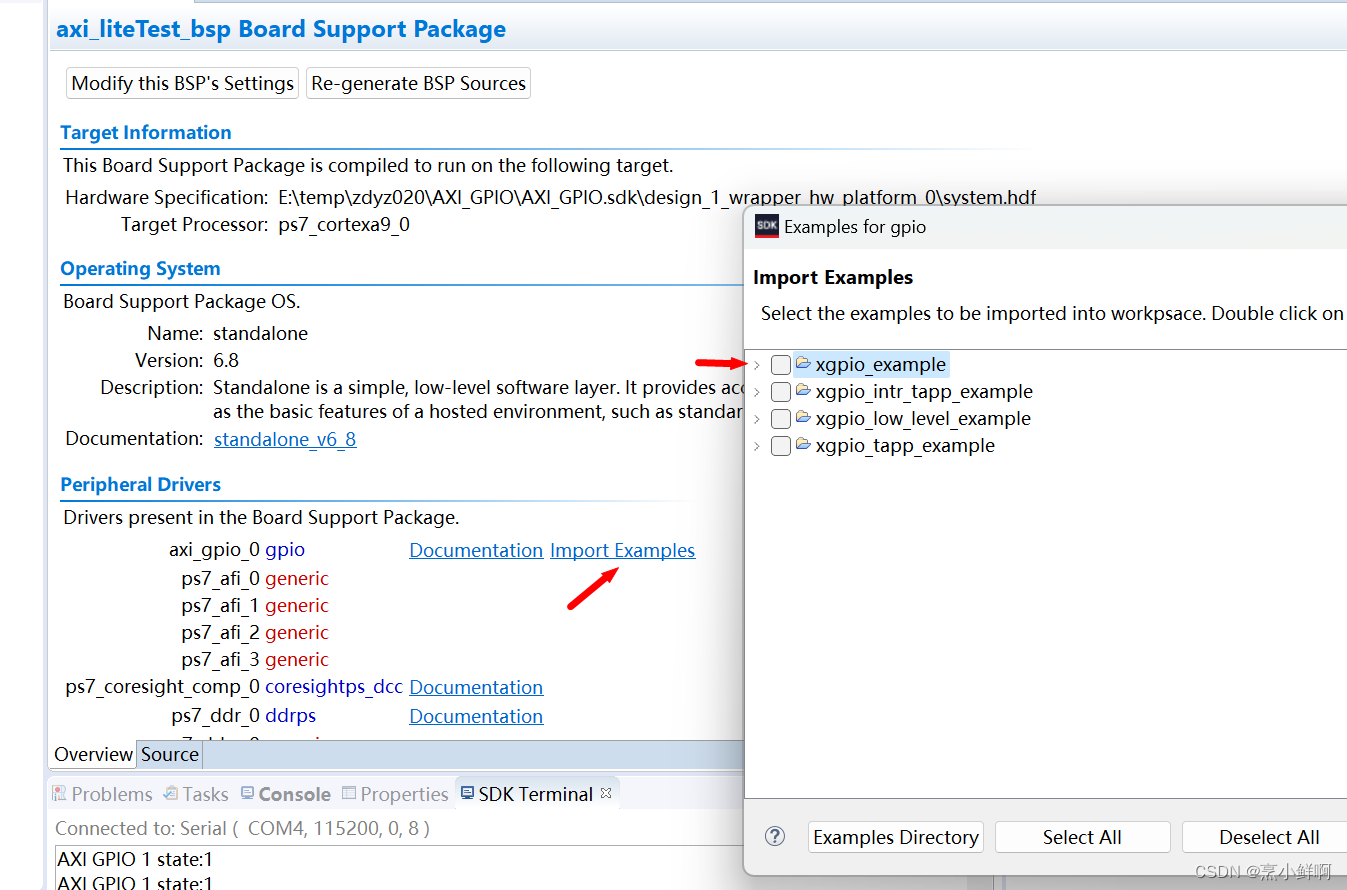

导入官方的例程。

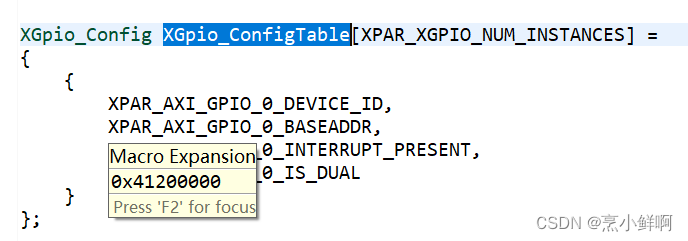

找到初始化GPIO的地方,看到这个地址很熟悉。

OK,到这里就完成了。

477

477

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?