触发器

触发器

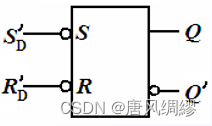

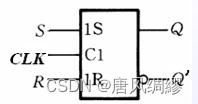

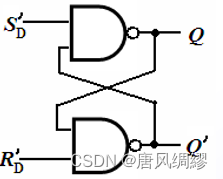

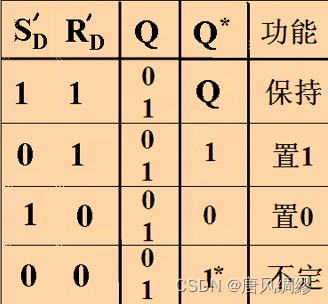

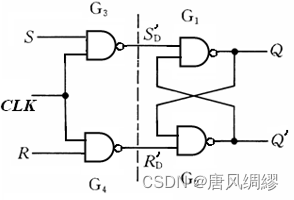

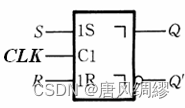

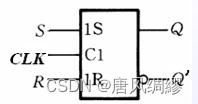

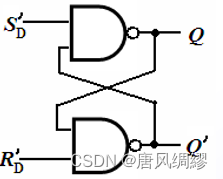

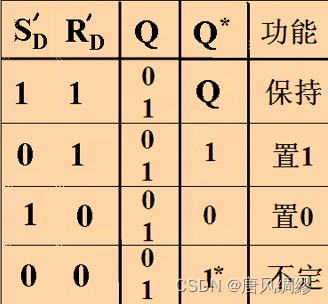

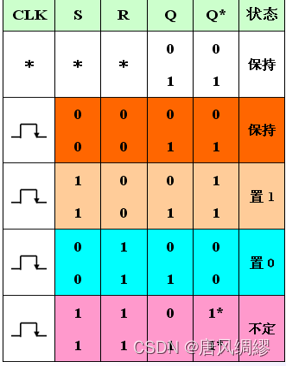

SR锁存器  SR触发器

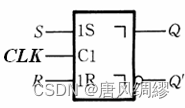

SR触发器

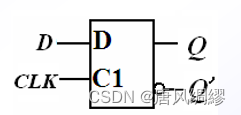

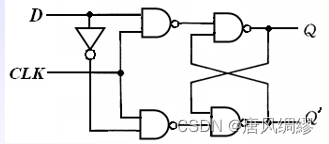

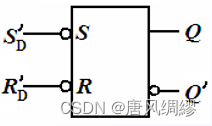

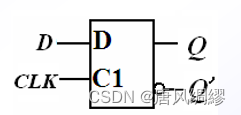

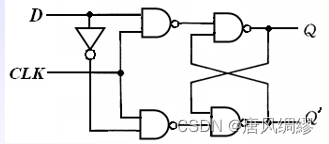

D触发器

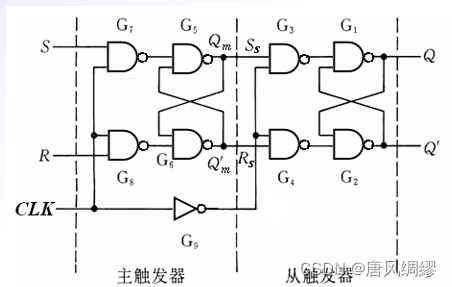

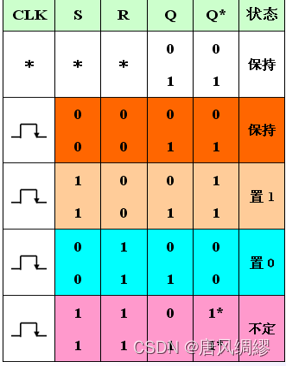

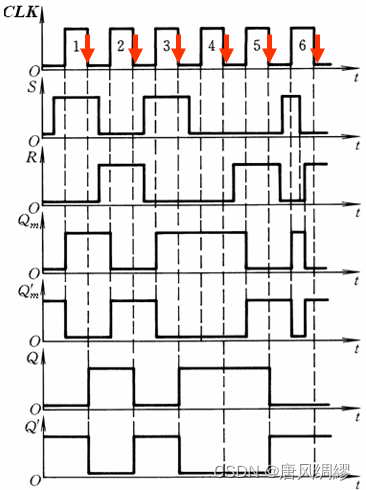

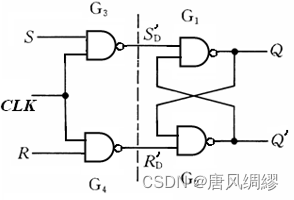

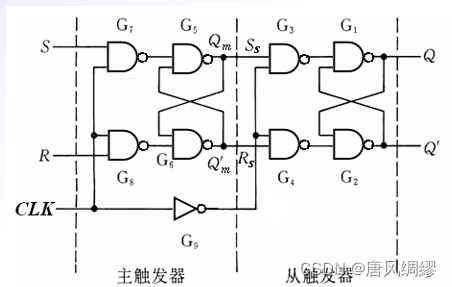

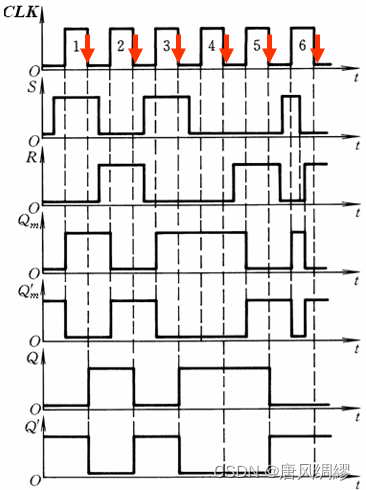

脉冲触发器(主从触发器)CLK回到低电平后输出状态才改变,每个CLK周期里主触发器的输出(次态)的状态只能改变一次。

主从SR:

触发器

触发器

SR锁存器  SR触发器

SR触发器

D触发器

脉冲触发器(主从触发器)CLK回到低电平后输出状态才改变,每个CLK周期里主触发器的输出(次态)的状态只能改变一次。

主从SR:

6606

6606

4515

4515

2416

2416

4013

4013

4865

4865

1万+

1万+

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?