本文图片整理自西安交通大学软件学院张斌老师的ppt,仅供学习使用,请勿转载

本文是我在数电期末考试前整理的个人复习资料,内容不全面,后面缺少了时序电路的设计(考试中会出大题),请对照ppt复习该部分

虽然张老师上课时候听不进去,但是考试时候还是比较简单的,我记得我们的设计题是设计4位加法器和一个序列转换器,好像是0000->1111的,而且触发器只用到了DFF,复习时可以以他的ppt为主,实在搞不懂的跳过就行了,他考的应该也不会非常难(或许吧)

数制和编码

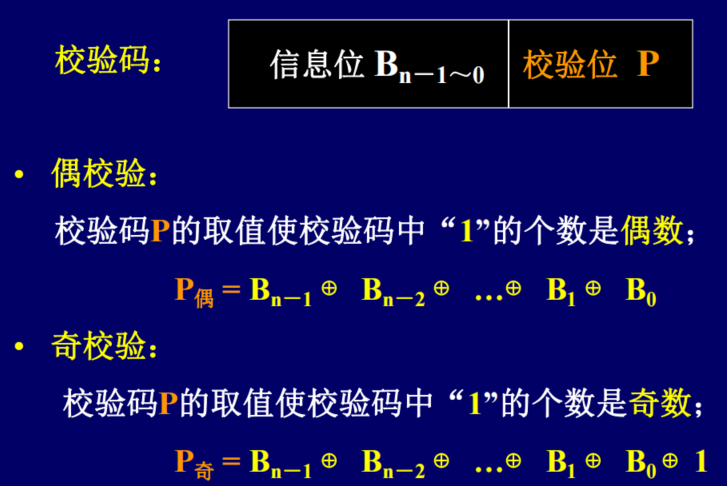

奇偶校验码

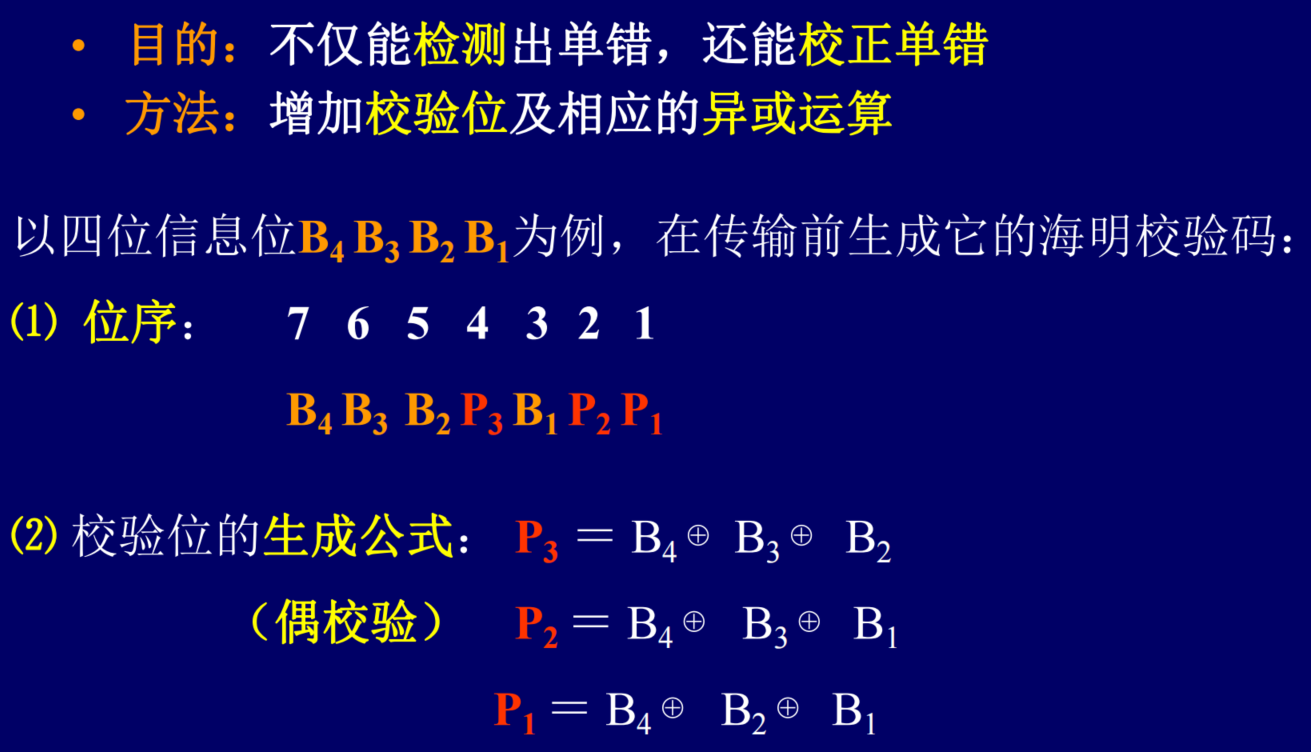

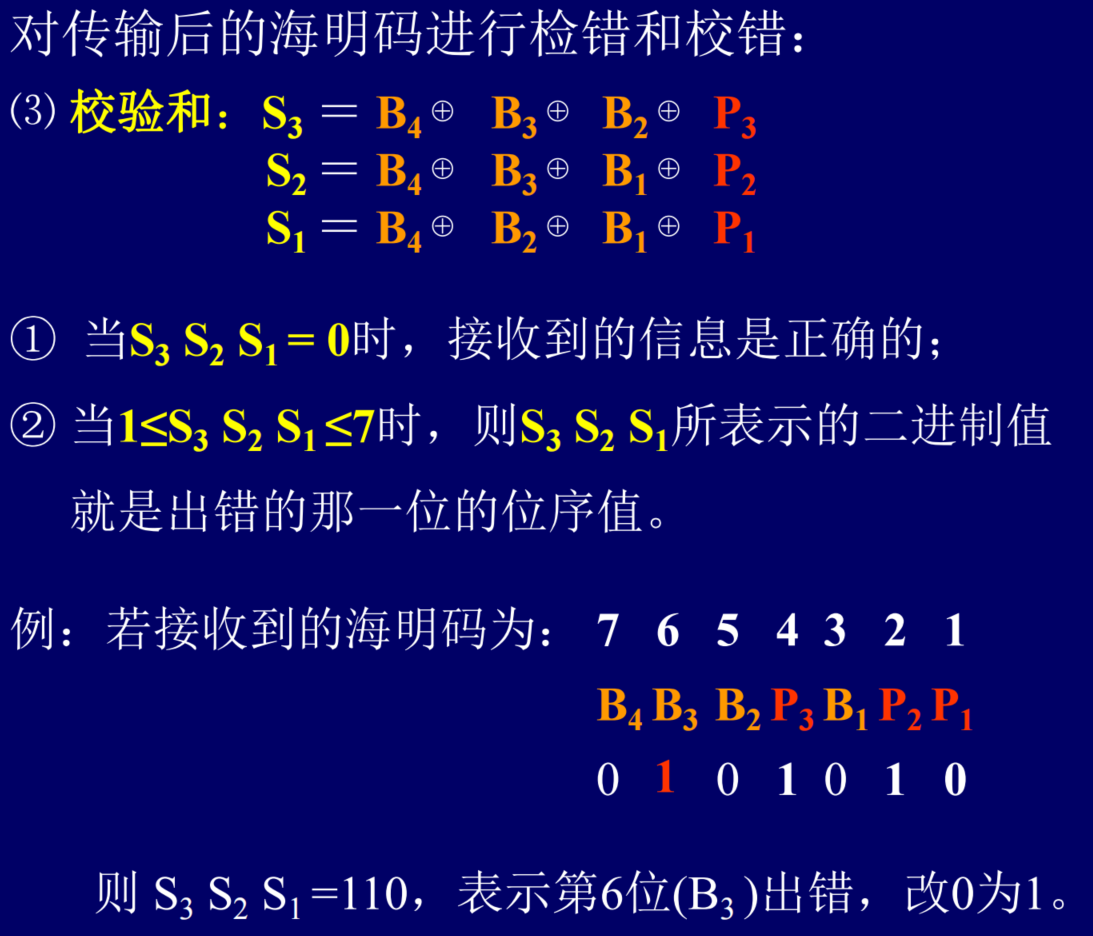

海明校验码

组合逻辑电路

组合逻辑电路的特点:电路输出仅取决于当时的输入, 而与过去的输入情况无关。

时序逻辑电路的特点:电路输出不仅取决于当时的输入, 而且也与过去的输入情况有关, 即与过去的电路状态有关。

逻辑电路描述文档

应至少包括以下五部分:

- 框图

- 用方框、圆框等粗略表示系统的输入、输出、功能模块(或称子系统),各模块的功能用文字加以说明;

- 用带箭头连线表示模块之间主要信息通路、流向和控制信号。

- 逻辑图

- 将框图的粗略表示,具体地用文字说明器件类型。

- 原理图

- 在逻辑电路图(Logic Diagram)中,详细标明器件类型、端脚之间的连接、信号名等条件细节,再次细化逻 辑电路图。

- 时间图

- 反映逻辑信号之间对应的时间关系,特别是要能反映出关键信号之间因果关系和传输延迟。

- 结构化逻辑描述

- 说明结构化逻辑器件的内部功能,如PLA、存储器芯片或者某些具有专门功能的中、大规模器件;

- 用逻辑等式、状态表(图)、功能表或程序表等形式说明。

- 电路说明

- 用文字简明叙述电路的使用方法; 解释内部的工作方法;

- 列出设计和操作中所有可能的潜在缺陷,以及在使用不当中隐含的问题。

门的符号标准

- 长方形符号:中国国标、IEC标准、IEEE标准

- 变形符号: IEEE标准

引端的有效级

- 引端的有效级: 是指电路的输入、输出上的物理量与电路的内部逻辑状态的对应关系。

- 对应关系:指选用器件的引端的有效级与所给信号的有效级相匹配。

正逻辑约定

逻辑电平对应关系:

-

H (高电平) —— “1”(外部逻辑状态)

-

L (低电平) —— “0”(外部逻辑状态)

负逻辑约定

逻辑电平对应关系:

- H (高电平) —— “0”(外部逻辑状态)

- L (低电平) —— “1”(外部逻辑状态)

组合电路中的竞争与险象

同一信号或同时变化的某些信号,经过不同路径到达某一点时有时差,这种现象称为竞争

险象一定是竞争的结果。对于有错误输出的竞争称之为临界竞争,对于未产生错误输出的竞争称之为非临界竞争。

组合逻辑器件

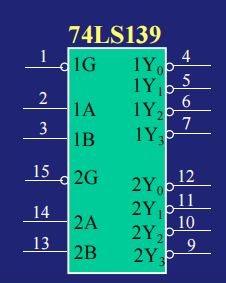

双24译码器74LS139

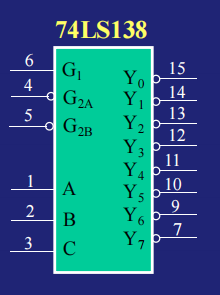

3-8译码器74LS138

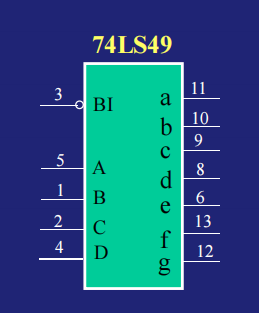

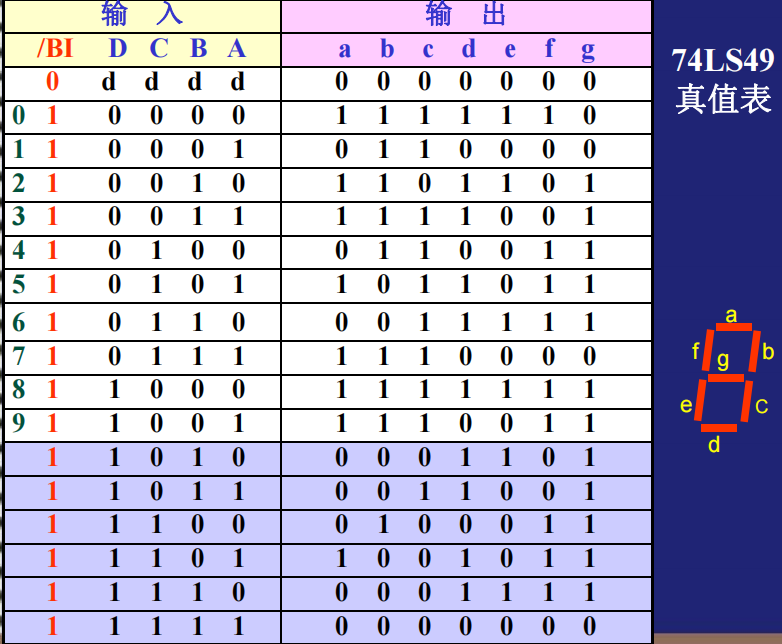

BCD译码器74LS49

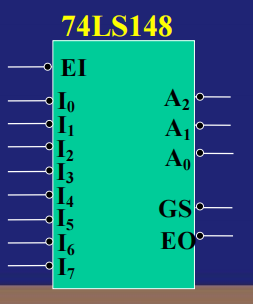

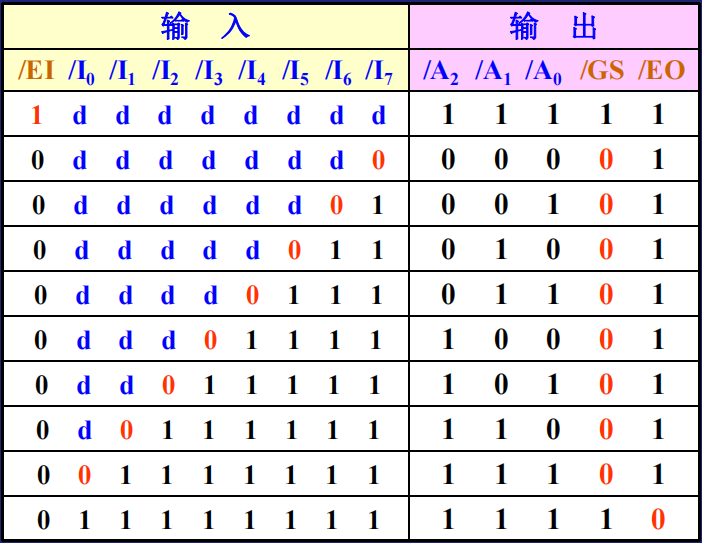

8-3 优先权编码器74LS148

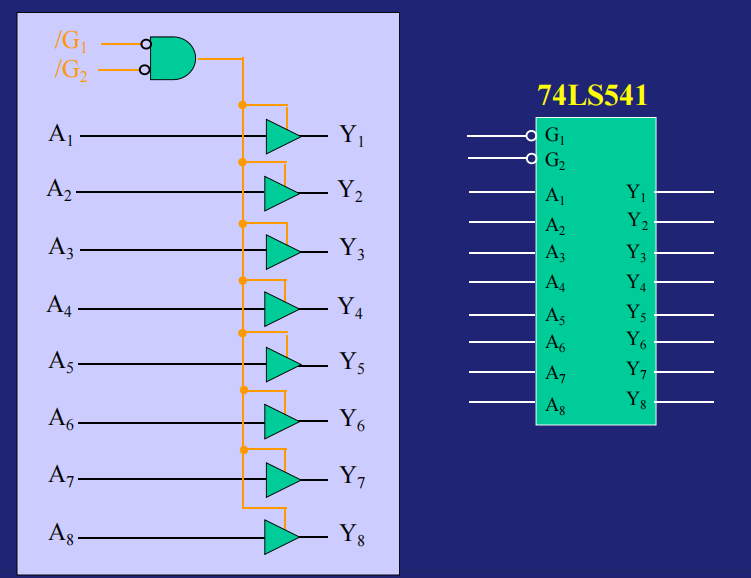

八三态缓冲器74LS541

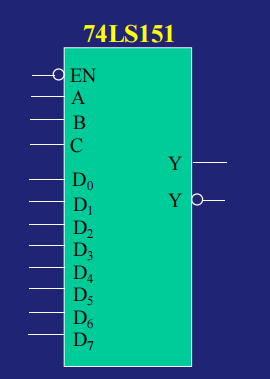

八输入1位输出多路选择器74LS151

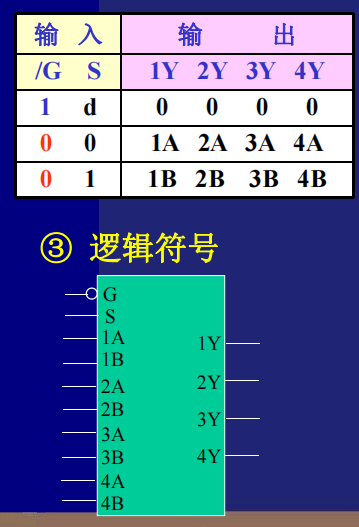

二输入4位多路选择器74LS157

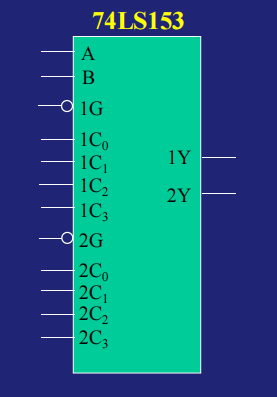

四输入2位多路选择器74LS153

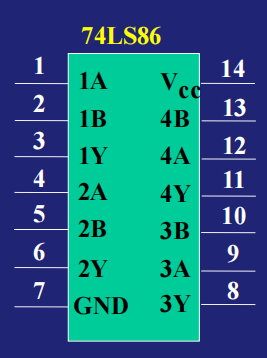

2输入4异或门74LS86

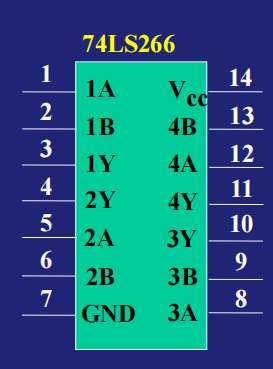

2输入4异或非门74LS266

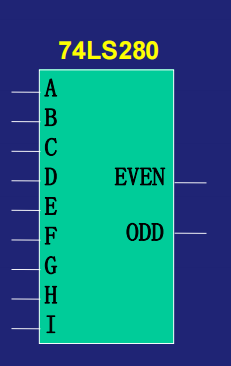

9位奇偶发生器/检验器74LS280

“1”的总个数为奇数的称为奇校验Odd

“1”的总个数为偶数的称为偶校验Even

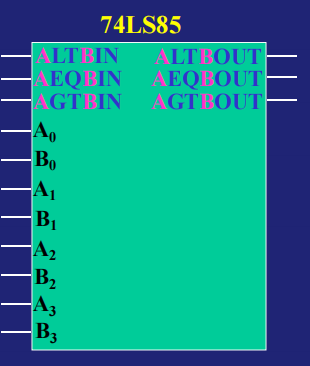

四位比较器74LS85

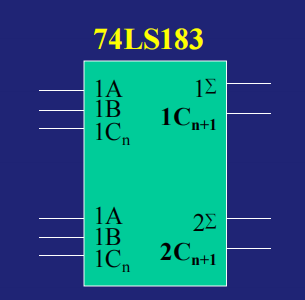

全加器74LS183

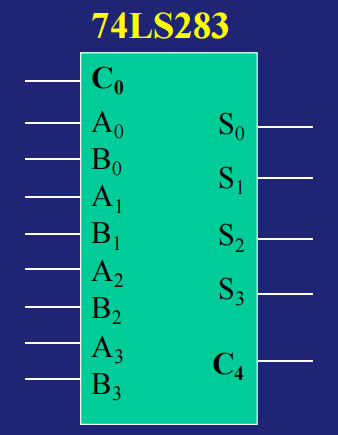

加法器74LS283

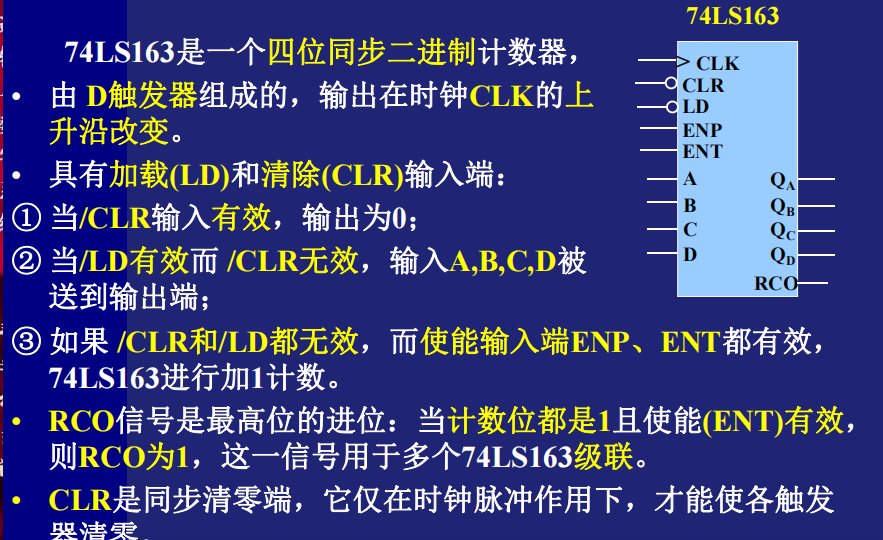

四位同步二进制计数器74LS163

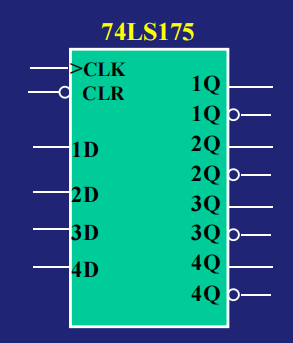

并行寄存器74LS175

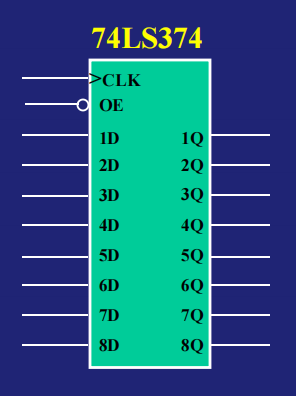

通用八位寄存器74LS374

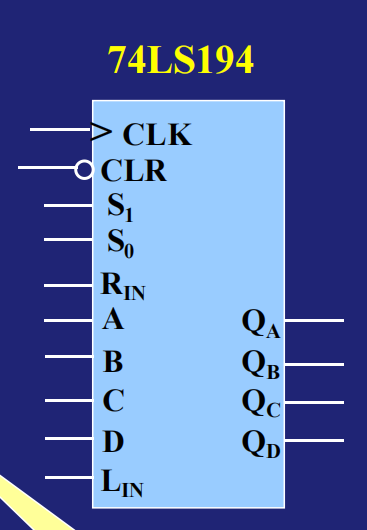

通用寄存器74LS194

同步时序电路的分析

基本概念

数字逻辑电路可分为两大类:

-

组合逻辑电路

-

时序逻辑电路

组合电路是指它的输出仅由当前输入决定。

时序电路是指它的输出不仅取决于当前输入,而且 也取决于过去的输入序列,即过去输入序列不同, 则在同一当前输入的情况下,输出也可能不同。

现态——某一时刻输入变化前的电路状态;

次态——当输入变化后的电路状态(即电路将要进入的状态);

时序电路的分类

1、按照引起状态发生变化的原因可分为:

- 同步时序电路:其状态的改变受同一个时钟脉冲的 控制,且与时钟脉冲同步。即电路在统一时钟控制CLK (或CP)下,同步改变状态。

- 异步时序电路:无统一的时钟脉冲使整个系统的工 作同步,输入直接引起状态改变。

2、按输入信号x的特性可分为:脉冲输入和电平输入。

-

在同步时序电路中,输入信号 x 相对时钟脉冲 CP 的变化速度而言,如果输入信号 x 在两个时钟脉冲之间信号完成 0→1→0 (或 1 →0 →1) 两次变化则为脉冲输入,否则为电平 输入。

-

在异步时序电路中,输入信号x按照电路研究的目的区 分:如果研究的是输入信号 x 完成0 →1→0 (或1 →0 →1)两 次变化对电路的影响,则为脉冲输入,否则为电平输入。

-

脉冲输入:在两个时钟脉冲之间信号完成 0→1→0 (或 1 →0 →1) 两次变化后对电路的影响;

-

电平输入:信号完成 0 →1 (或 1 →0) 一次变化对电 路的影响。

3、按输出特性可分为:Mealy型和Moore型。

双稳态元件

双稳态元件是构成存储电路的基本模块,通常指锁存器或触发器。双稳态元件的特点是:

⑴ 有两个稳定状态,分别表示存储数码 0或1

⑵ 在一定的触发信号作用下**,**它可从一个稳态翻转 到另一个稳态。

锁存器是利用电平控制数据的输入;

触发器是利用脉冲或边沿控制数据的输入。

空翻现象: 指在一个时钟脉冲C的作用下,状态发生了两次或两次以上的翻转。

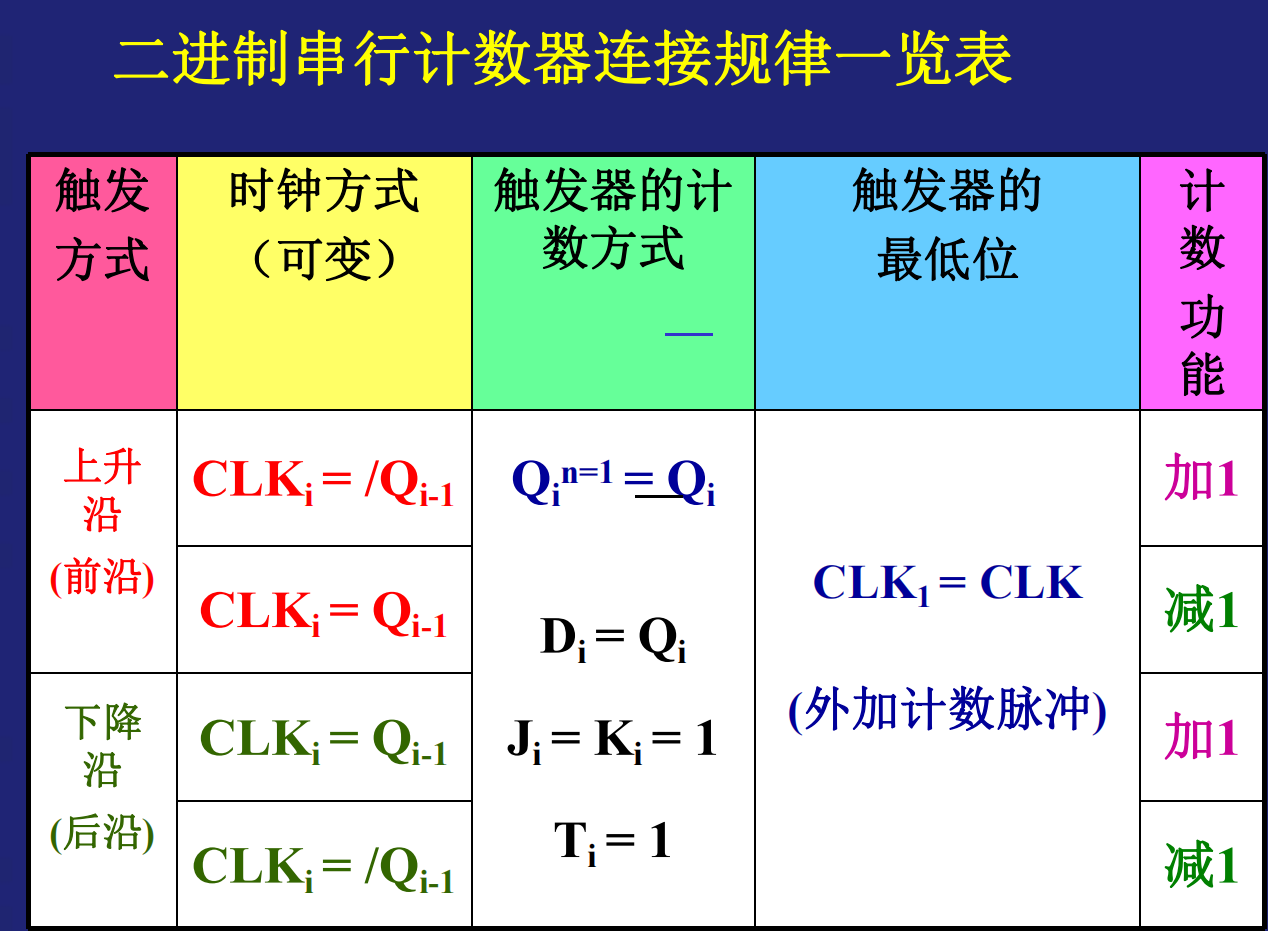

计数器

2160

2160

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?