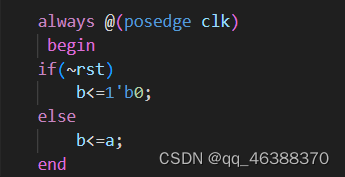

同步复位:

同步电路:存储电路中所有触发器的时钟输入端都接同一个时钟脉冲源,因而所有触发器的状态的变化都与所加的时钟脉冲信号同步

verilog描述一个同步的D触发器,当有时钟脉冲时才会做出响应,而reset只会在时钟上升沿或者下降沿才会做出响应。

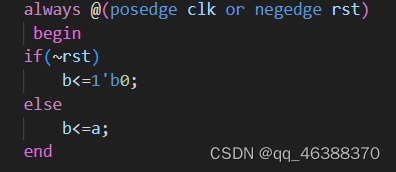

异步复位:

异步电路:电路没有统一的时钟,有些触发器的时钟输入端与时钟脉冲源相连,这些触发器的状态变化与时钟脉冲同步,而其他的触发器的状态变化不与时钟脉冲同步。

用verilog描述一个异步的D触发器,即使没有clk触发条件,rst有触发条件时也会复位,与时钟无关

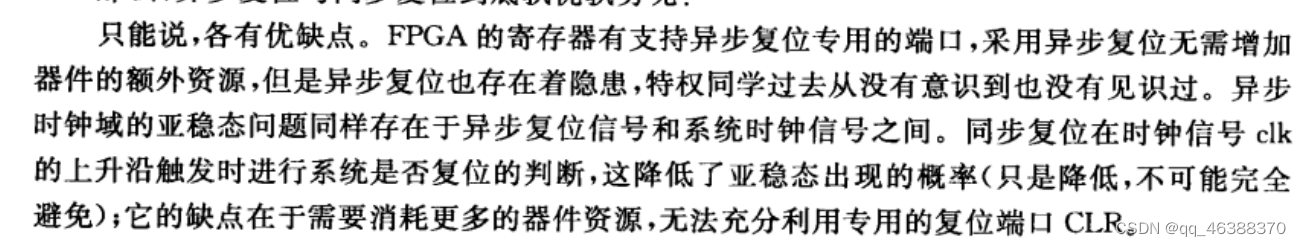

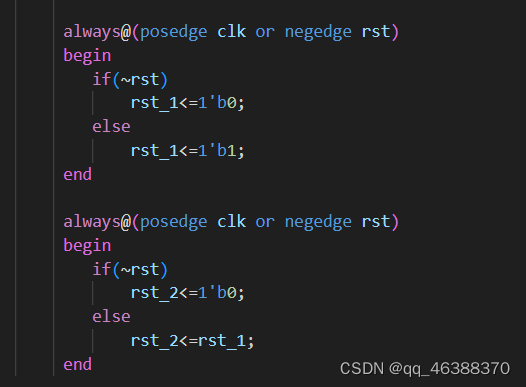

解决办法:采用异步复位,同步释放

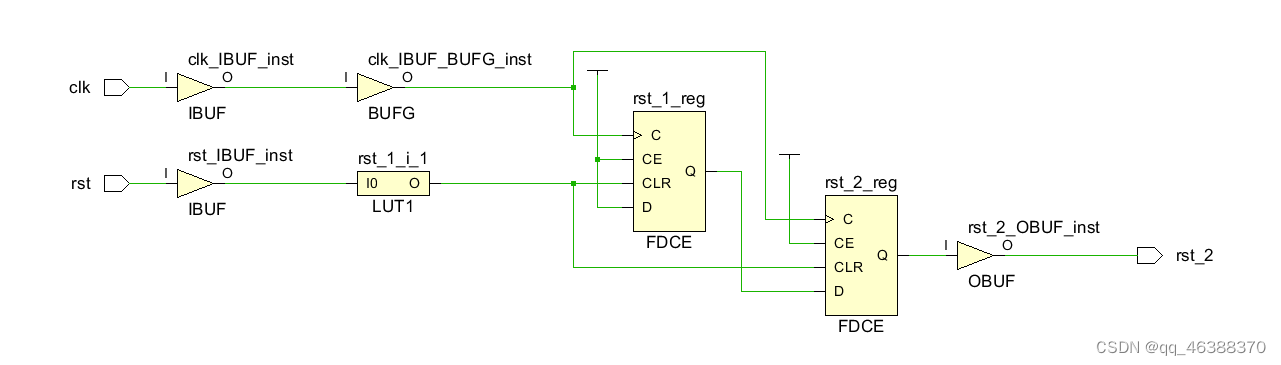

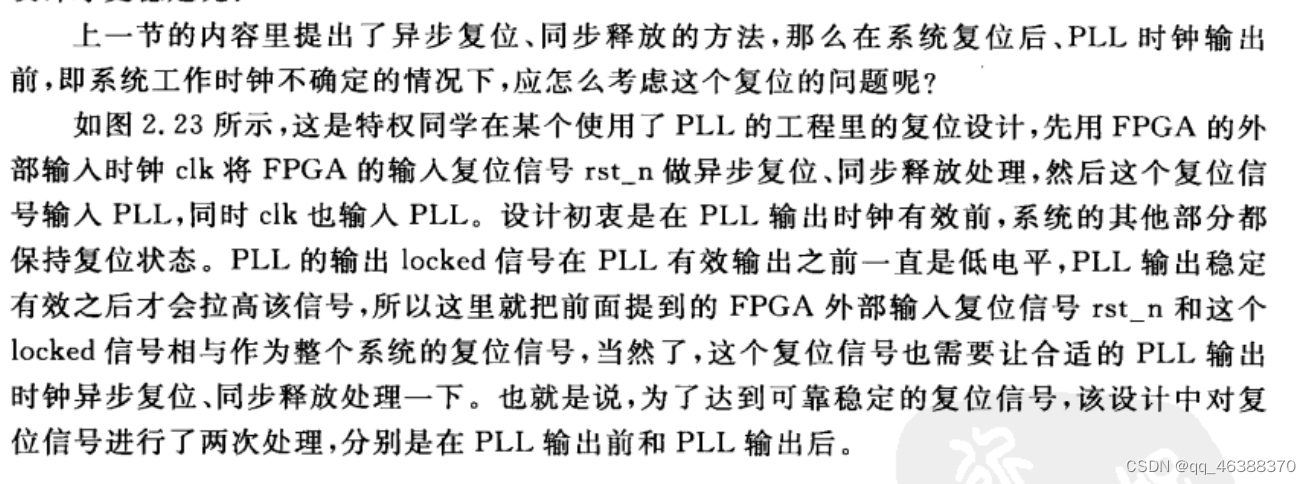

综合后的原理图:

解决了资源消耗和亚稳态问题。

948

948

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?