好久没更新了,这段时间一直在写小论文,终于投出去了,想要产出一篇论文还是很耗时间的。言归正传,我们接着来学习AC620。

一、原理

时序逻辑电路

时序逻辑电路是指电路任何时刻的稳态输出,不仅取决于当前的输入,还与前一时刻输入形成的状态有关。这跟组合逻辑电路相反,组合逻辑的输出只会跟目前的输入成一种函数关系。换句话说,时序逻辑电路拥有储存元件来存储信息,而组合逻辑电路则没有。下面以计数器为例。

设计计数器

本节设计一个计数器,使AC620开发板上的4个LED状态每500ms翻转一次。AC620开发板上的晶振输出时钟频率为50MHz,即时钟周期为20ns。这样可以计算得出500ms/20ns=25000000,即需要计数25000000次,也就是需要一个至少25位的计数器(2^25>25000000>2^24)。且每当计数次数达到目标就需要清零并重新计数。

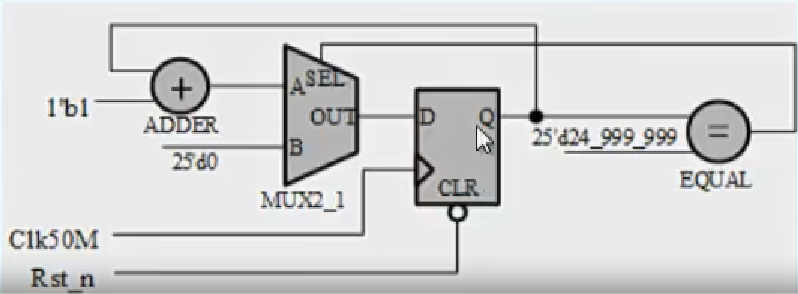

我们要编写的是一个实际硬件电路,所以要先搞清楚用什么器件和逻辑关系,我们通过一个加法器、二选一多路选择器、D触发器和比较器来实现目标。需要一定的数电基础。

先把目标解释成具体操作。计数25000000次,之后清零:从0开始,计数到24999999,下一次就要回到0。

先看二选一多路选择器,它由SEL控制,SEL=0,输出A;SEL=1,输出B。而SEL由最右边的比较器控制,当D触发器的输出为24999999时,比较器输出才为1。很明显,这是为了清零而设置的。加法器的作用是计数+1,存在D触发器中,输出Q反馈到输入,再加1。

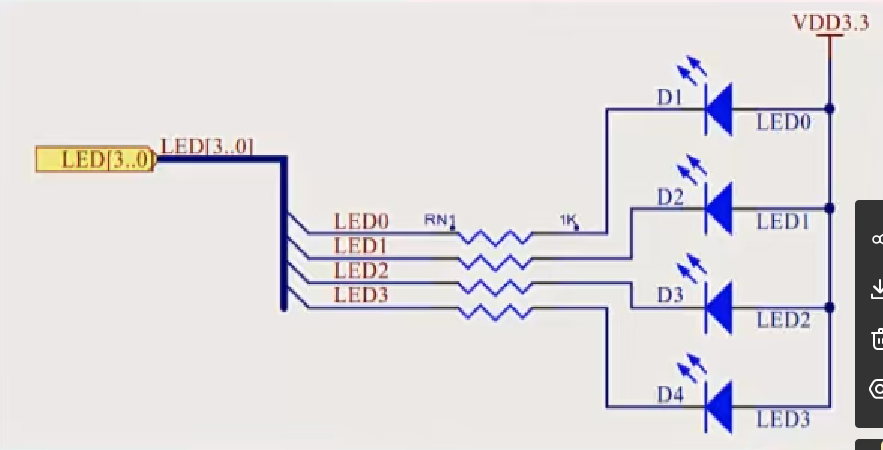

硬件电路

通过LED来显示。

二、开发

开发流程

创建Quartus Prime工程

编写计数器HDL描述文本

编写计数器测试脚本(testbench)

对计数器进行功能仿真

在Quartus Prime中执行布局布线

对计数器进行时序仿真

分配引脚并编译得到FPGA配置文件.sof

配置FPGA并运行

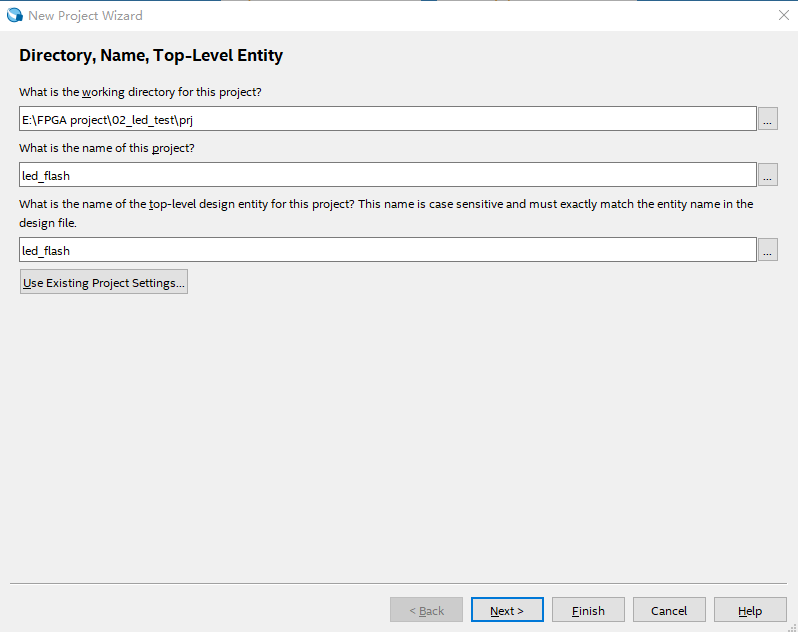

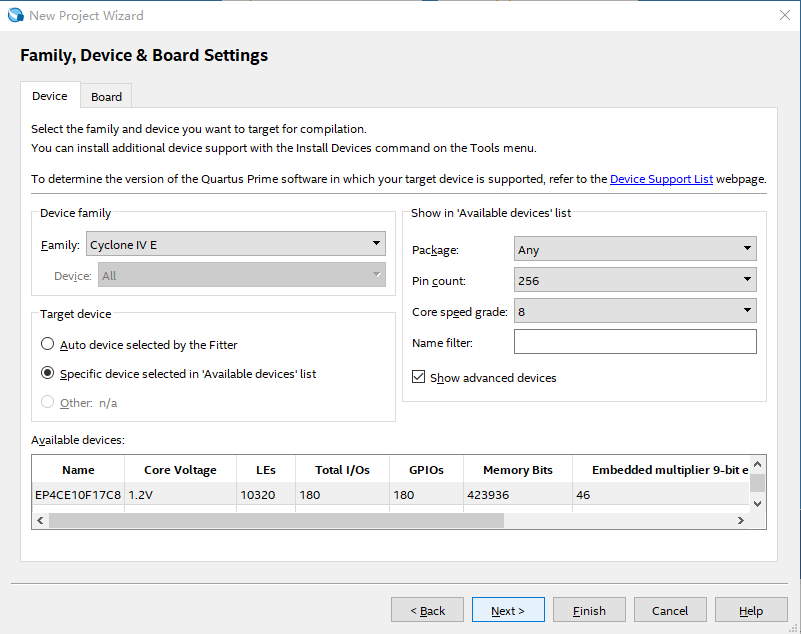

创建工程

创建"LED闪烁"工程

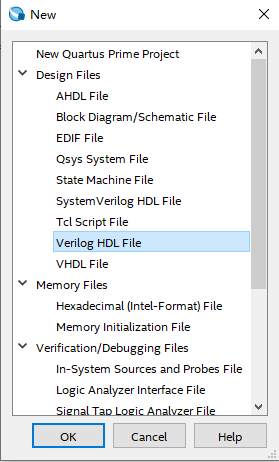

别忘了创建Verilog文件

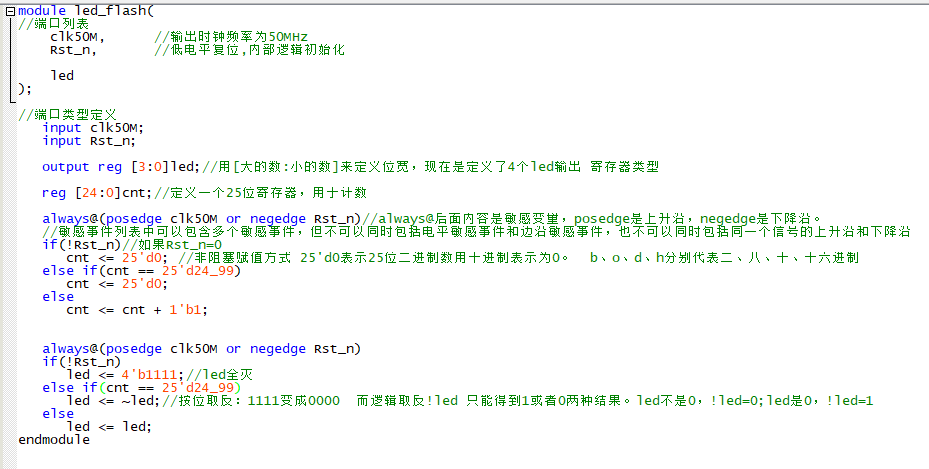

编写verilog文件

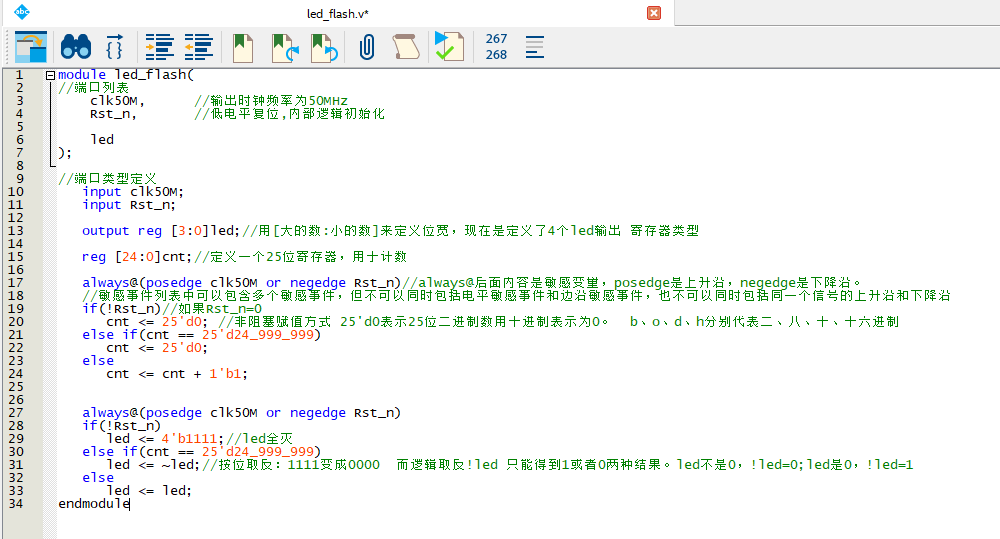

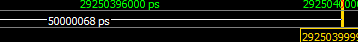

先进行端口列表的编写和端口类型的定义,然后设计了敏感事件,只要触发了敏感变量,就会执行下面的操作。如果复位端是低电平(低电平有效),那么计数器置零。如果计数到24999999,那么计数器置零。其他情况都是正常+1.

led灯是为了展示现象的,如果复位了,那么led全灭。如果计数到24999999,那么led全灭。其他情况led保持当前状态不变。

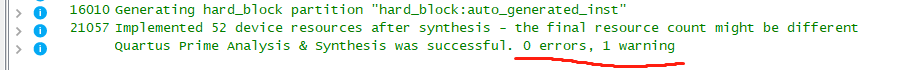

当前是把计数器的代码和led翻转的代码编写完成了。检查下有无错误

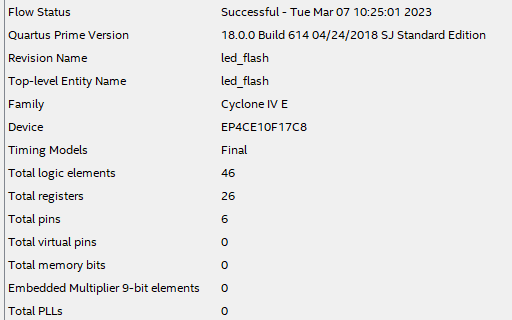

逻辑单元46个,寄存器26个,引脚6个。

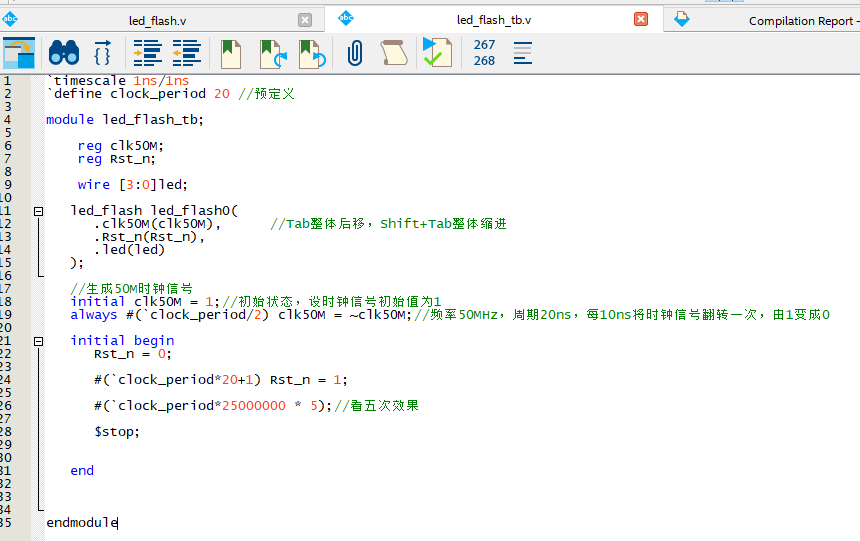

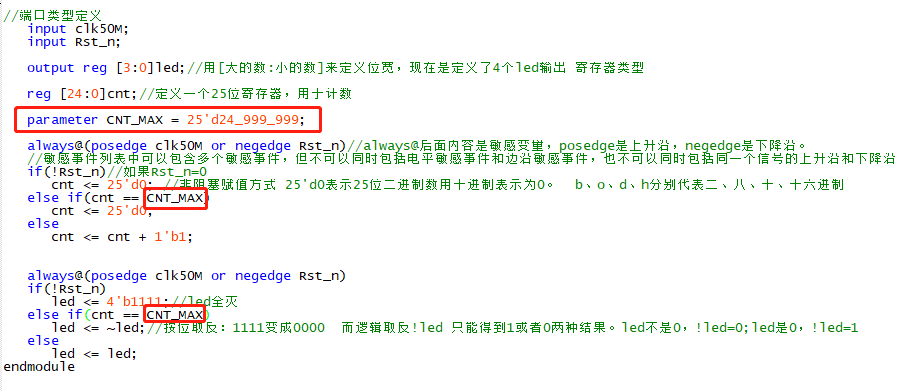

编写测试脚本(testbench)

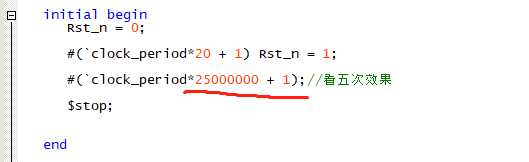

`define常用于定义常量,可以跨模块、跨文件,范围是整个工程。parameter定义的范围仅限模块。下面进行分析和综合

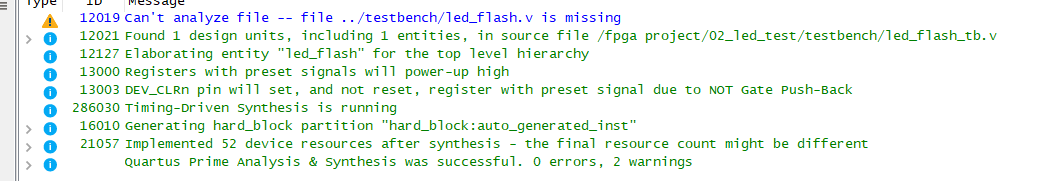

如果进行分析后出现很多报错,先去查是不是有拼写错误。我不小心把define拼错了,导致错误一大堆,改了很久才发现。

功能仿真

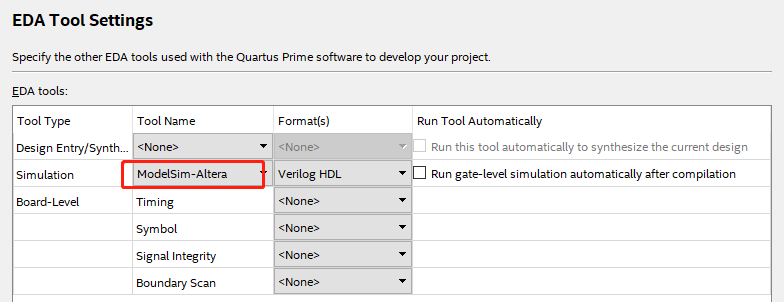

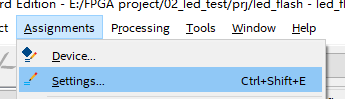

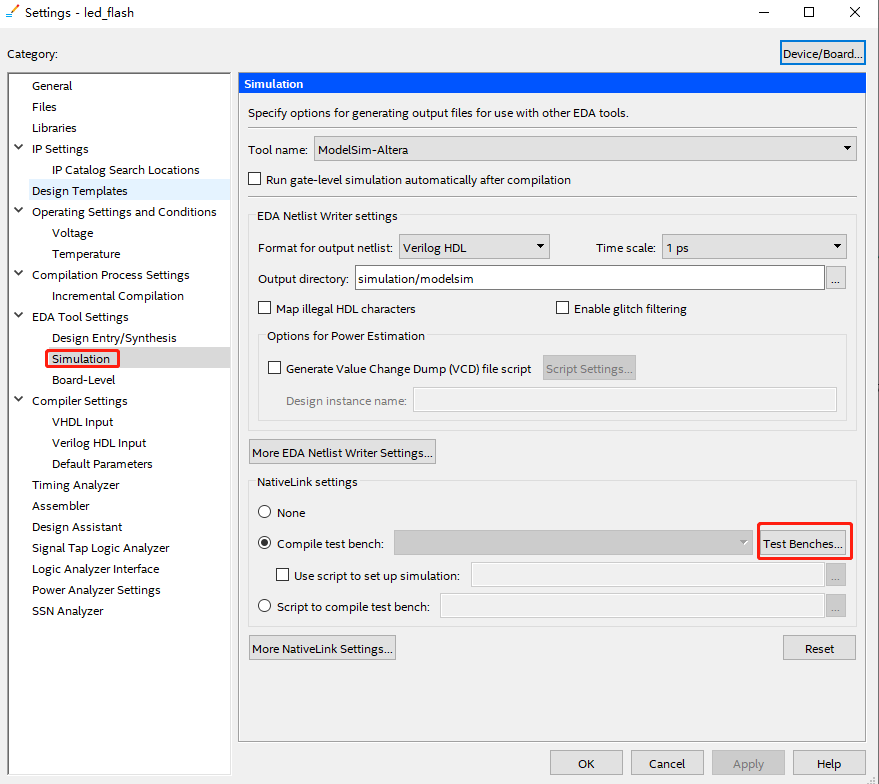

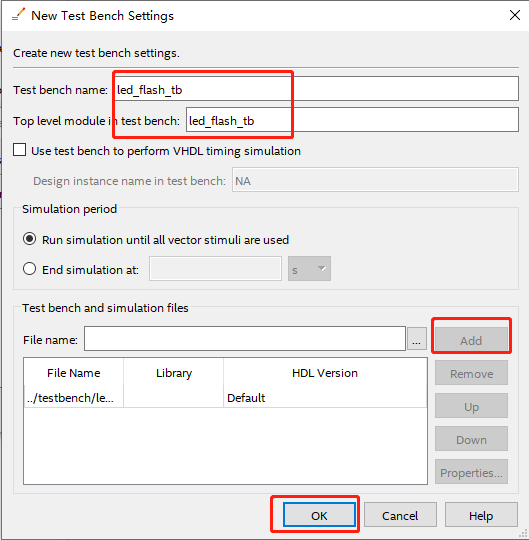

先设置NativeLink脚本,把刚写好tb文件导入

之前的博客也有说过,这个流程就不详细介绍了

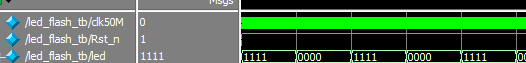

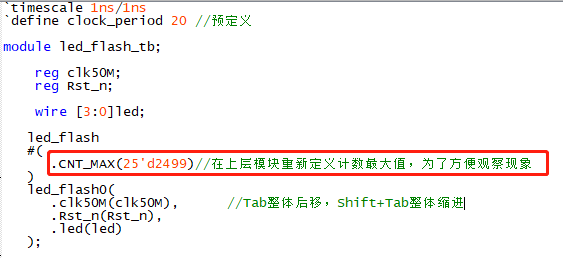

仿真之后我们发现,波形突然中断了,并没有持续到我们设置的时间,所以我们对代码进行更改

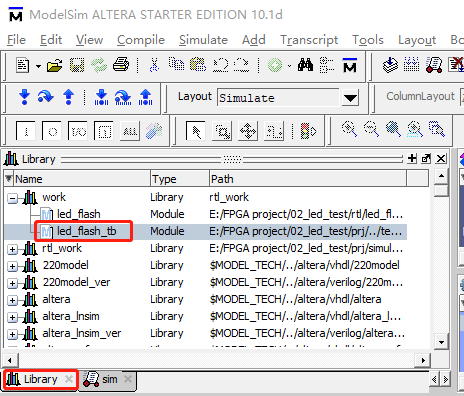

之后我们没必要关掉重新仿真,去library中找到tb文件,右键,点击重新编译Recompile

接着重新开始,出现弹框点击OK和Reload

重新run

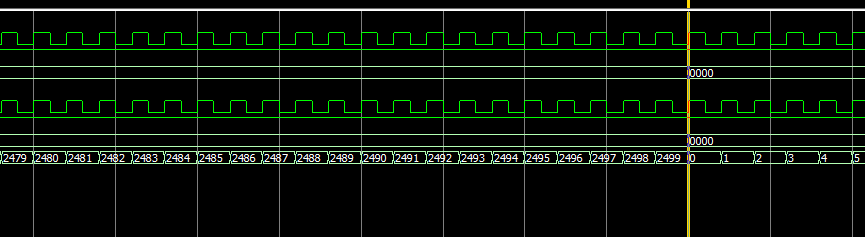

过程比较慢,不易于观察现象。所以我们更改一下代码,使计数达到2499时,led就翻转

重新编译文件,再次仿真

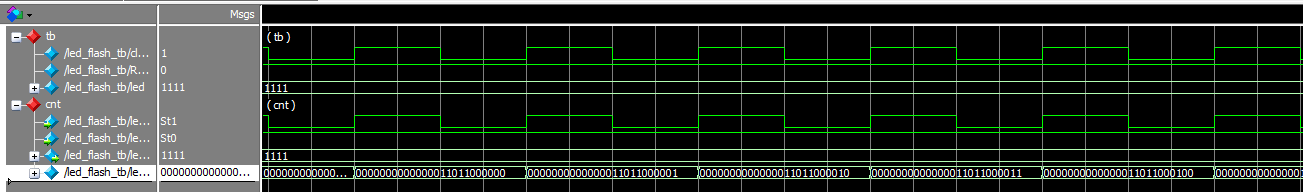

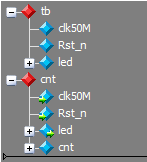

添加实际模块led_flash0的波形

把二进制转成十进制来观察

右键最下面cnt,Radix-unsigned

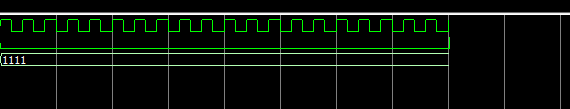

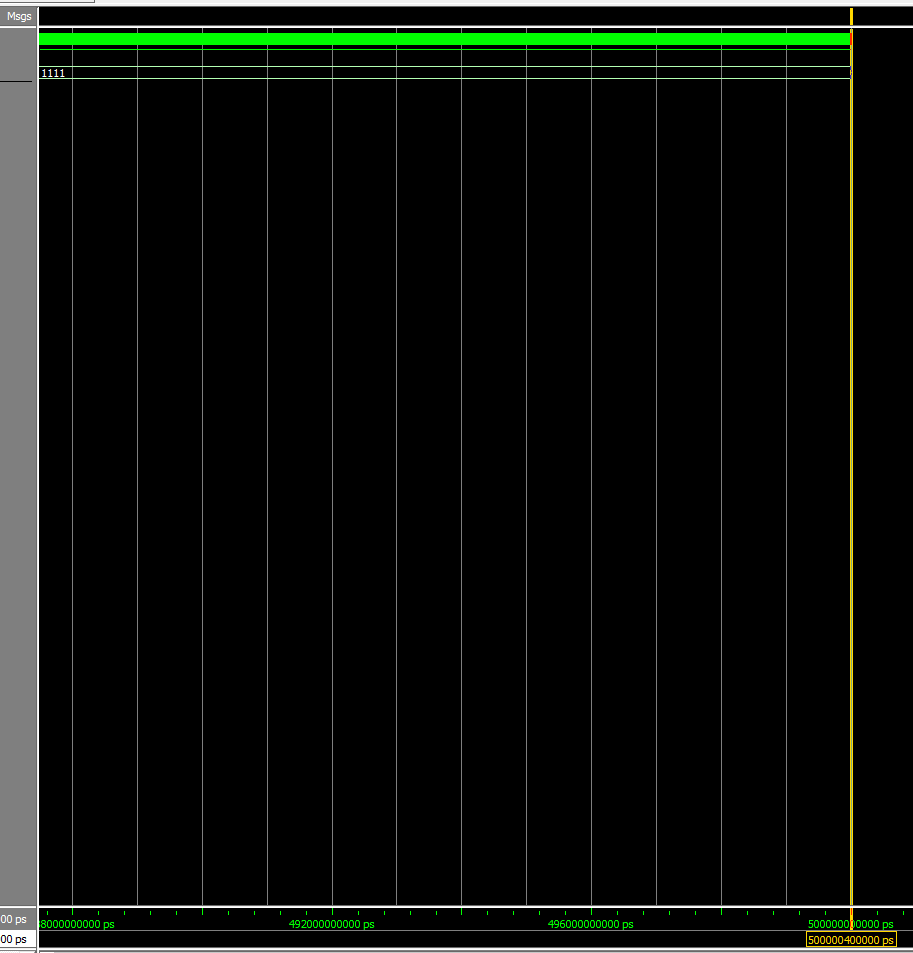

测定一个循环用时为50000ns,与设置的值一致

功能仿真结束。

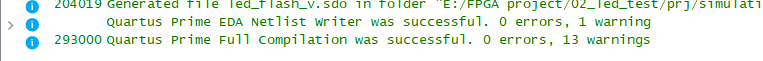

执行布局布线(全编译)

先用parameter定义计数最大值,这样修改起来就很方便了。

进行全编译,全编译时的计数最大值是与led_flash保持一致的,而不是tb

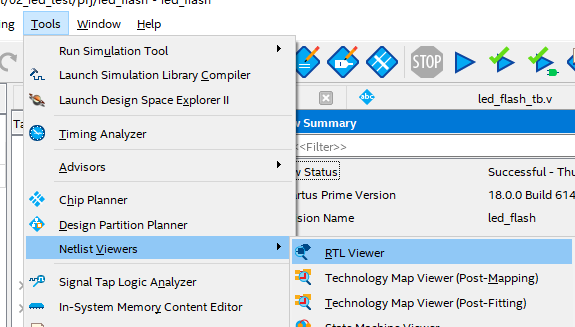

编译没问题之后,我们来查看RTL视图

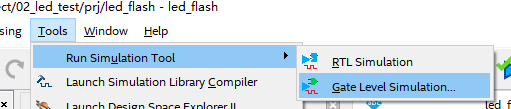

时序仿真(门级仿真)

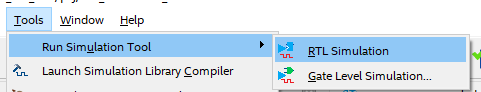

进行门级仿真

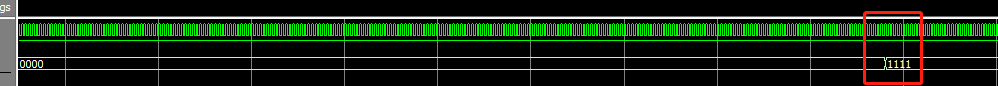

并没有与刻度线对应,存在延迟

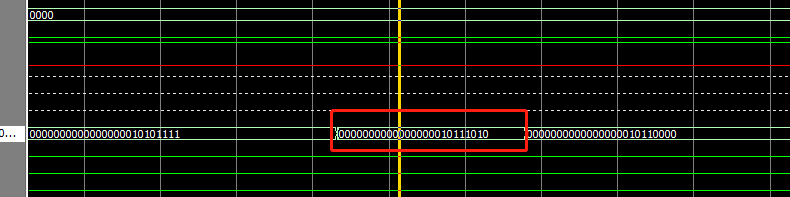

为什么仿真中会出现非常短暂的一个计数状态呢,这是因为当01111(前面都一样,就只说后五位)要变为10000时,这五位数都需要改变,但是实际中每位数改变所需要时间是不一致的,有的快有的慢,所以就出现了一个短暂的中间态(11010),也就是说第二位和第四位变得慢了一点,还没从1变成0。这个情况就叫做毛刺,是组合逻辑中存在的一个问题。但时序逻辑只看时钟边沿时的状态,其他时刻不管,所以就算毛刺存在,也基本不会在边沿时刻,那么逻辑就不会受到影响。但是如果时钟频率过高,时钟边沿采到毛刺状态的几率就大大增加,那么计数器就会有一定的出错可能。所以为了避免这种情况的发生,时钟频率不应该过高。

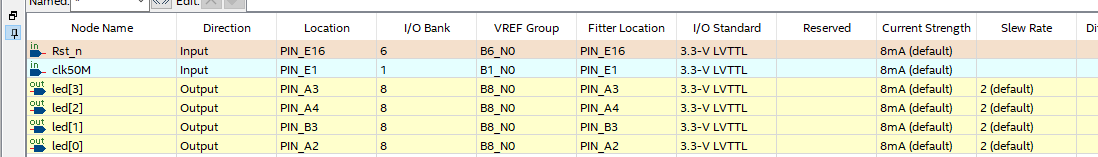

引脚分配

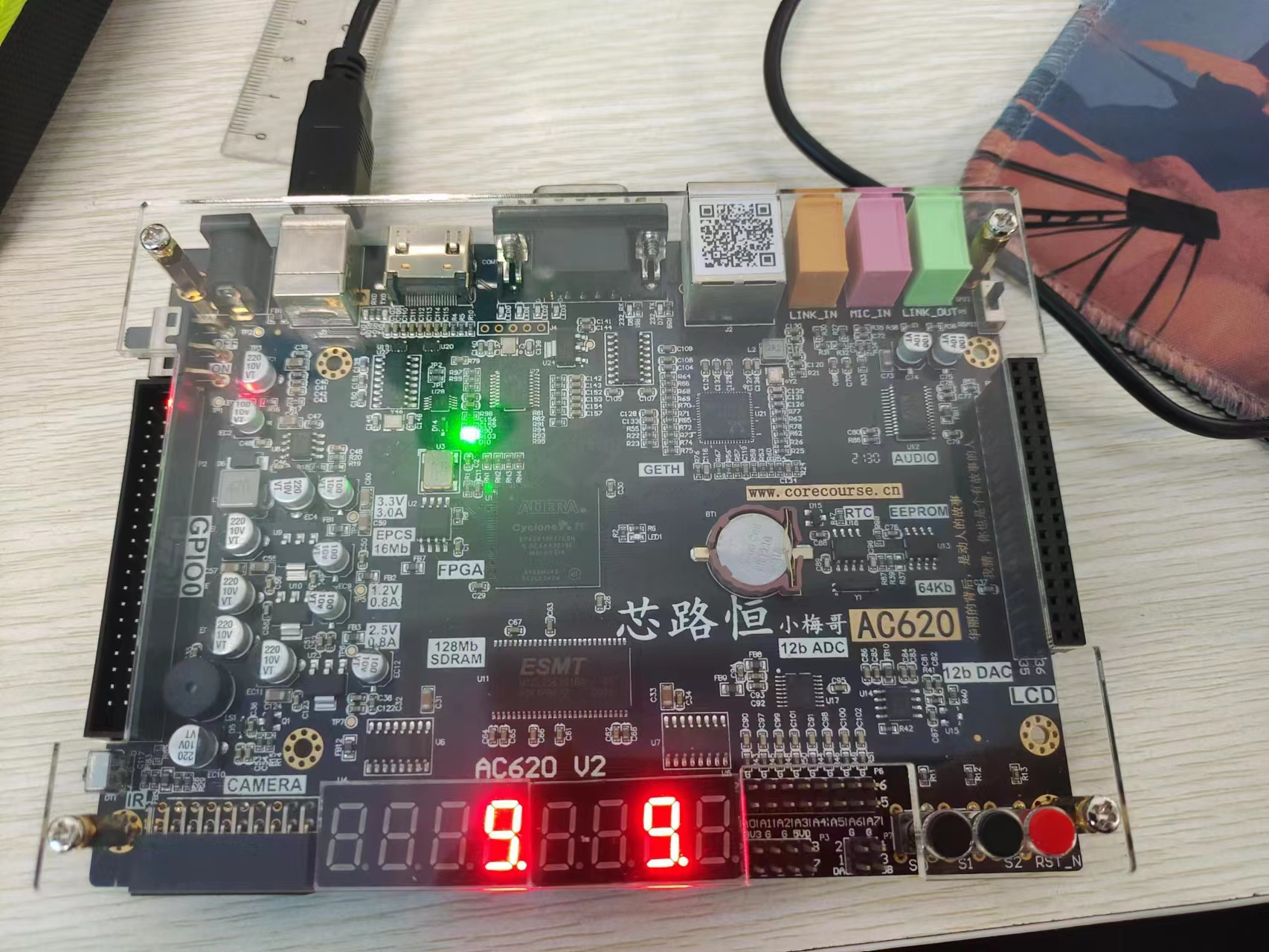

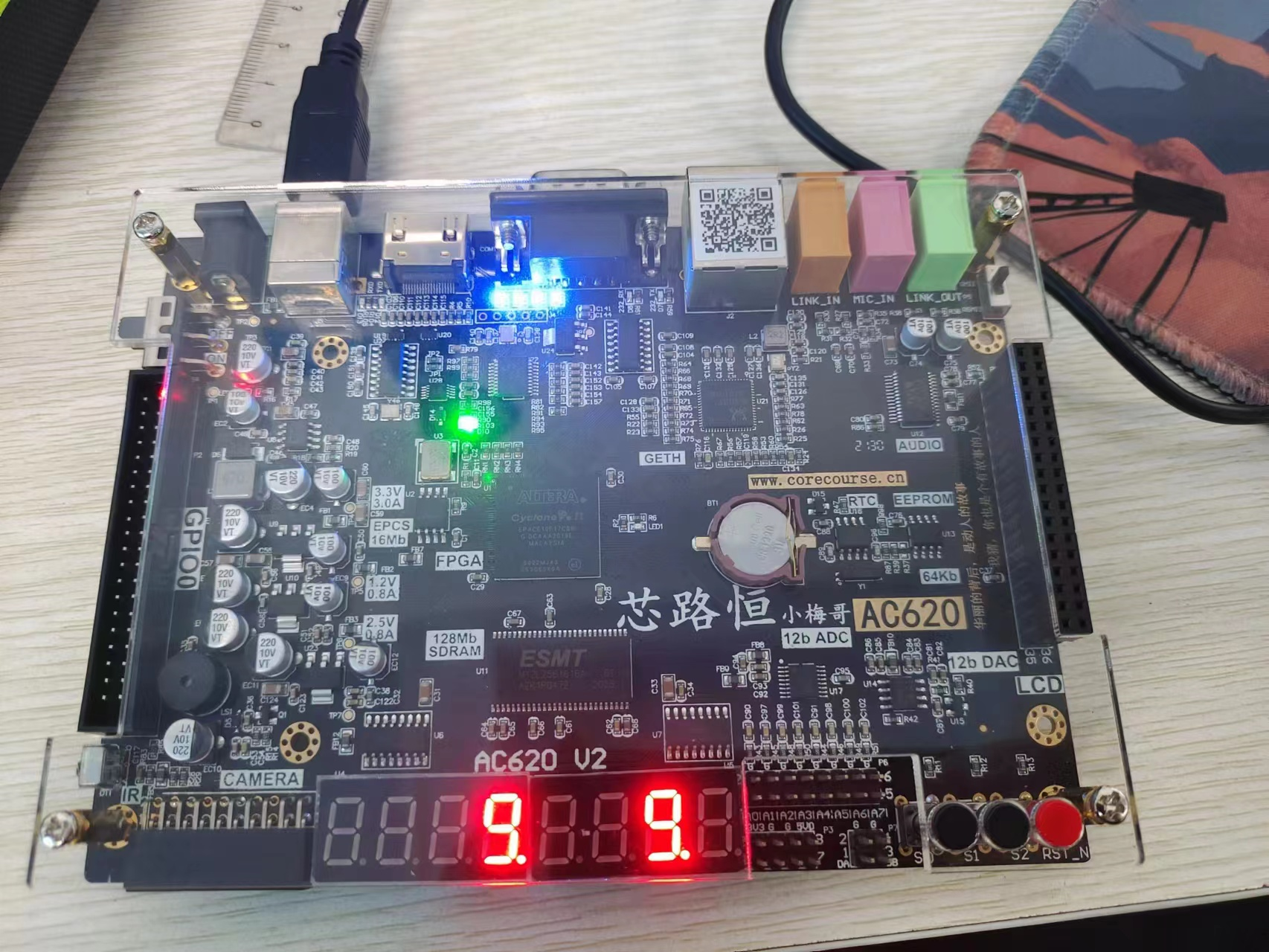

配置FPGA并运行

打开Programmer

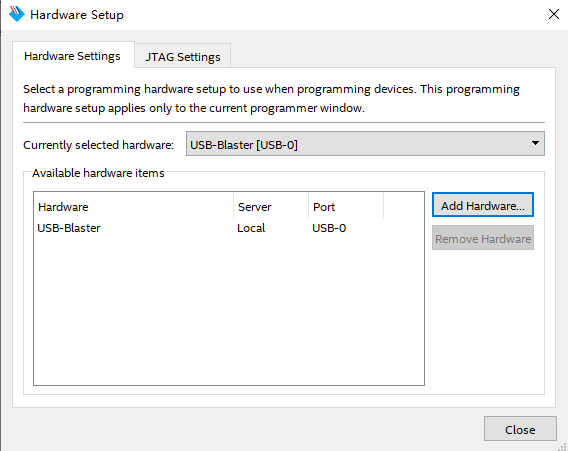

选择USB-Blaster

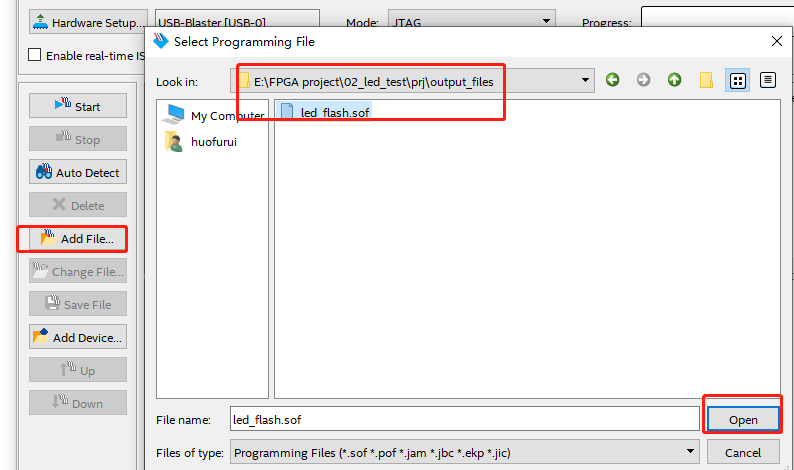

添加.sof文件

点击start

led灯不断闪烁,符合预期现象。

1109

1109

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?