Verilog数字系统设计九

任务和函数实验1

前言

随着人工智能的不断发展,机器学习这门技术也越来越重要,很多人都开启了学习机器学习,本文就介绍了机器学习的基础内容。提示:以下是本篇文章正文内容:

1 分别用任务和函数实现斐波纳契数列求职;

2 斐波纳契数列递归的方法定义如下:F(0)=0,F(1)=1,F(n)=F(n-1)+F(n-2);

一、任务和函数的区别?

示例:pandas 是基于NumPy 的一种工具,该工具是为了解决数据分析任务而创建的。

二、编程

1.要求:

1 分别用任务和函数实现斐波纳契数列求职;

2 斐波纳契数列递归的方法定义如下:F(0)=0,F(1)=1,F(n)=F(n-1)+F(n-2);

2.设计思路:

3.采用任务方法实现:

代码如下:

module Fibonacci_task(din,dout);

input [3:0] din;

output reg [7:0] dout;

always@(din)

FibonacciT(din,dout);

task FibonacciT(input [3:0] n ,output [7:0] result);

reg [7:0] f1;

reg [7:0] f2;

integer i;

if(n==0)

result=0;

else if(n==1)

result=1;

else

begin

f1=0;

f2=1;

for(i= n;i>1;i=i-1)

begin

result = f1 + f2;

f1=f2;

f2=result;

end

end

endtask

endmodule

测试代码如下:

module Fibonacci_task_tb;

reg [3:0] din_t;

wire[7:0] dout_t;

initial

begin

din_t=0;

end

always #10 din_t=din_t+1;

Fibonacci_task myFibonacci_task(

.dout(dout_t),

.din(din_t));

endmodule

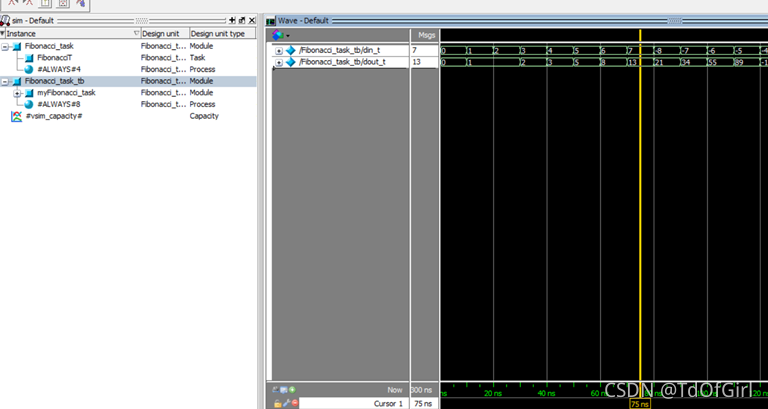

仿真波形如下:

4.采用函数方法实现:

代码如下:

module Fibonacci_func(dout,din);

input [3:0] din;

output reg[7:0] dout;

always@(din)

dout=fib(din);

function [7:0] fib;

input [3:0] n;

reg [7:0] f1;

reg [7:0] f2;

integer i;

begin

if(n==0)

fib=0;

else if(n==1)

fib=1;

else

begin

f1=0;

f2=1;

for(i= n;i>1;i=i-1)

begin

fib = f1 + f2;

f1=f2;

f2=fib;

end

end

end

endfunction

endmodule

测试代码如下:

module Fibonacci_func_tb;

reg [3:0] din_t;

wire[7:0] dout_t;

initial

begin

din_t=0;

end

always #10 din_t=din_t+1;

Fibonacci_func myFibonacci_func(

.dout(dout_t),

.din(din_t));

endmodule

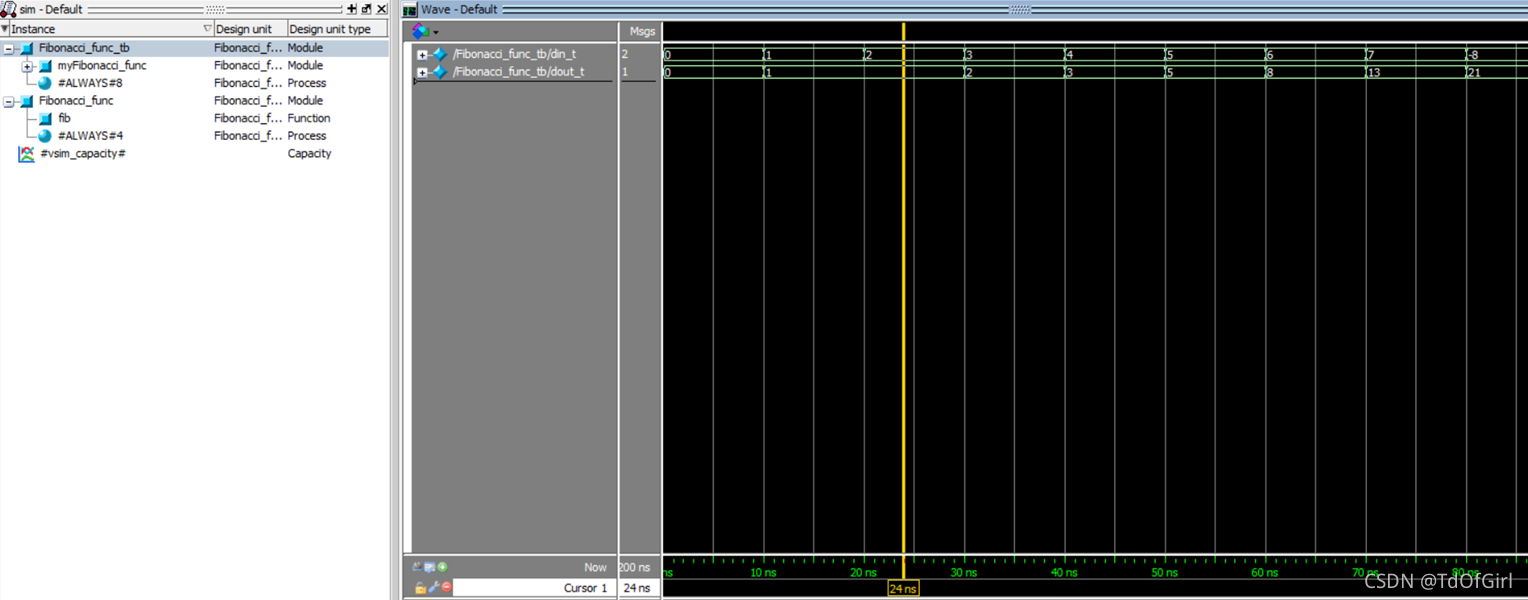

仿真波形如下:

总结

提示:

以上就是今天要分享的内容,本文仅仅简单介绍了用Verilog的函数和任务实现斐波那契数列。

1922

1922

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?