verilog实现led闪烁

一、介绍

使用verilog实现代码,实现led闪烁,每间隔200ms进行切换led灯

二、代码

module led (

input wire clk,

input wire rstn,

output wire[3:0] led

);

parameter TIME_200MS = 10_000_000;

reg[1:0] state;

reg[24:0] cnt;

reg[3:0] led_r;

always @(posedge clk or negedge rstn) begin

if(!rstn)begin

cnt<=24'd0;

end

else if(cnt == TIME_200MS - 1)begin

cnt<=24'd0;

end

else begin

cnt<=cnt+1'b1;

end

end

always @(posedge clk or negedge rstn) begin

if(!rstn)begin

state<=2'b00;

end

else if(cnt == TIME_200MS - 1) begin

state<=state+1'b1;

end

else begin

state<=state;

end

end

always @(posedge clk or negedge rstn) begin

if(!rstn)begin

led_r<=4'b0000;

end

else begin

case(state)

2'b00:led_r <= 4'b0001;

2'b01:led_r <= 4'b0010;

2'b10:led_r <= 4'b0100;

2'b11:led_r <= 4'b1000;

default led_r<=led_r;

endcase

end

end

assign led = led_r;

endmodule

三、仿真代码

`timescale 1ns/1ns

module led_tb ();

reg clk;

reg rstn;

wire[3:0] led;

parameter MAX_NUM = 10_000;

parameter SYS_CLK = 20;

always #(SYS_CLK/2) clk=~clk;

initial begin

clk = 1'b0;

rstn = 1'b0;

#(SYS_CLK*20);

rstn = 1'b1;

#(SYS_CLK*100000);

$stop;

end

led #(.TIME_200MS(MAX_NUM)) t1(

.clk(clk),

.rstn(rstn),

.led(led)

);

endmodule

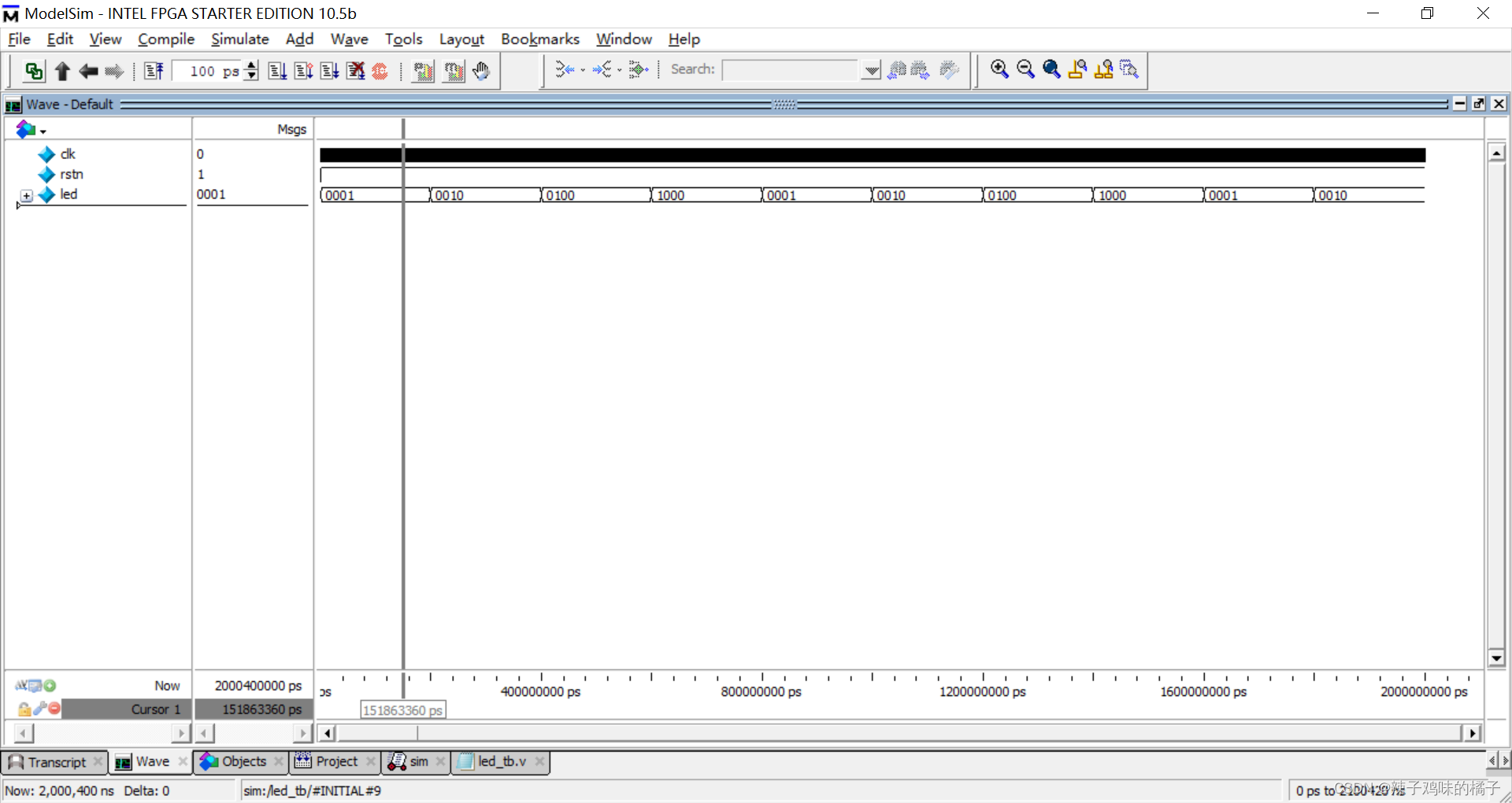

四、仿真结果

五、总结

控制led闪烁相对吉纳丹,使用一个计数器进行切换即可

447

447

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?