这篇文章主要借鉴了网上几篇文章,但是具体是哪个博主的已经忘了,因为当时我是做了笔记来着,当时不太理解,就直接复制粘贴保存在我的个人笔记中了。第三小结主要是我我在理解了这部分电路后的几个仿真电路,希望对大家有用,如果有问题也请大佬指出,谢谢。

- LDO电路简单介绍

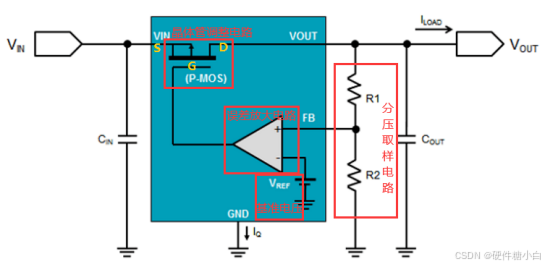

下面我们一起来学习LDO电路的经典拓扑结构。

1)分压取样电路:通过电阻R1和R2对输出电压进行采集,然后将采集到的电压返回运放的同相输入端或反相输入端;

2)基准电压:一般通过带隙电压基准产生的,目的是防止温度变化对基准电压产生过大影响;

3)误差放大电路:一般由运放加上外部电阻和电容组成,也可以不加电阻和电容。误差放大器的作用是将分压取样电路上采集到的电压与基准电压值作比较,再将比较结果放大输出给晶体调整管。

4)晶体管调整电路:把这个放大后的信号输出到晶体管的控制极(也就是MOS管的栅极或者三极管的基极),从而这个放大后的信号就可以控制晶体管的导通电压了,这就是一个负反馈调节回路。

2.晶体调整管

刚开始学习LDO电路这部分电路时,我一直无法理解mos管和晶体管是怎么调节输出电压的,主要因素还是因为模拟电路学得太烂了。看了一段时间的资料后,现在开始有了一些自己的感悟,希望我的理解对你有用。

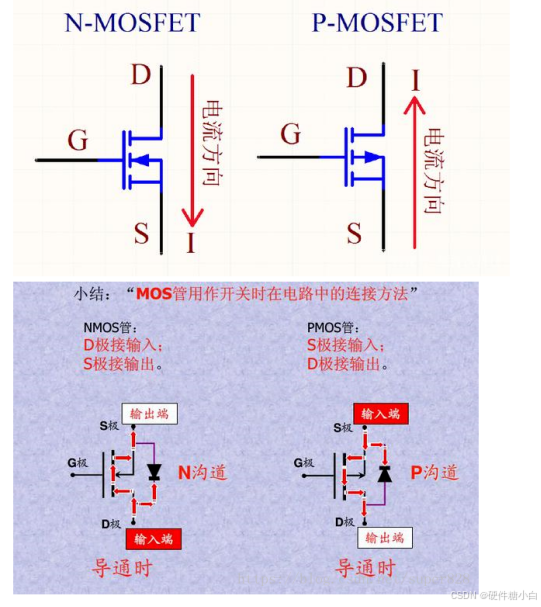

首先介绍一下PMOS和NMOS两种MOS管。我们知道,无论是NMOS还是PMOS都具有三个管脚:源极S(source)、栅极G(Gate)和漏极(Drain)。

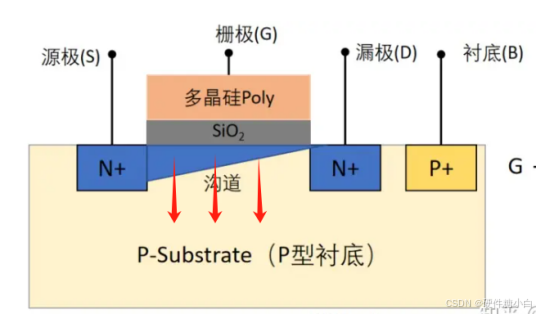

为什么要叫NMOS和PMOS,N的沟道和P沟道又是如何形成的呢?以NMOS为例,我们可以这样理解,NMOS是由两个N型金属作沟道,P型金属作衬底。最后形成的沟道是N沟道,所以叫NMOS。那N沟道是如何形成的呢?查阅资料可知,当g极和s极的压差Vgs>0时,在g极下端的金属板会产生大量正电子从而形成如下图所示的方向向下的电场。

同性相吸,异性相斥,所以正电子移动方向总是与电场方向相同,而负电子移动方向与电场方向相反。所以当Vgs>0时,存在在P型衬底中的负电子就会被吸引到绝缘体sio2下端与s极和d极的N型金属形成沟道,可以通过大量的负电子,我猜这也是为什么NMOS一般用于驱动大电流的场合。

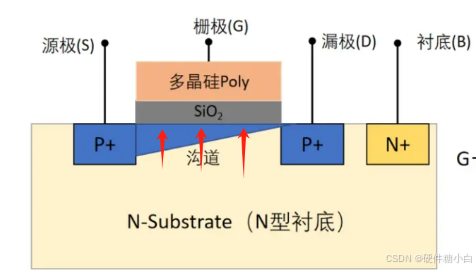

看完NMOS管我们再来看PMOS管就更好理解了,PMOS管的结构与NMOS的结构刚好相反,导通条件是Vgs<0。当Vgs<0时,形成方向向上的电场,吸引正电子,排斥负电子,最后形成P沟道。PMOS靠空穴的流动运送电流的MOS管。

通过上面的分析我们会发现,其实MOS管符号中的箭头指的方向其实就是MOS管导通时负电子移动的方向,NMOS向内,PMOS向外。

除了了解MOS管的上述知识,我们还需要了解MOS管的导通电阻,由于导通电阻存在,这样电流就会在这个电阻上消耗能量,这部分消耗的能量叫做导通损耗。选择导通电阻小的MOS管会减小导通损耗。现在的小功率MOS管导通电阻一般在几十毫欧左右,几毫欧的也有。

MOS在导通和截止的时候,一定不是在瞬间完成的。MOS两端的电压有一个下降的过程,流过的电流有一个上升的过程,在这段时间内,MOS管的损失是电压和电流的乘积,叫做开关损失。通常开关损失比导通损失大得多,而且开关频率越高,损失也越大。

导通瞬间电压和电流的乘积很大,造成的损失也就很大。缩短开关时间,可以减小每次导通时的损失;降低开关频率,可以减小单位时间内的开关次数。这两种办法都可以减小开关损失。我们常用的是NMOS,因为其导通电阻小,且容易制造。

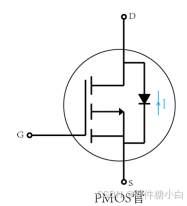

NMOS和PMOS的电流方向如下图所示。

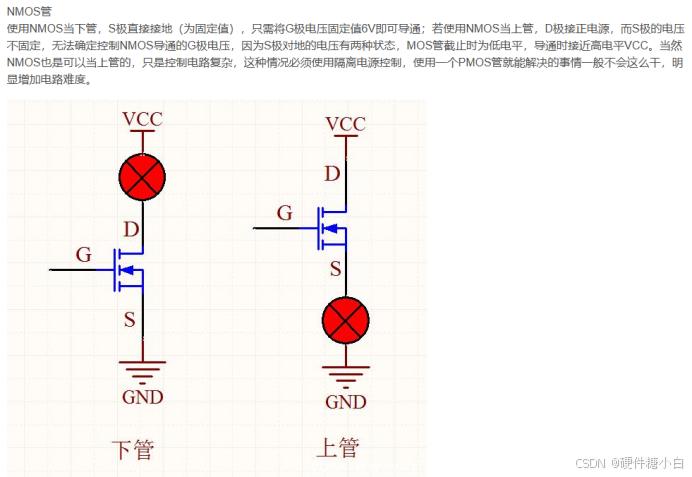

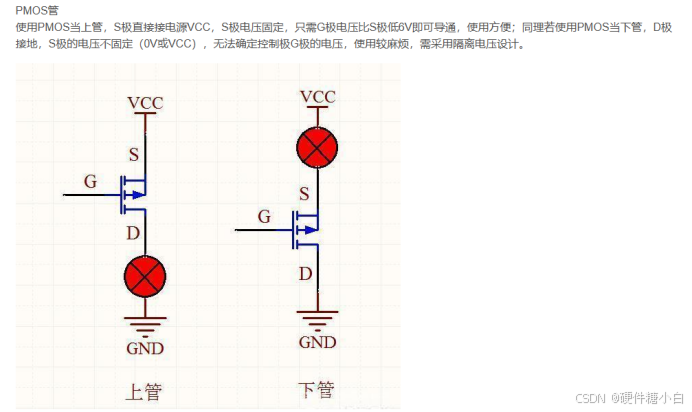

所以使用PMOS做上管、NMOS做下管比较方便。

NMOS管的主回路电流方向为D→S,导通条件为VGS有一定的压差,一般为5~10V(G电位比S电位高);而PMOS管的主回路电流方向为S→D,导通条件为VGS有一定的压差,一般为-5~-10V(S电位比G电位高),下面以导通压差6V为例。

3.MOS管做调整管的LDO电路

1)PMOS做调整管

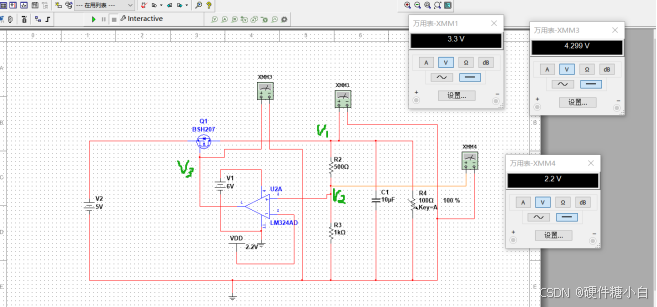

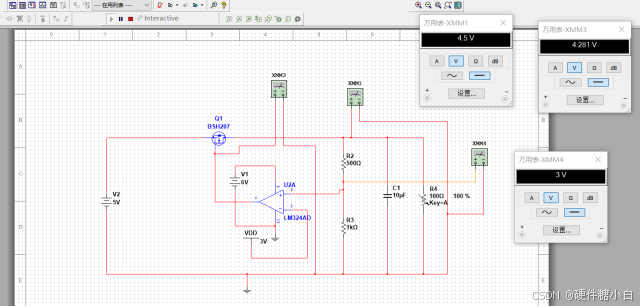

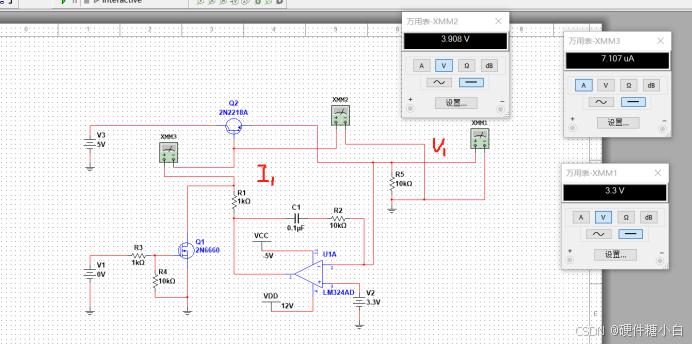

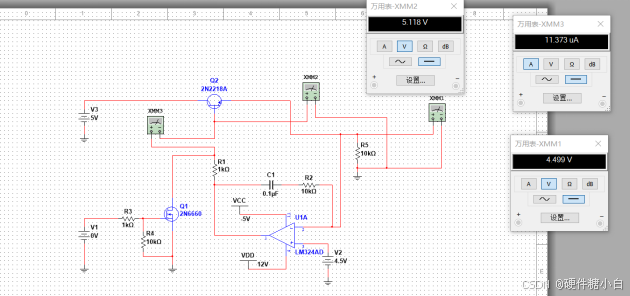

首先分析这个LDO是如何将5V电压降低到3.3V电压的。在下面的电路图中,R2和R3是分压取样电路,VDD是基准电压源,LM324AD是误差放大器,Q1是调整管。确定了基准电压和分压取样电路,LDO的输出电压也基本确定了,根据运放“虚短”和“虚断”的性质,我们可以得到R3*V1/(R2+R3)=VDD(基准电压源),即V1=(1+R2/R1)*2.2=3.3V。

上面浅显的分析好像不足以证明什么,我再根据我自己的理解分析一遍。首先输入电压是5V,我们的目的是将它降到3.3V,LDO是如何实现这一功能的呢?首先,由于运放“虚短”的特性,所以运放会强制使其同相输入端和反相输入端的输入电压相同,因此当基准电压为2.2V时,运放会强制使得V2也为2.2V,V2实际是V1经过R2和R3分压所得,此时V1为3.3V。如果在工作过程中,误差放大器检测到输入端电压不同,如V2高于2.2V,即V1>3.3V,那么误差放大器就会增大它的输出电压,由于输入电压5V不变,所以Vgs下降,Vgs下降会使得PMOS的沟道变小,沟道变小会使从S到D的电流变小,从而V1下降,直到V1下降到3.3V为止。稳定后V3的电压也会稳定在一个固定值,Vgs也会稳定,P沟道的大小也会稳定,输出电压也就稳定了。

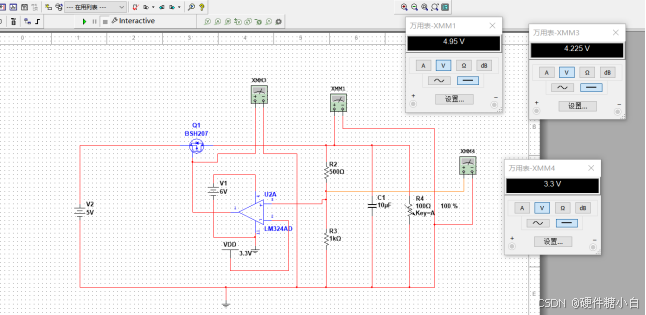

那你说,你这个是降低到3.3V的,那你能不能降低到1.5V,4.5V,或者其他电压啊?当然可以,我们只需要改变电路中的基准电压或者分压取样电路的电阻阻值就可以实现这个需求。要实现4.5V,我们只需要改变基准电压的大小,这里将基准电压调整为3V。

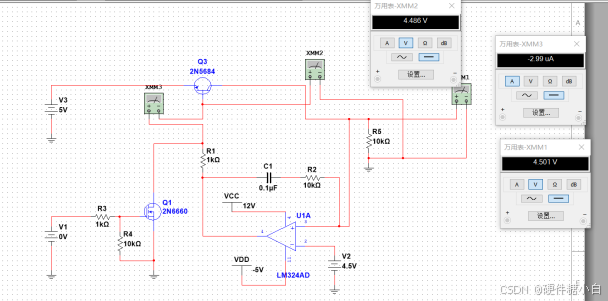

由上图可以得基准电压调整为3V时,输出电压为4.5V,调整电阻的大小方法也是一样的,就是遵循运放“虚短”的原则。

仔细对比上面两张仿真图,我们会发现,误差放大器的输出电压V3也发生了变化,当输出为3.3V时,V3=4.299,输出为4.5V时,V3=4.281,由此可得3.3V时的Vgs小于4.5V时的Vgs(此处比较的是绝对值),为什么呢?我们可以这样想,输出4.5V时,我们需要从前级的5V获得更多的能量,所以要求Vgs的压差尽量大一点,这样PMOS管导通沟道就大输出电流就大,所以输出电压就大。要获得3.3V时需要的能量较小,所以Vgs压差较小,PMOS导通沟道小,通过P沟道的电流小,所以输出电压小。不信我们可以让输出更大一点,看看Vgs有没有在变大。

从上面的图中,我们可以看到误差放大器的输出电压相较于输出4.5V时的输出电压有在降低,所以Vgs变得更大了。证明猜想正确。

- NMOS做调整管

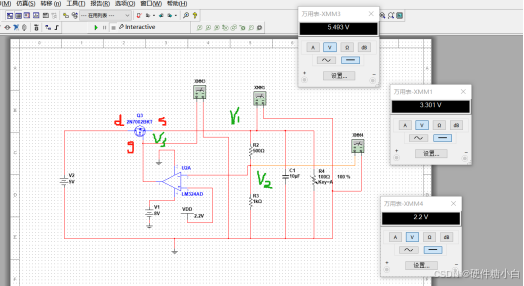

对于N管做调整管的电路,我们还是以3.3V为例。在下面的电路中,将PMOS换成了NMOS,交换式务必注意NMOS的方向,在第二小节中提到过NMOS的电流方向是从d到s,PMOS是从s到n。还有误差放大器的反馈端变成了反相输入端,误差放大器的供电电压从原来的6V上升到8V。至于为什么,我会在下一个章节讲。

我们先分析这个电路降压的原理。首先,还是由于运放“虚短”的特性,所以强制使得两个输入端电压相同。从下面的仿真电路中我们可以看到V2的电压等于基准电压VDD,大小为2.2V。由电阻分压原理我们就可以计算得V1的电压为3.3V。整个电路的调节过程就是,V1处的电压如果发生变化,通过V2反馈给误差放大器,误差放大器输出一个V3,Vgs大小变化,调整N管的导通程度,最终使得输出电压稳定,V2=2.2V。

同样给出一个输出4.5V的例子。

通过上面两个例子,我们可以计算出输出3.3V时的Vgs=2.193,输出4.5V时的Vgs=2.5。显然,输出4.5V时的Vgs更大,又验证了我们前面提到的,因为需要输出的能量多,所以要求Vgs更大,使得MOS管的导通沟道越大,输出电流更大,输出电压也更大。

4.三极管做调整管的LDO电路

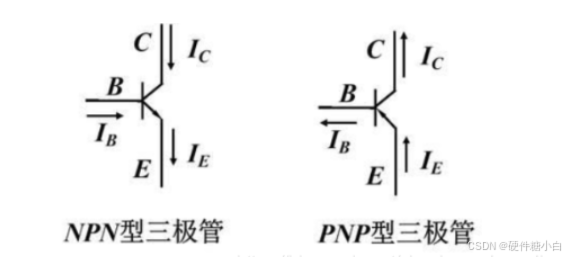

在讲三极管做调整管的电路之前,我们先复习一下三极管的知识。三极管,又称双极性晶体管,是电流驱动型器件。NPN三极管的电流方向为基极流向发射极(驱动电流从基极流入),集电极流向发射极。PNP三极管的电流方向为发射极流向基极(驱动电流从基极流出),发射极流向集电极。如下图所示。

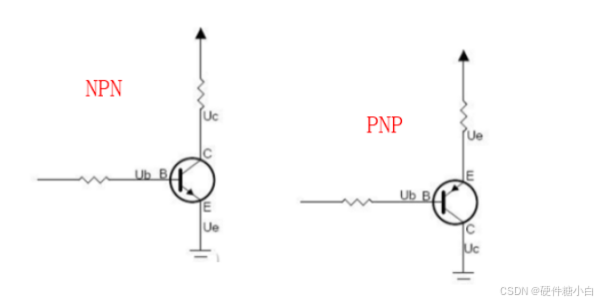

在设计电路时,NPN通常做下管,PNP做上管。NPN的集电极通常接VCC,PNP管的发射极接VCC。

- NPN做调整管

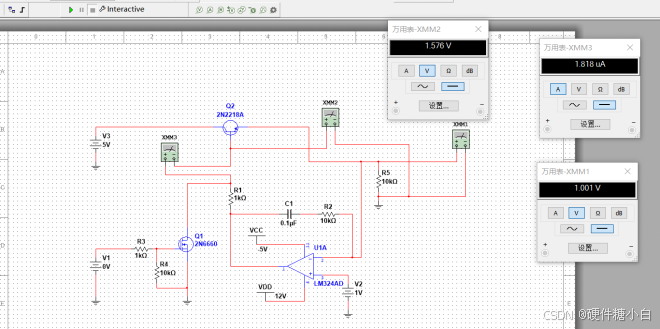

下面的电路也是仿照LDO的拓扑图来设计的,调整管使用的是NPN,减少了分压取样电路,直接从LDO输出反馈到误差放大器输入端。设计时注意我们的电流是从集电极(C)流向发射极(E),所以按照图示放置三极管。反馈电压从误差放大器的反相端输入。电路的工作过程是,当V1发生变化,与误差放大器同相输入端的3.3V进行比较,如果V1>3.3V,输出电流下降,Q2集电极和发射机导通能力下降,通过npn管的电流下降,输出电压V1下降,直到与3.3V相等为止。如果V1<3.3V,输出电流增加,Q2集电极和发射机导通能力上升,通过npn管的电流增加,输出电压V1变大,直到与3.3V相等为止。

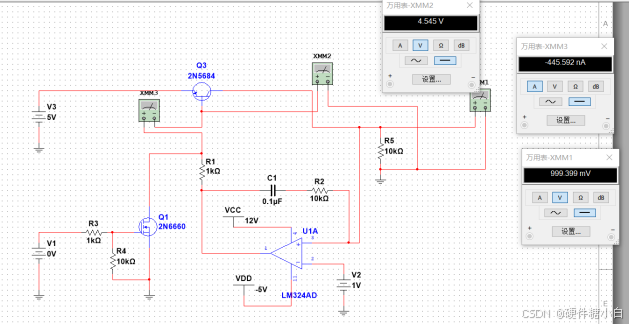

同样我们在这里给出一个输出电压1V和输出电压4.5V的例子来分析Ib对三极管导通能力的影响。

通过上面三个例子,我们可以得到,输出电压越大,Ib越大。电路中加入的这个NMOS电路是用来关闭LDO输出的。给NMOS的栅极一个高电平,NMOS导通,将NPN的基极拉底,NPN截止,LDO不输出。调节负压时改变反馈端(接同相输入端)和npn的方向(对调)。

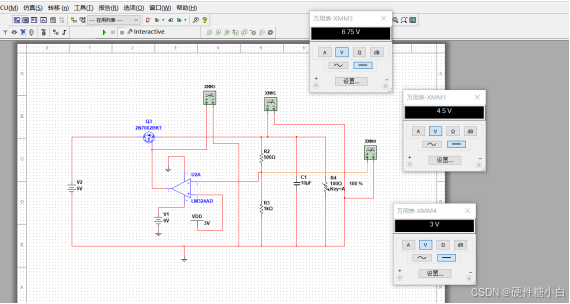

- PNP做调整管

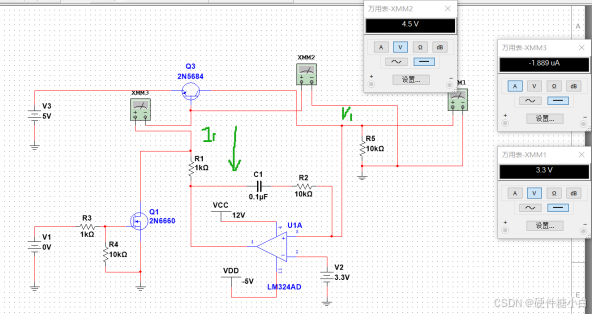

相较于上面的电路下面的电路更换调整管为PNP,反馈电压给到误差放大器同相输入端反馈。电路的工作过程是,当V1发生变化,与误差放大器反相输入端的3.3V进行比较,如果V1>3.3V,流出基极电流下降,Q3集电极和发射机导通能力下降,通过pnp管的电流下降,输出电压V1下降,直到与3.3V相等为止。如果V1<3.3V,输出电流增加,Q3集电极和发射机导通能力上升,通过pnp管的电流增加,输出电压V1变大,直到与3.3V相等为止。

同样我们在这里给出一个输出电压1V和输出电压4.5V的例子来分析Ib对三极管导通能力的影响。

通过上面三个例子,我们可以得到,输出电压越大,Ib越大(绝对值)。

457

457

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?