目录

今天在听B站上张鸿老师讲模拟集成电路第六章——Amp频率响应的时候讲到了一阶RC网络,自己对于这一部分知识的掌握略显生疏,于是在课后进行了仿真调试,将所得结果记录在此。

一、理论分析

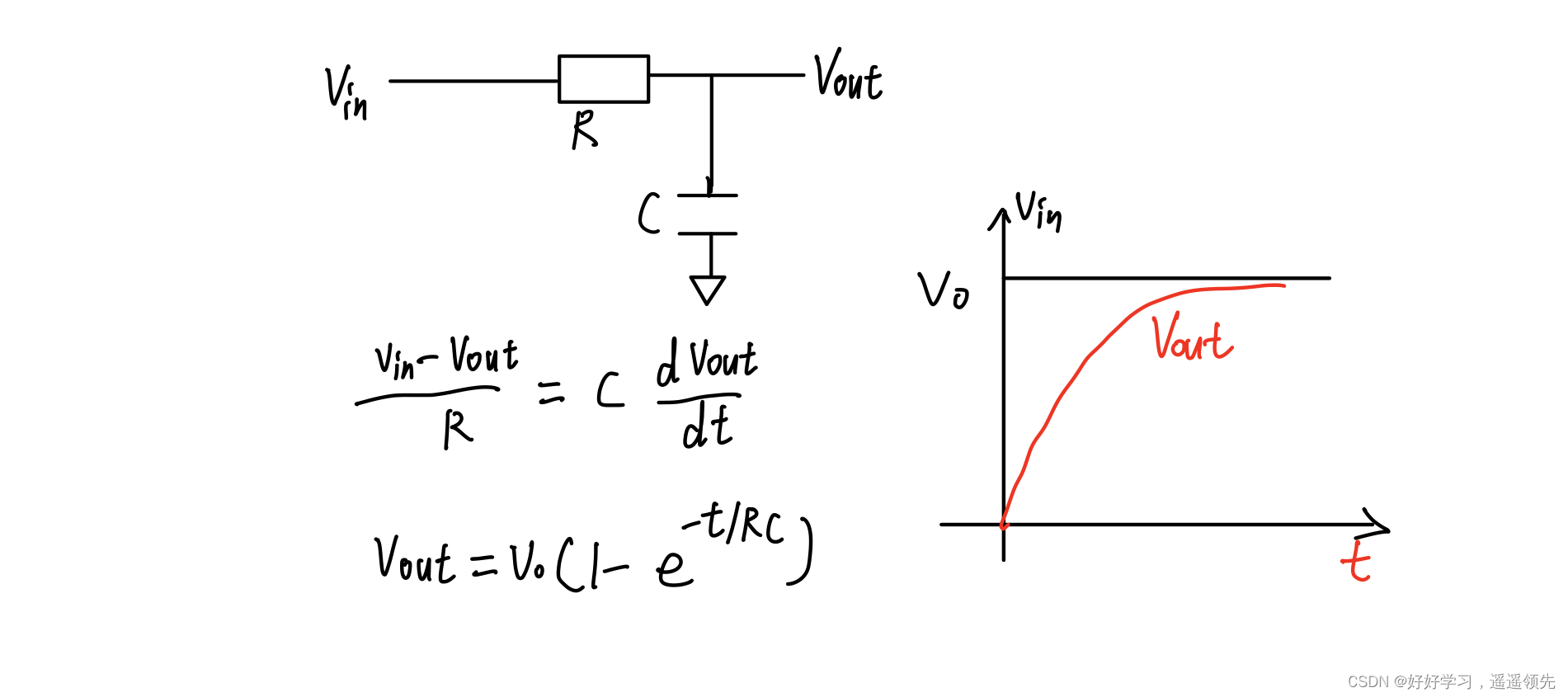

1、时间域

一阶RC低通滤波器的电路图如图所示。分析对此电路施加阶跃响应,并由基尔霍夫电压电流定律可列出一阶微分方程,对方程求解可得Vout 的表达式。式中RC就是时间常数,它反应电路中相应变化的快慢,时间常数越小,则电路相应变化越快,反之则越慢。

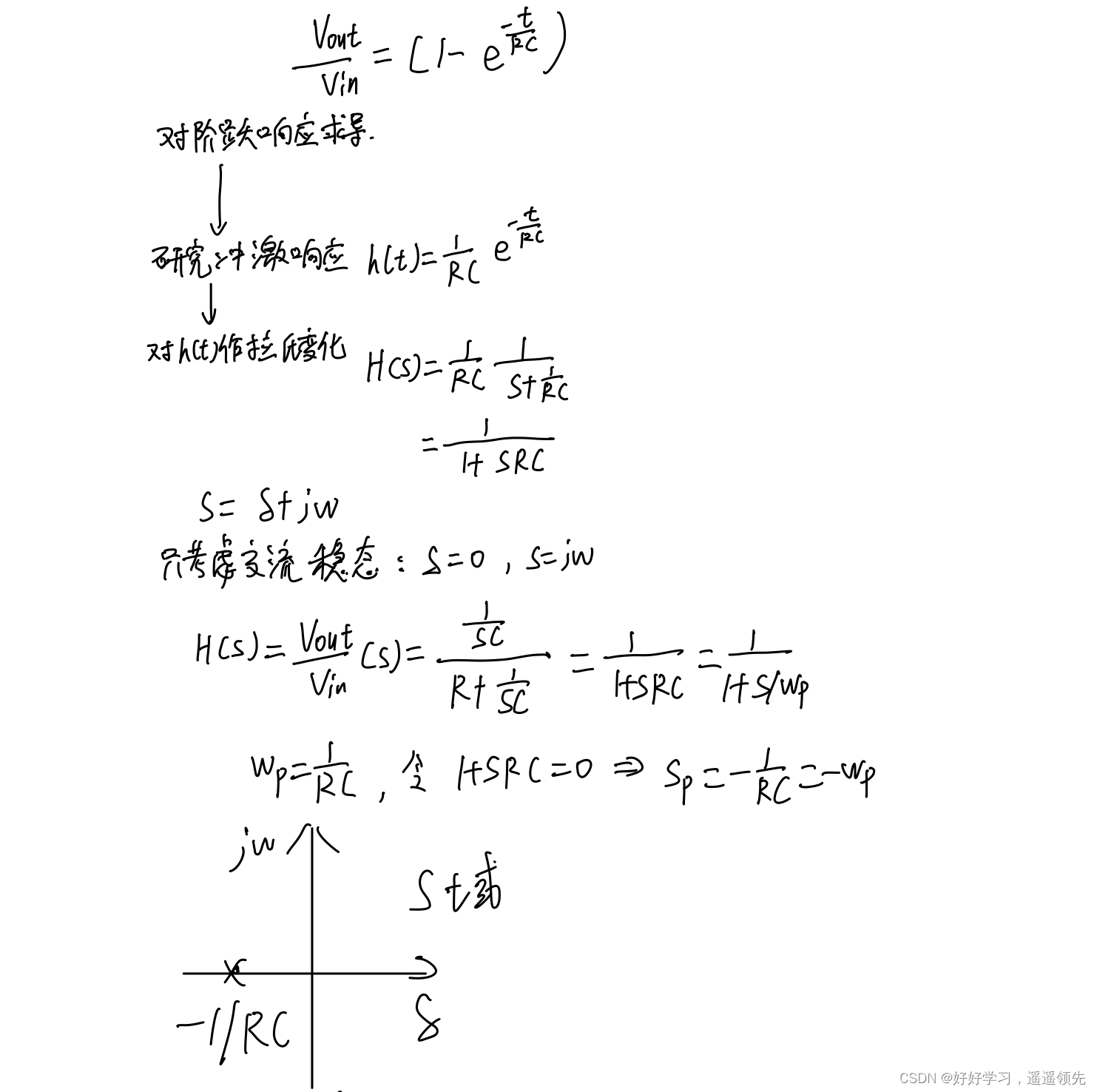

2、频域

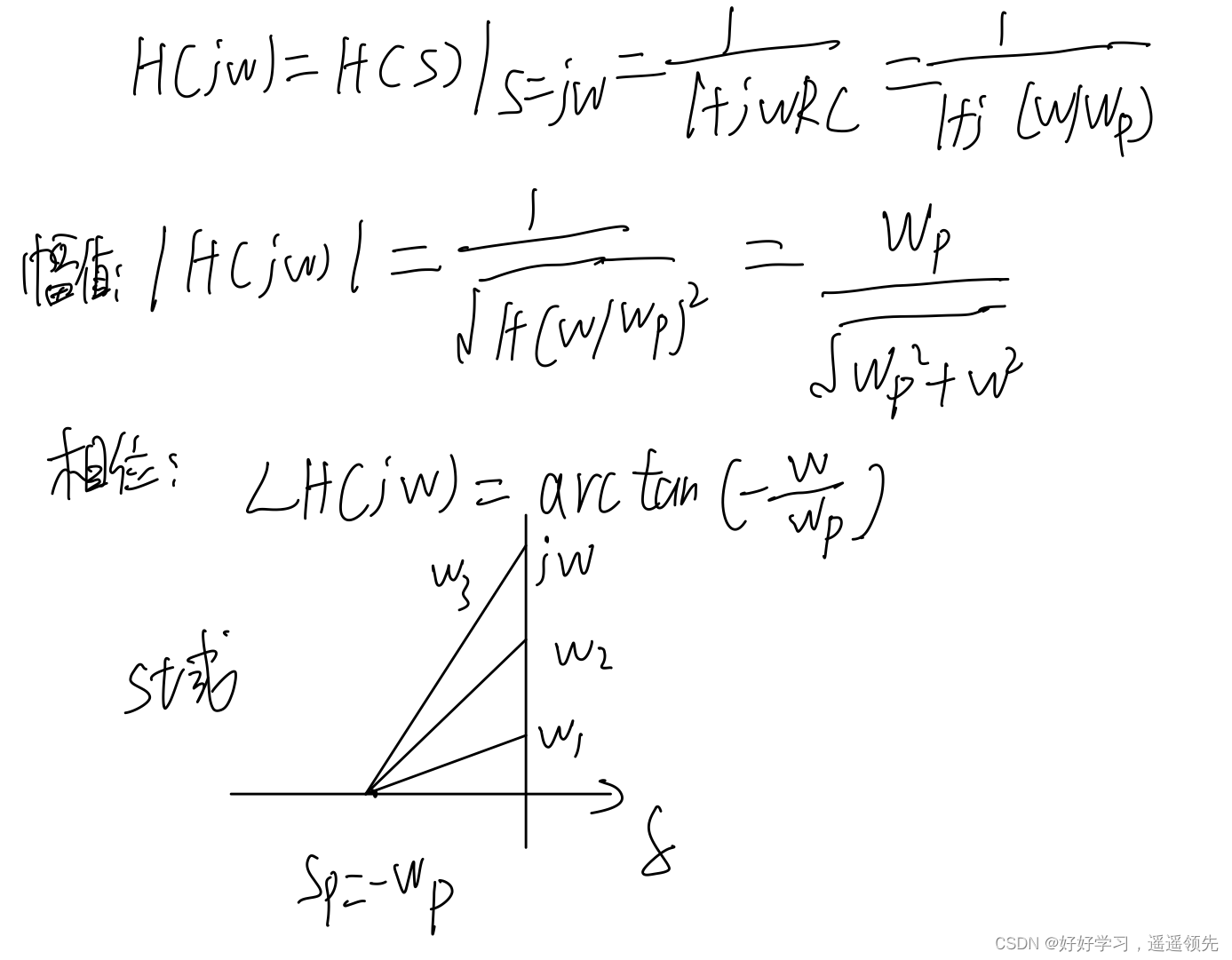

由上就得到了电路在时间域上的表达式,为了在复频域上进行研究,对表达式进行一系列变换:

得到电路的传输函数,写出其幅值和相位的表达式

以上理论分析也只是简单的一个推导过程,有关一阶RC低通电路的详细可以看看别人的教程,此处就不再赘述。

二、仿真

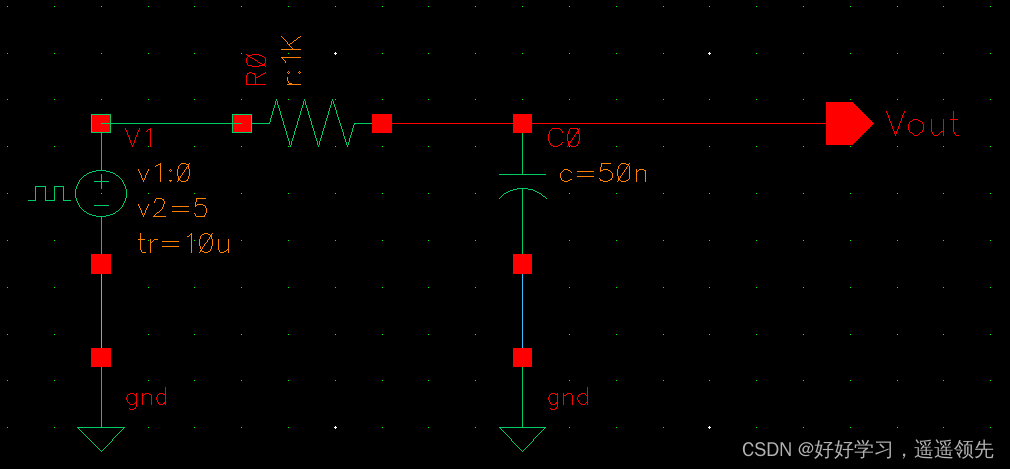

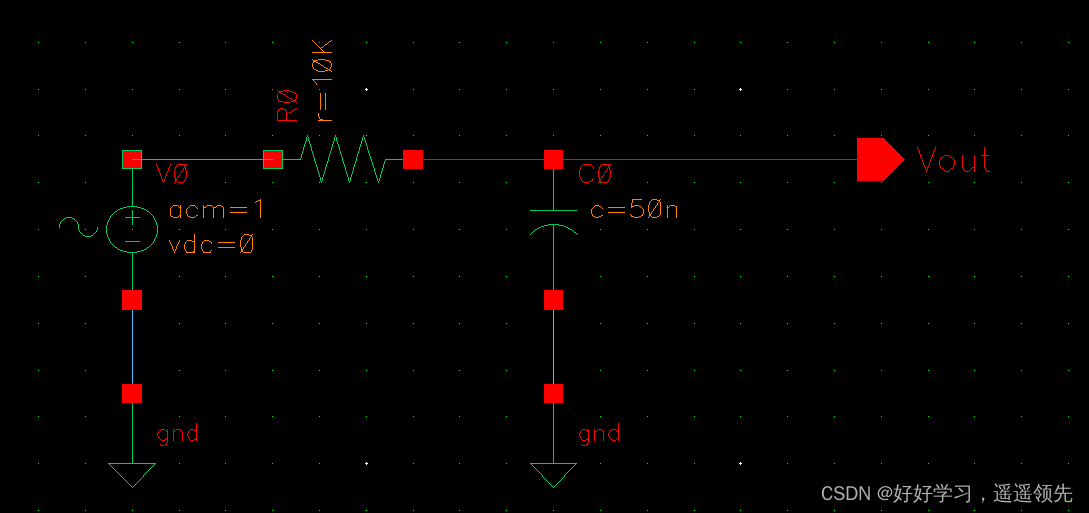

1、电路搭建

打开virtuoso,创建电路原理图。其中的元器件均在analogLib这个模拟库中找到。电阻R=1K,电容C=50nF,添加一个激励源vpulse。激励源vpulse具体参数设置:Voltage 1 =0V,Voltage2 =5V,周期period设置为500us,上升时间(Rise time)10us,下降时间10us。时间常数=RC

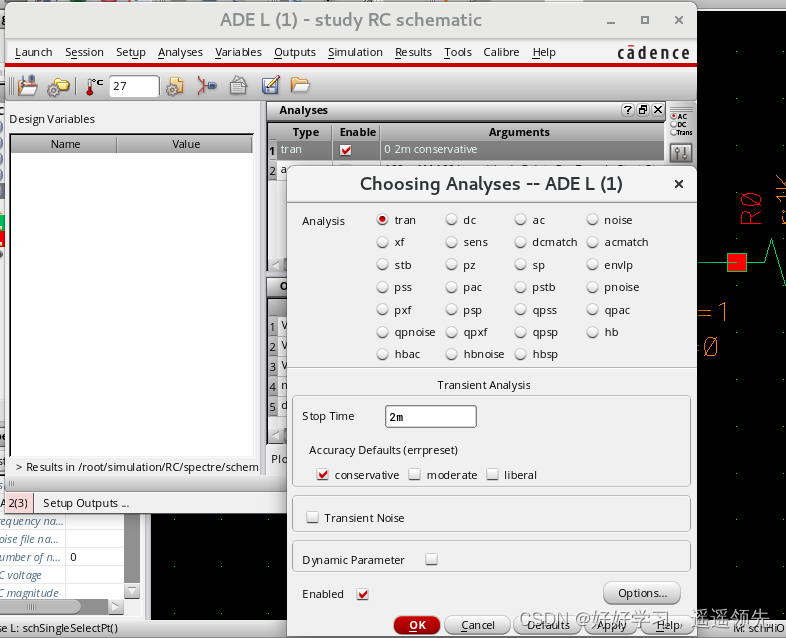

2、ADE L设置

选择tran(瞬态)仿真,仿真时间2ms,精度选了第一个(中间的也行)。添加输入:就是连接电阻和vpulse的线;添加输出:Vout 那根线。

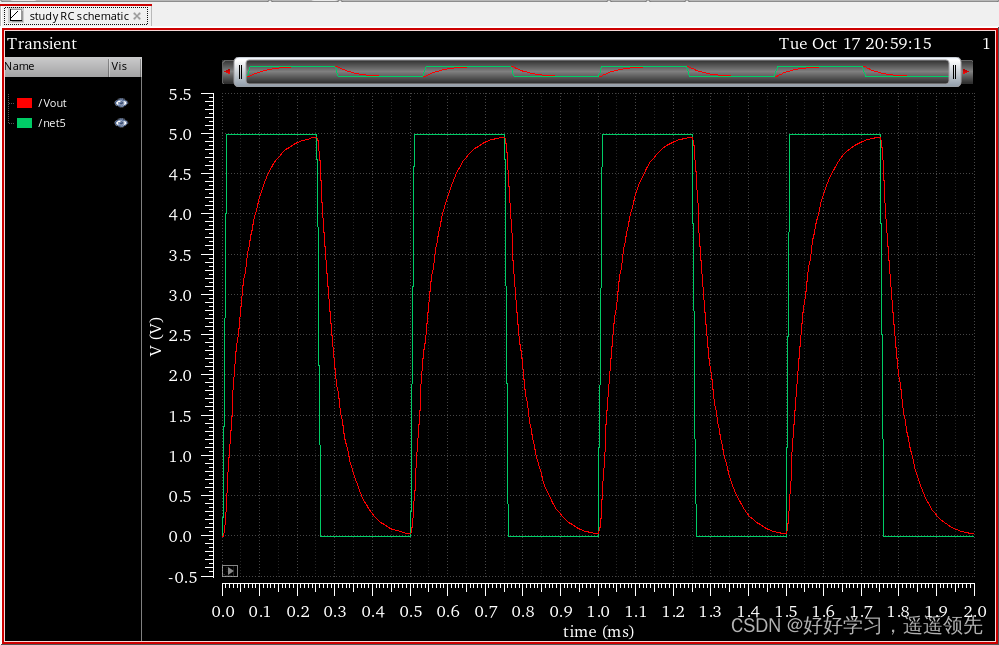

3、tran仿真结果

绿色线是输出方波(vpulse中的参数设置),红色线是输出Vout。可以看到当输入从0-5V突变时,由于C的存在,输出并没有从0突变到5V,而是从0开始增加到一个最高值V0(这个值最大是5V,但并不一定能达到,这里大概有4.7V)。当输入从5-0V突变时,由于C的存在,输出并没有从V0突变到0V,而是从V0逐渐减小。

理论分析部分讲到了时间常数=RC,它反应电路中相应变化的快慢,时间常数越小,则电路相应变化越快,反之则越慢。这里可以看成电容C充放电的速度。我们相应的改变电阻R的值,从而使时间常数

发生改变,研究输出结果的变化。

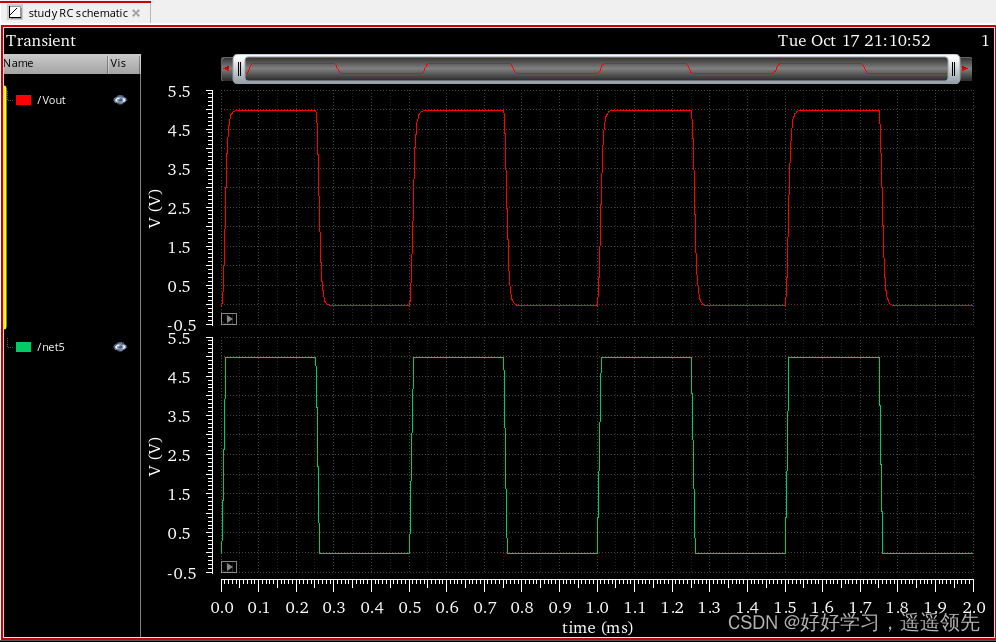

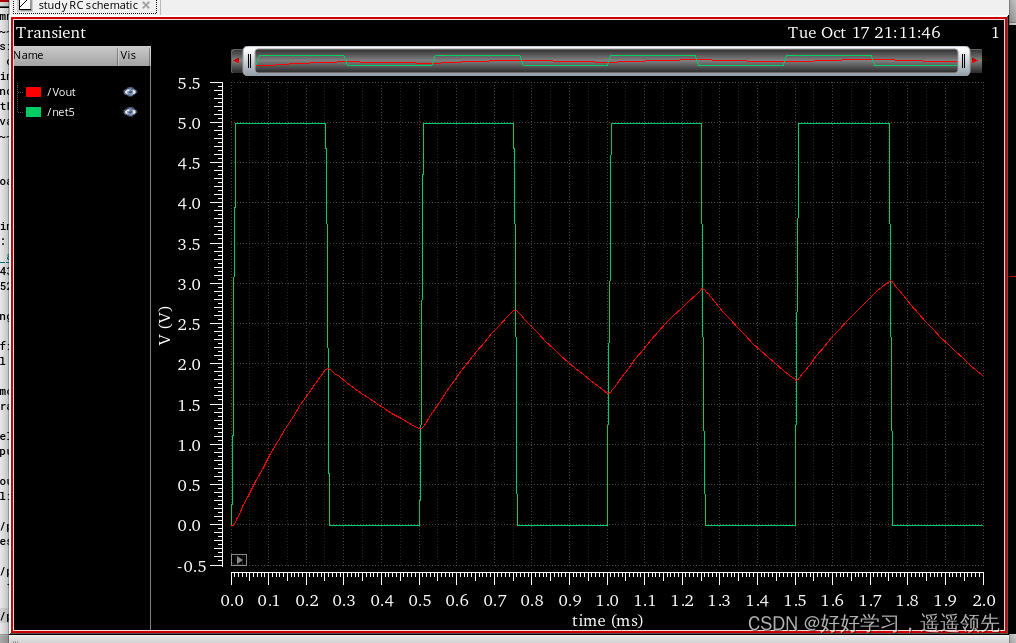

取R=10Ω、100Ω、10KΩ,分别得到输出结果图像(图像按电阻取值顺序排列):

不难看出,当R的取值减小时,输出波形逐渐与输入相同;当R取值增大时, 输出波形与输出逐渐不同,并且上述Vout所能达到的最大值V0随R(其实是=RC)的增大逐渐减小。印证了理论分析部分的结论:时间常数越小,则电路相应变化越快(这里的变化指的是VOut电压的变化,也可以看成是电容的充放电速度)。

4、AC仿真

4.1仿真环境设置

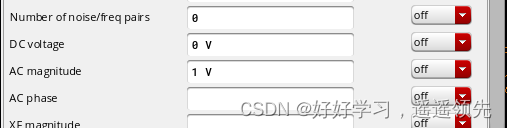

将tran仿真所用的vpulse替换成vsin(也是在analogLib库中),对vsin进行参数设置。AC magnitude设置为1V ,DC voltage设置为0V。这里电压值的设置我觉得影响不大,因为在交流通路中直流电压DC交流短路。AC magnitude是交流电压的幅值。

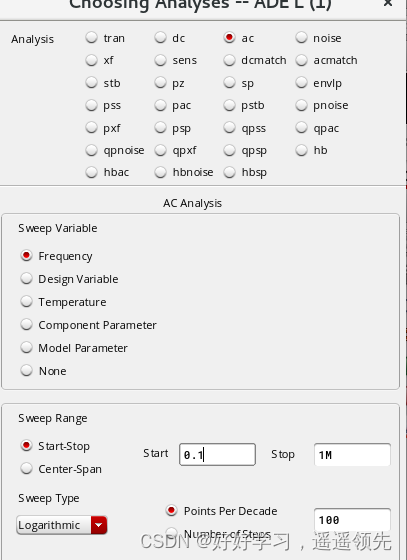

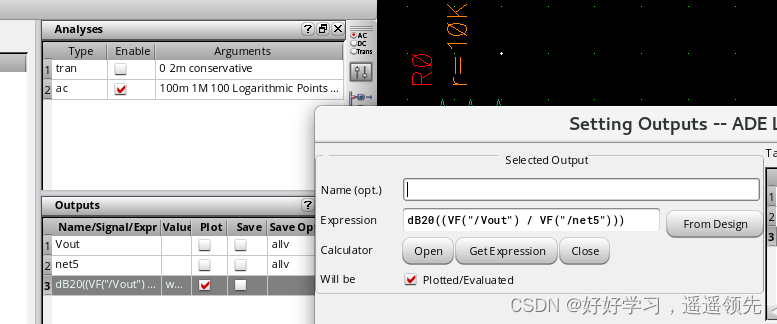

在仿真器ADE L中添加ac仿真,变量选择频率Frequency,变化范围0.1M-1M。 Sweep Type(仿真方式)选择points per decade——表示每10倍频中会扫描的点数,将其设置为100。Number of steps表示仿真的总点数,如果选择这种扫描方式,在低频处扫描到的点数可能会很少,曲线会降落的很快,影响仿真结果的准确性。

添加输出:在tran仿真中输出选择的是输入电压和输出电压,在AC仿真时我们想要观察其增益随频率 f 的变化,因此输出是 “输出电压 / 输入电压”。可以自己手动输入表达式(下图右方expression处),也可以通过calculator去设置,(“输出电压”和“输入电压”具体的name就是tran仿真中勾选的那两项,下图左下方的前两个)。

4.2、仿真结果

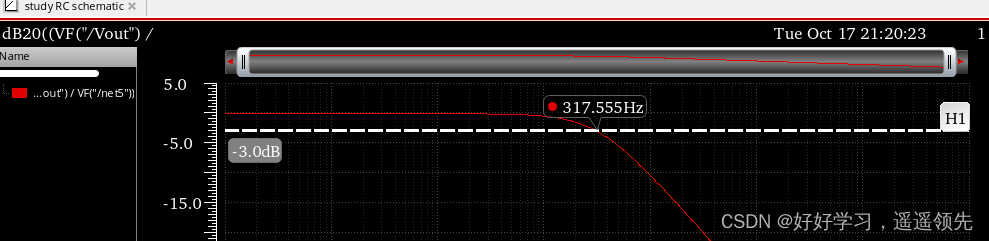

仿真环境设置好以后,直接点击仿真按钮即可,不用再添加工艺文件(因为用的是理想器件),如果仿真没有出结果可以在仿真前保存一下,再进行仿真。仿真结果如下图所示,一定频率内增益不随输入频率的变化而变换,但当频率超过一个特定的值后,增益开始随着频率的增加而下降。工程上提出了截止频率 f(-3dB)的概念,它表示增益下降到初始值的0.707时所对应的频率。f与RC的关系可表示为f = 1/2ΠRC。

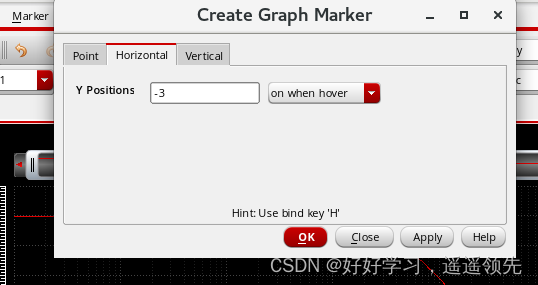

为了显示截止频率 f 的位置,可以在导航栏中点击Marker-Creat Marker,之后按图进行设置,输入Y的值为-3,点击OK即可。

不难看出,当增益为-db时,截止频率 f = 317.555Hz。可以根据 f 的表达式理论计算可得 f≈318.3Hz。

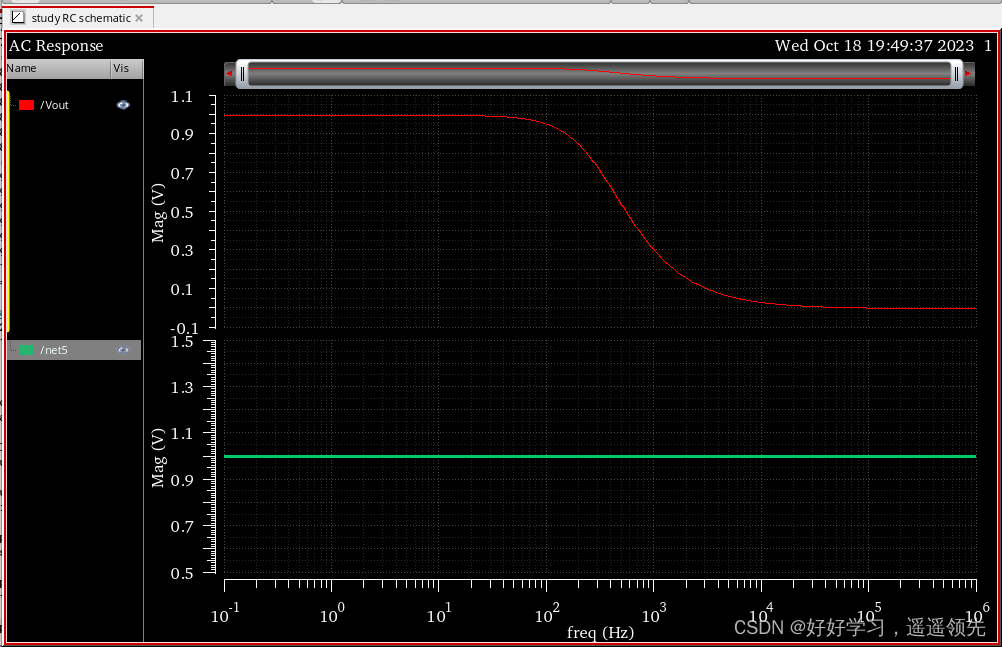

我们也可以把输出换成tran仿真时所用的输出输出电压,仿真结果如下图所示:低频时输入=输出=1V,当 f 超过一定值后,VOut开始下降。整个过程中Vout一直 ≤ Vin,所以在求增益时Av=dB20 log(Vout / Vin) ,曲线从0db开始下降。

4.3、RC的值对 f 的影响

4.3、RC的值对 f 的影响

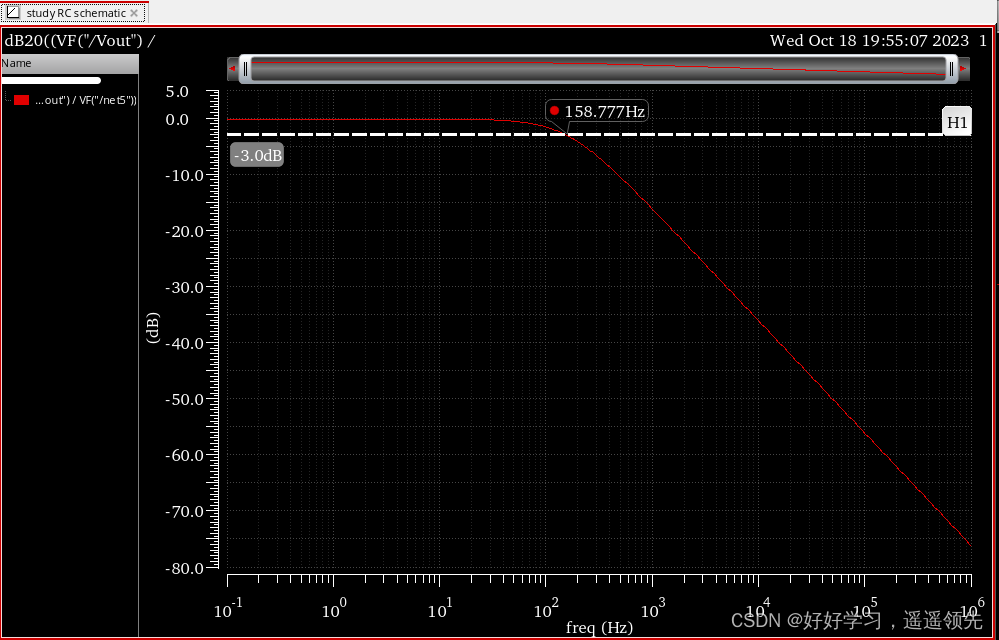

理论上 f 与RC的关系可表示为 f = 1/2ΠRC,RC增大,f 的值会减小。在电路图中,改变R或C的值可以改变RC的乘积值。以改变R=20K为例进行仿真,结果如下:

可以看到,此时 f =158.777Hz。不难分析出,当R由10K变为20K时,截止频率变为原来的1/2,与理论相符合。同样的,可以改变C的值进行分析 。

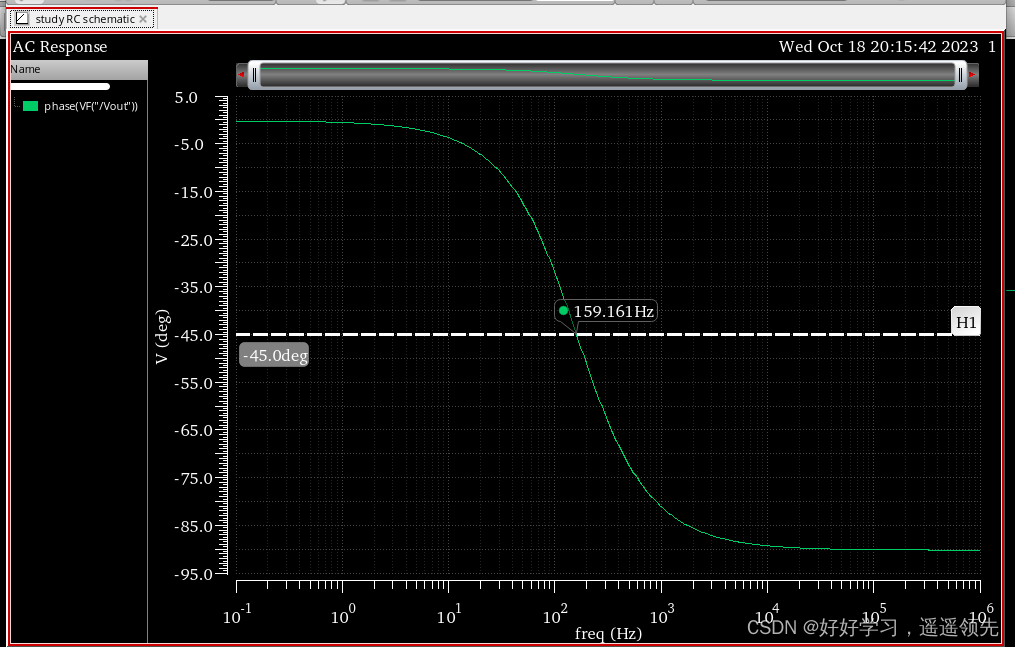

4.4、相位的变化

上面我们分析了增益随 f 的变化。我们知道通过传输函数H(s)可以得到幅值和相位,这里我们就来分析一下相位的变换。理论上来说,当输入频率超过一个特定的值后,Av开始下降,相位也随着改变。在截止频率处,增益下降为原来的0.707倍,此时相位改变45°;之后,再随着频率 f 的增加,相位继续改变,对于一阶RC网络,只有一个极点,相位最高改变90°。(这一块内容可以自己去学习)。以下仿真结果可以看出,当相位改变45°时,对应的输入频率 f1 = 1591.61Hz。上面在分析增益时得出的截止频率为 f0 = 158.777Hz(此时电路用的是R = 20K)。可以看出 f1≈f0。

此次记录就到此为止,鉴于自己知识水平和文字能力有限,有些地方表达的不是很清楚或出现错误,还请大家批评指正。

博主在学习模拟集成电路中一阶RC网络知识后进行仿真调试并记录结果。先进行理论分析,包括时间域和频域;接着开展仿真,涵盖电路搭建、ADE L设置,分析tran和AC仿真结果,研究RC值对截止频率的影响以及相位变化。

博主在学习模拟集成电路中一阶RC网络知识后进行仿真调试并记录结果。先进行理论分析,包括时间域和频域;接着开展仿真,涵盖电路搭建、ADE L设置,分析tran和AC仿真结果,研究RC值对截止频率的影响以及相位变化。

5379

5379

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?