前言

在学习时训练如何自定义IP核心,在网络上搜索流程发现大部分都是Vivado的自定义流程,所以在成功创建我的串口收发IP后用博客来记录一下具体流程。

流程

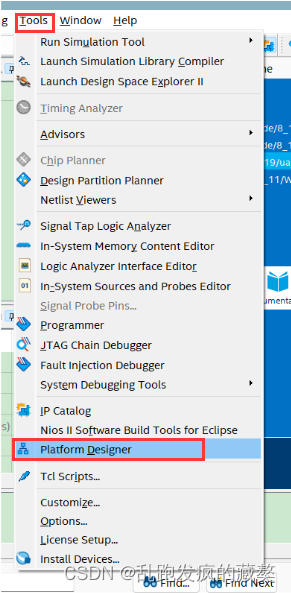

1.首先我们使用的是Quartus中的Platform Designer来创建我们自己的IP核,我们根据下图点击进入界面。

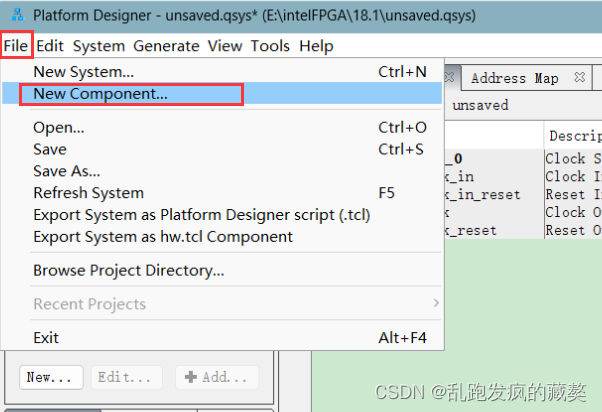

2.然后点击下方图片的红色方框选项

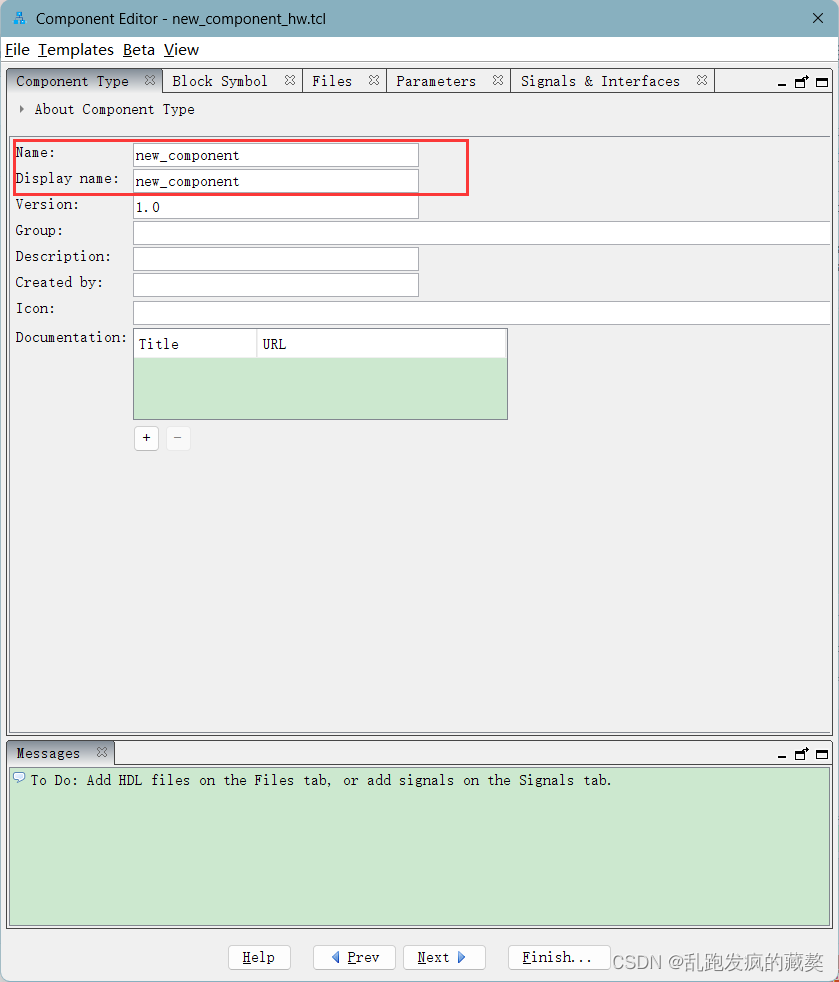

3.我们进入创建界面,我们在以下界面输入我们IP核的名字

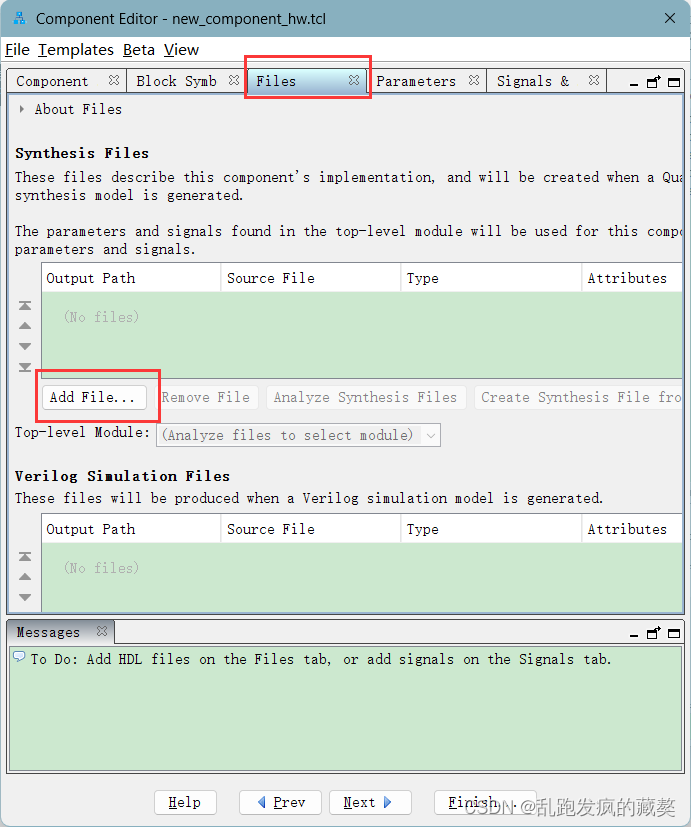

4.然后我们选择Files来添加我们的IP核源文件

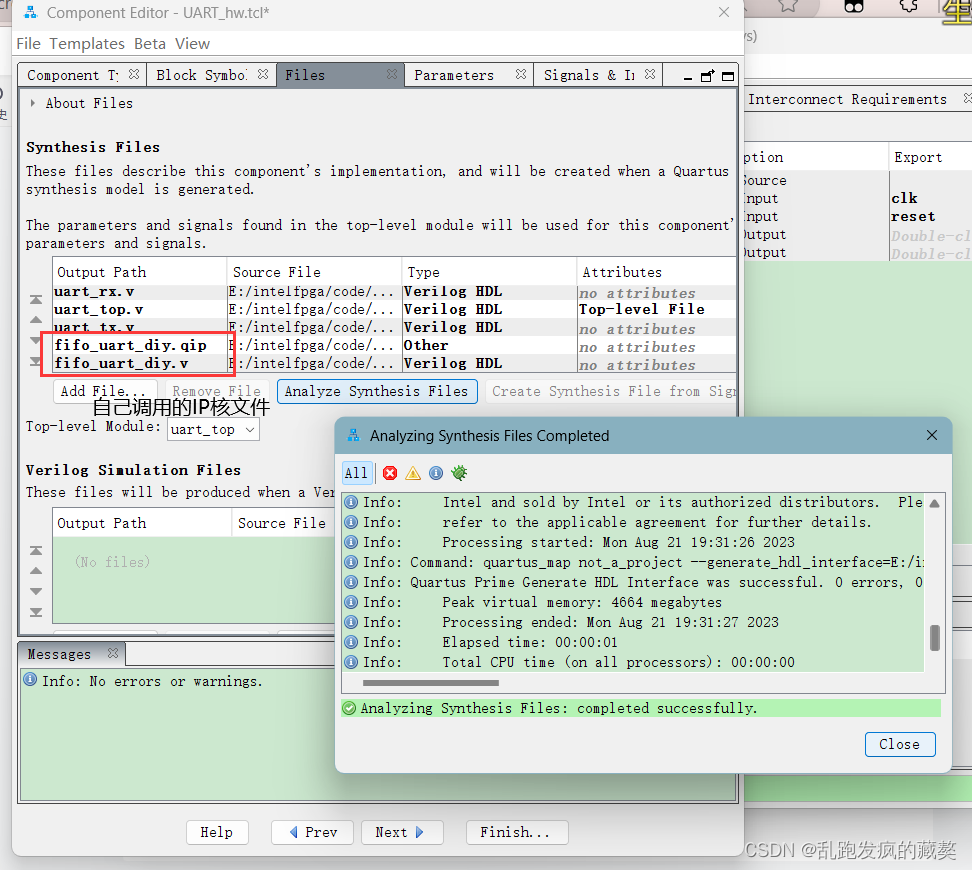

5.选择好后我们选择编译分析我们的添加的源文件(注意,如果我们的工程中调用了IP核也记得一定要把我们添加的IP核的.v文件添加进来)

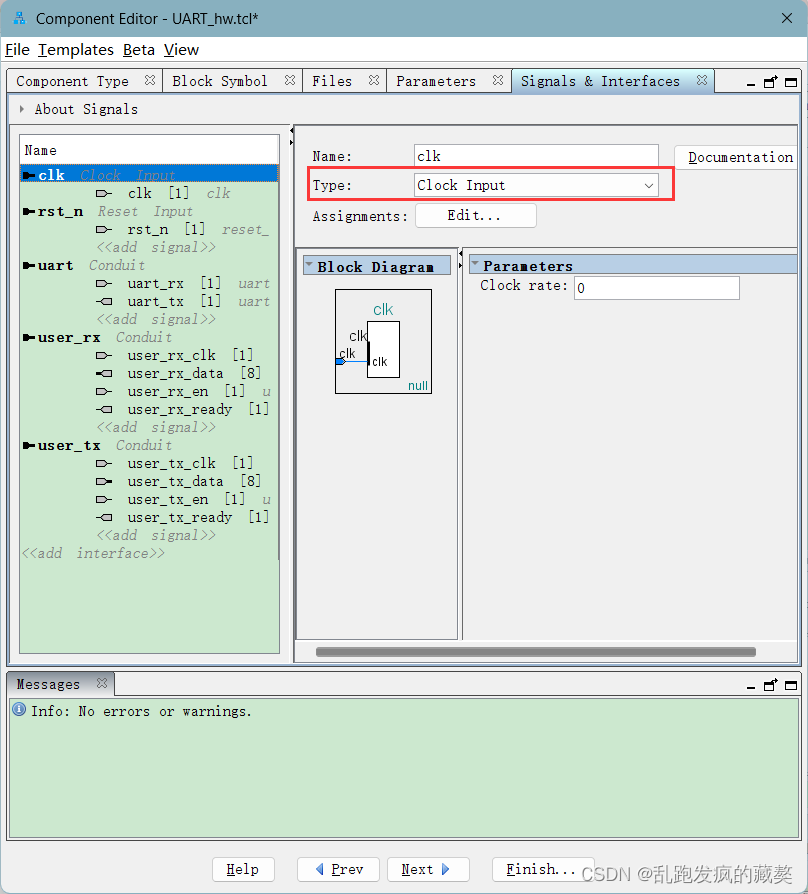

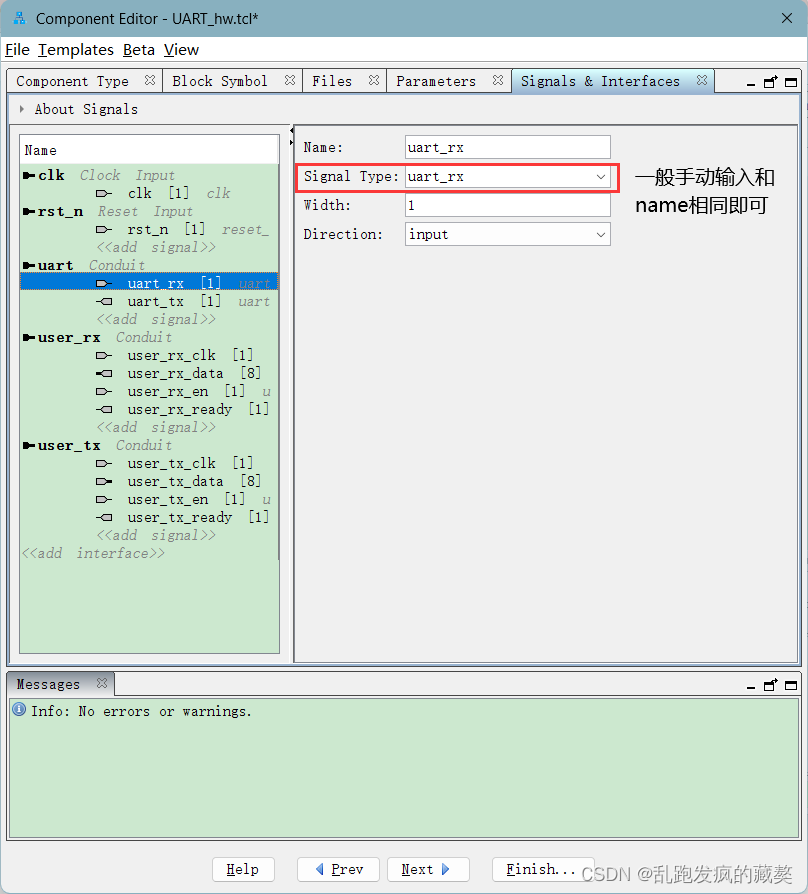

6.然后我们进入Signals & Interfaces来设置我们的信号

这是我们的时钟信号,我们设置好后,需要把其他类别块都选择我们设置的时钟

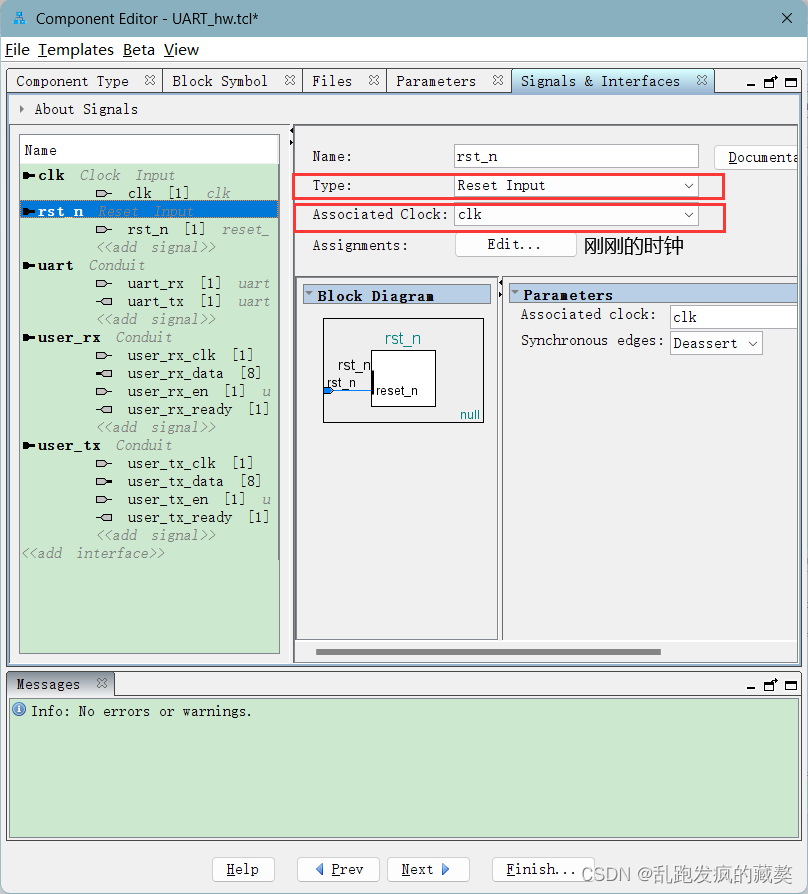

接下来是我们使能信号,创建好了后将使能信号拖入该类别

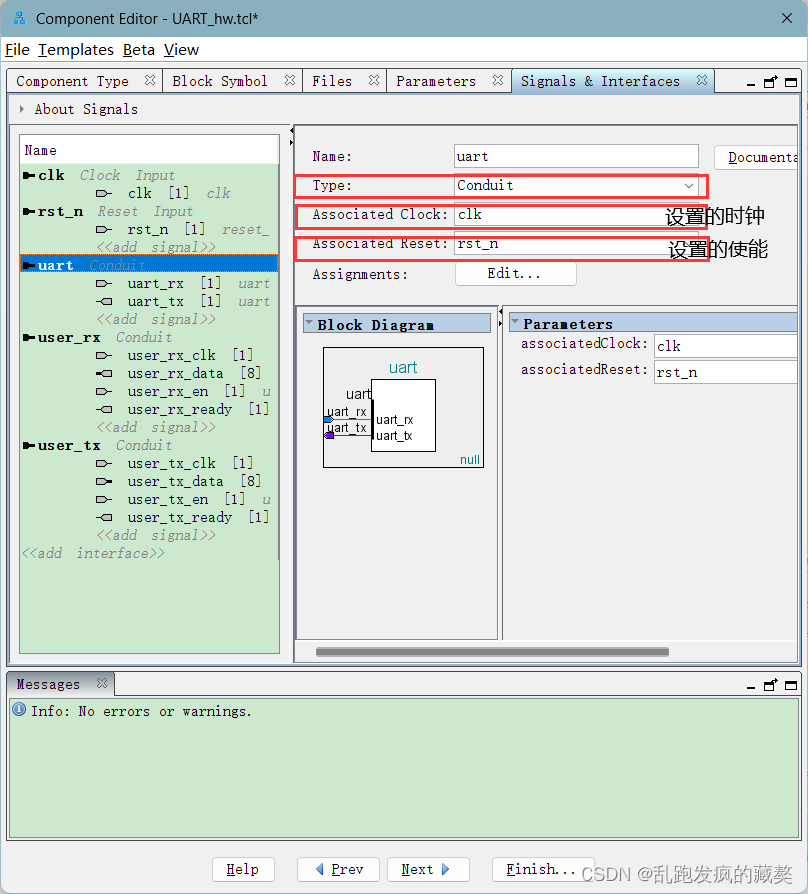

对于我们使用的其他信号我们统一选择Conduit类别,为了美观区分我们可以多创建几个Conduit块这样可以更加直观区分不同功能的信号。

一般对于单个信号的设置我们一般如下图设置,我们把Conduit下的信号的类型直接手动输入成我们name的相同名称即可,在设置后我们的inst中信号后的注释会显示为Signal Type的值,但是切记不要使用中文,使用中文会出现超出数组的报错(可能是笔者使用太多,但最好就和name相同),还有一点需要注意的就是clk和rst_n的信号是如上面的图选择对应的值,并不是我们手动输入的;对于类别块这些的Name可以自己修改,但是还是最好不要使用中文,否则可能出现一些奇怪的报错

设置好后如果massages显示如上图即可点击Finish,如果出现一些报错可以去这个博主的文章下面看看是否可以解决:Quartus 18.1 PD平台封装IP核_quartus怎么封装_吨吨吨2333的博客-CSDN博客

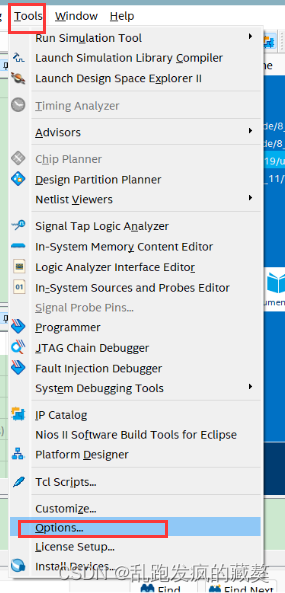

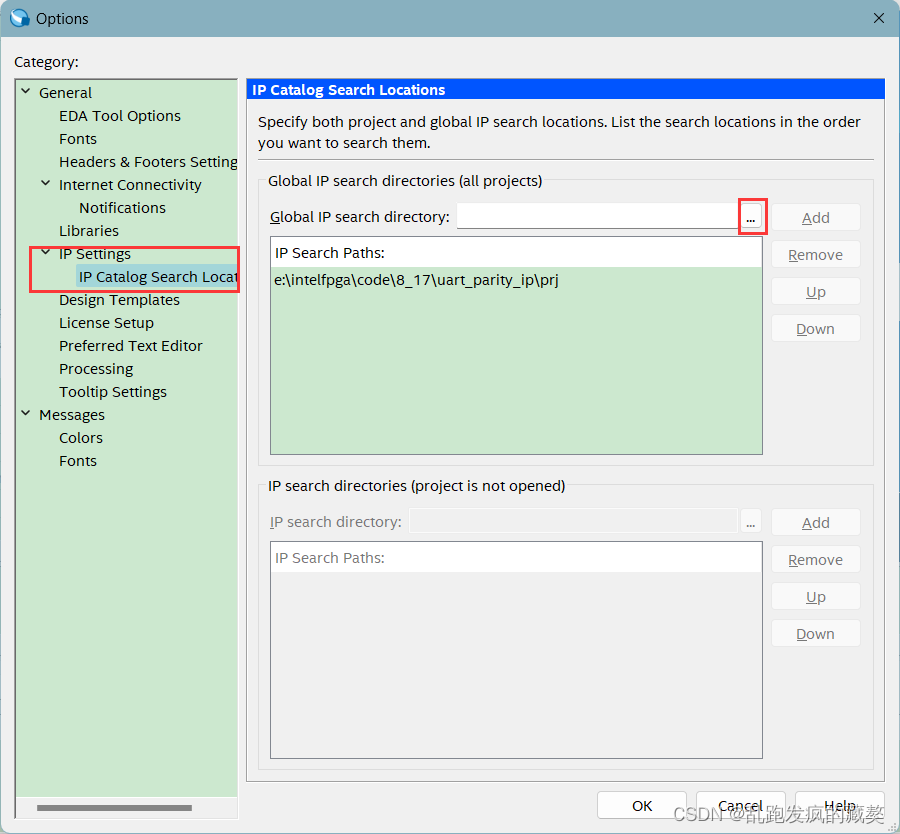

7.然后我们这就属于创建好了我们自己的IP,然后我们来添加路径

根据红色方框操作,我们只需要选择存放我们工程的prj目录即可

这样我们就能发现我们的IP成功的出现在了IP核的界面中

接下来我们来演示一下调用:

调用自定义IP

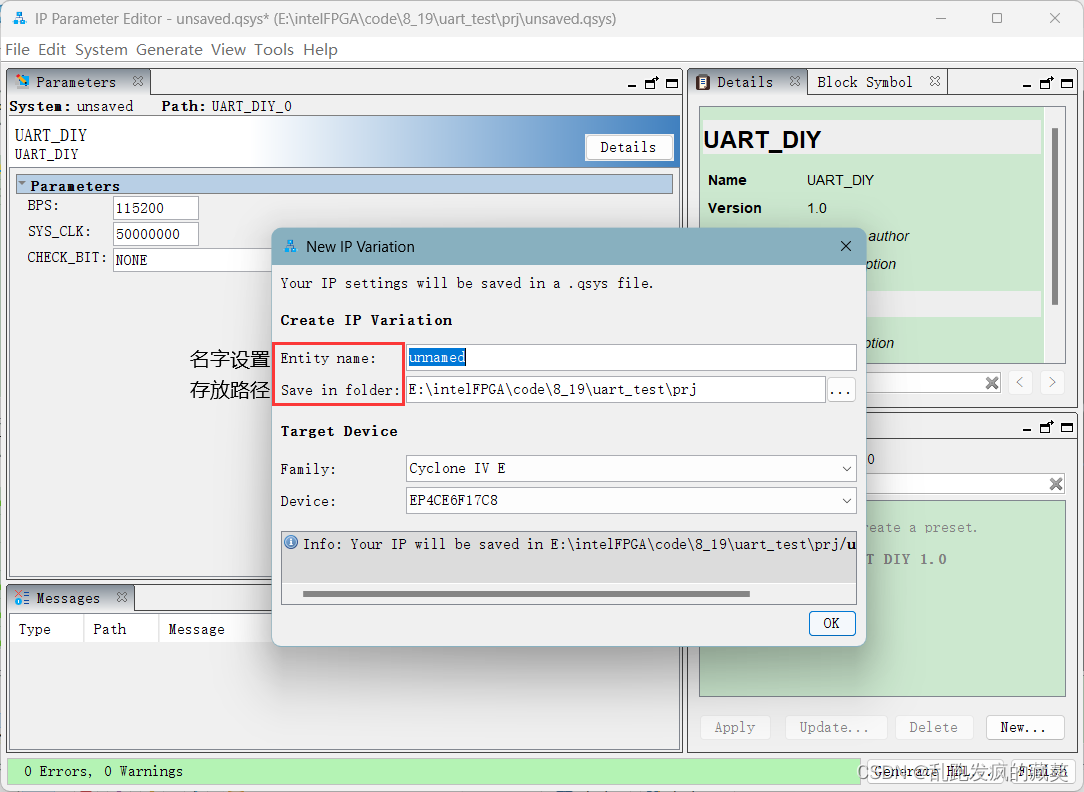

1.双击我们刚刚创建好的IP核

可能会有些读者没有哪个OK,我们只需要把这个窗口拉大一点即可

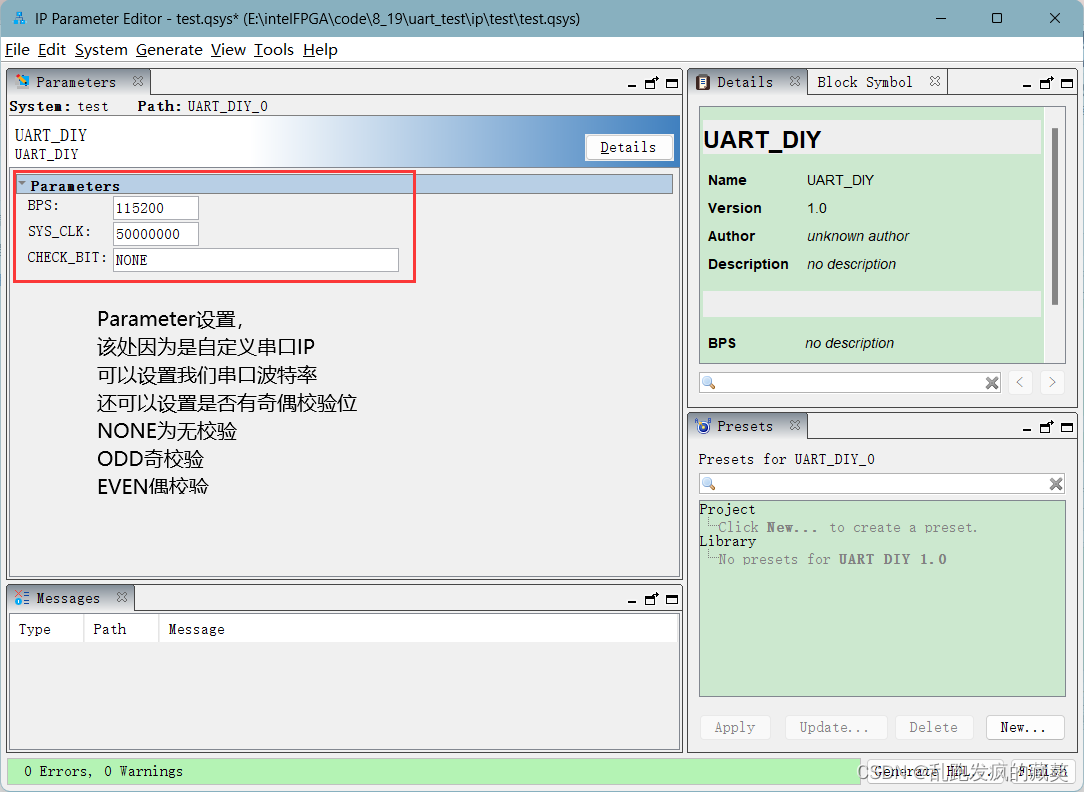

2.常量设置

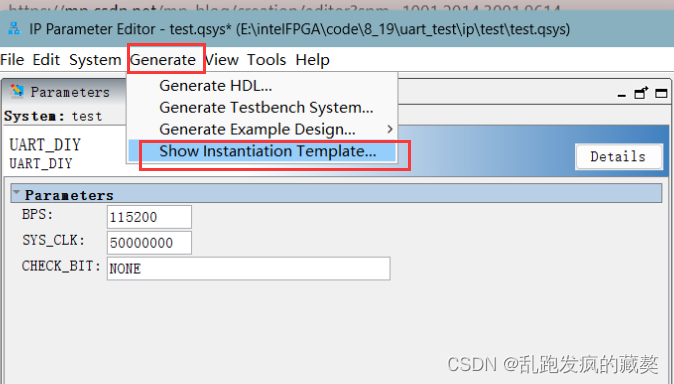

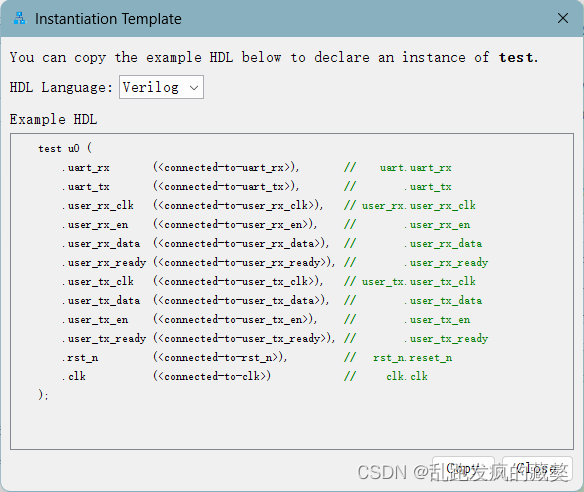

3.例化模板复制

点击进入后我们可以看到我们的例化模板,直接复制到我们要使用的地方填入信号即可

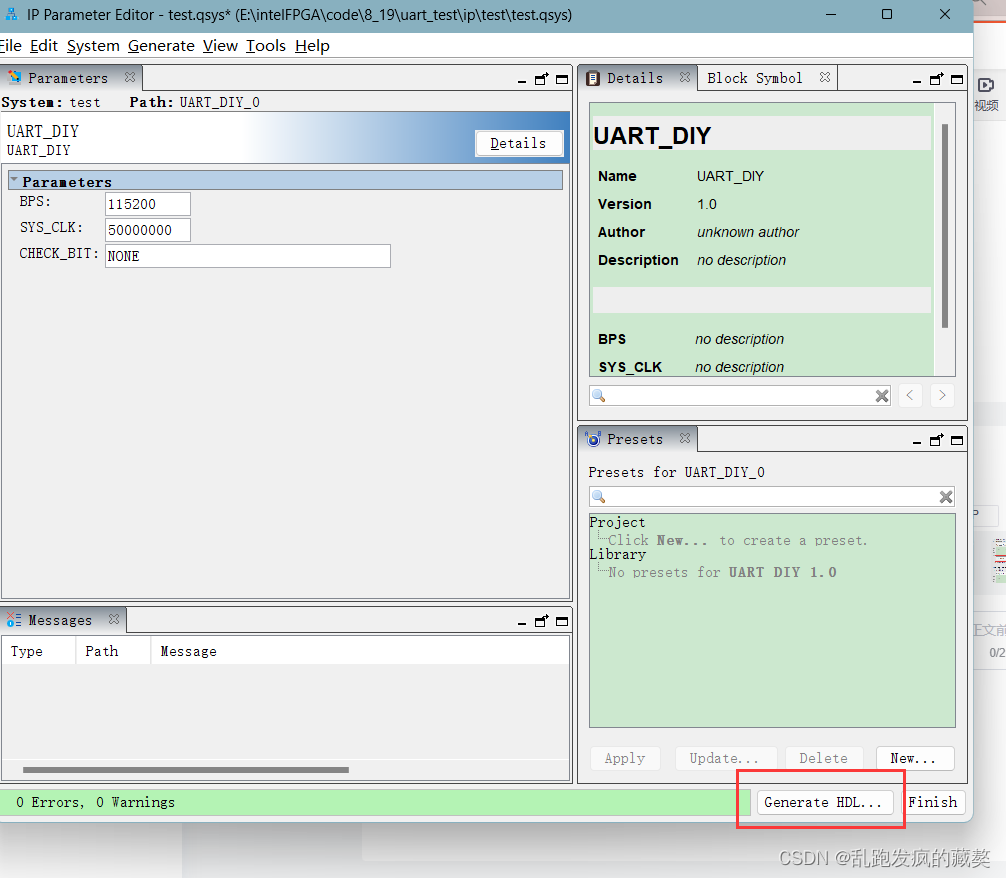

4.生成HDL

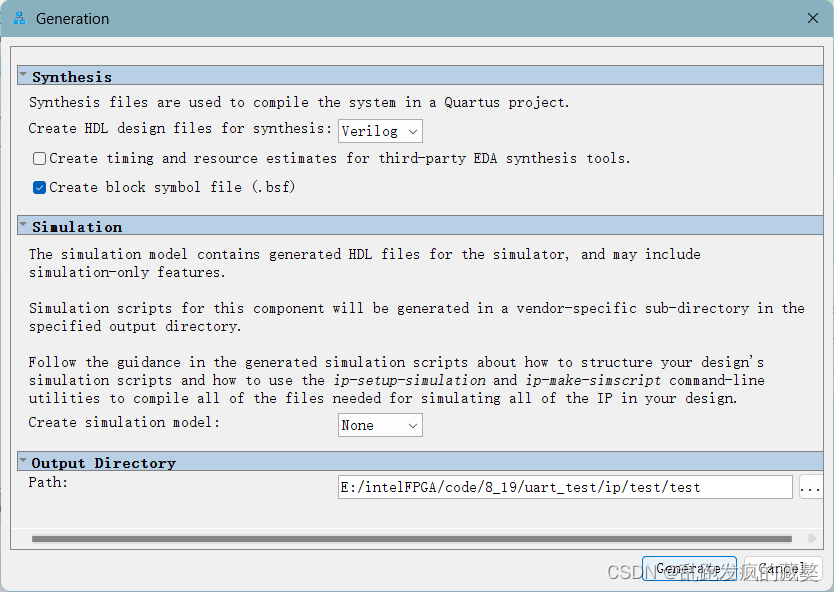

点击红色方框按钮,出现以下窗口

我们不需要管,一般默认即可,点击右下角创建

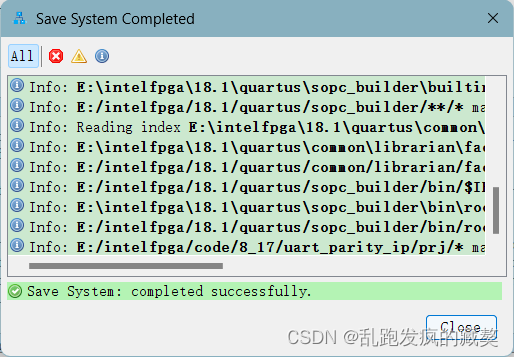

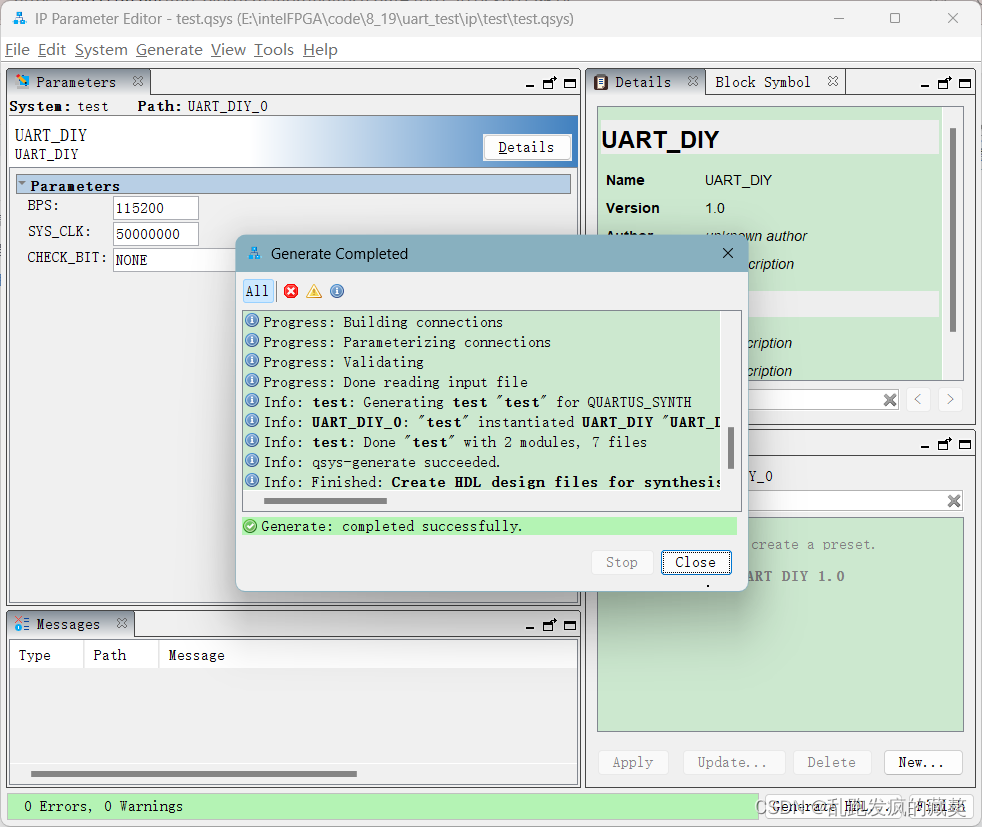

显示该界面一般就是成功了,我们close掉窗口

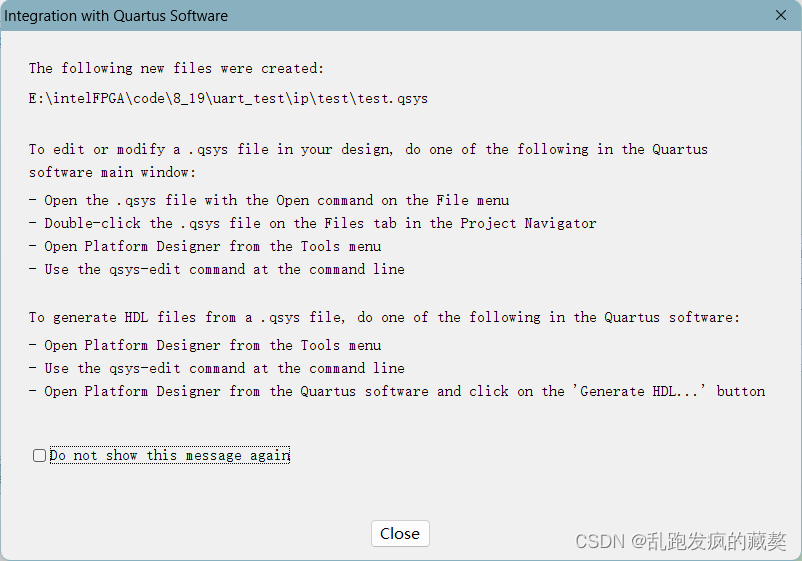

然后加载完成显示成功后我们close掉窗口,然后点击finish,会显示以下界面

我们直接Close即可

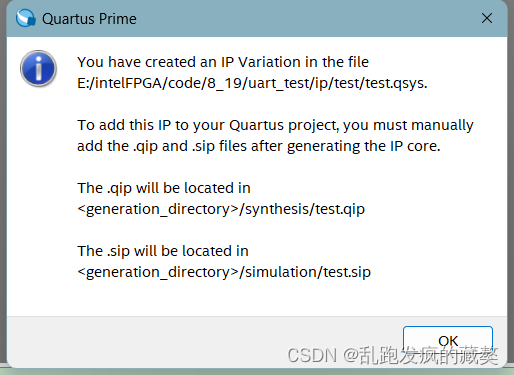

然后quartus出现弹窗

我们也直接OK

然后我们便成功创建了我们的自定义IP核,然后我们直接把IP核路径下的.qsys文件添加进工程即可正常调用编译!

ps:这里讲一些注意事项,比如我这个串口IP中调用了FIFO,如果我们工程中也调用了FIFO的话我们对于FIFO的名字需要做出区别,不然就会出现因为设置不同的调用错误,我们也可以对自定义IP中的这些命名复杂一些,这样可以规避我们命名相同造成编译错误。

然后还有就是我们自定义的IP核中添加的那些文件的命名也需要对我们当前工程的名字作出区分,不然也会出现意料之外的编译错误,比如该工程太复杂(自己和自己循环相连),解决方法也可以使用上方第一个注意的方式。

谢谢观看!!!

博主记录了在Quartus中自定义IP核的具体流程,包括使用Platform Designer创建IP核,设置信号、添加路径等步骤,还演示了调用自定义IP核的方法,如常量设置、例化模板复制等,同时给出了避免编译错误的注意事项。

博主记录了在Quartus中自定义IP核的具体流程,包括使用Platform Designer创建IP核,设置信号、添加路径等步骤,还演示了调用自定义IP核的方法,如常量设置、例化模板复制等,同时给出了避免编译错误的注意事项。

3599

3599

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?