前言

出笔试题汇总,是为了总结秋招可能遇到的问题,做题不是目的,在做题的过程中发现自己的漏洞,巩固基础才是目的。

所有题目结果和解释由笔者给出,答案主观性较强,若有错误欢迎评论区指出,资料整理来自于“数字IC打工人”等数字IC相关公众号,牛客网等网站真题、网络笔试真题及面经抄录。

保持更新(2023.9.25)文章内含 单选题270道、多选题106道、填空题16道、判断题17道、简答题72道、逻辑推理题3道、C语言 python 脚本编程题8道。

在本文中笔者提供的所有代码,都写成了API,可直接copy到软件编译、运行、给出结果。

题目较多,即使有前人解析和强大的ChatGPT,也难免出错,若发现错误,欢迎评论区讨论。

另外夹带一点私货~: 这一刻,我感觉一定要给.....

数字IC笔试千题解总字数已到达15w+,网页码字卡顿情况严重,故将其分割成多个部分以方便维护,链接如下:

数字IC笔试千题解--单选题篇(一)

数字IC笔试千题解--单选题篇(二)

数字IC笔试千题解--多选题篇(三)

数字IC笔试千题解--填空题篇(四)

数字IC笔试千题解--判断题篇(五)

数字IC笔试千题解--简答题篇(六)

数字IC笔试千题解--逻辑推理篇(七)

数字IC笔试千题解--编程&&脚本篇(八)

填空题

-

verilog 当中 a=4’b10x1;b=4’b10x1;那么逻辑表达式 a==b 为_______ a===b 为________

答案:x,1

相等运算符(==):参与比较的两个操作数必须逐位相等,其相等比较的结果才为 1, 如果某些位是不定态或高阻值,其相等比较得到的结果是不定值。

全等运算符(===):全等比较是对这些不定态或高阻值的位也进行比较,两个操作数必须完全一致,其结果才是 1,否则结果是 0

逻辑运算符可参考笔者其他文章:Verilog 逻辑与(&&)、按位与(&)、逻辑或(||)、按位或(|)、等于(==)、全等(===)的区别

2. 4bit 的信号输入和 8bit 的信号输入的乘法器内部计算输出信号至少需要______ bit 的位宽

答案:4bit信号的最大值为4'b1111 = 15, 8bit信号的最大值为8'b1111 1111 = 255;

乘积输出最大值为:255 * 15 = (2^4 - 1) * (2^8 - 1) = 2^12 - 2^8 -2^4 + 1,至少需要12bit位宽。

改一下题目:3bit信号输入和4bit信号输入的乘法器输出至少需要多少bit位宽?

max_output = 3'b111 * 4'b1111 = 7 * 15 = (2^3 - 1) * (2^4 - 1) = 2^7-2^4-2^3+1,用7bit即可描述,得出结论,X bit信号输入和 Y bit信号输入的乘法器输出信号至少需要(X+Y)bit。

3. 通常情况下, 芯片工作温度较________, 工作电压较_______ , 速度最快。

答案:电子迁移率主要受晶格散射影响,即随温度升高迁移率下降,芯片工作温度较低,则速度较快。芯片供电电压影响到电容充放电速度,电压降低时,芯片会变慢,电压升高时,芯片会变快。

4.以下代码的打印输出是___________

always@(posedge clk) begin

a=0;

a<=1;

$display(“%0b”,a);

end

答案:0,同一时刻阻塞赋值和非阻塞赋值发生,以阻塞赋值结果为准。

5. 全部使用组合逻辑实现 A, B, C 的运算实现|A*(B+C)|^2 共需使用_______ 个乘法器与_______个加法器

答案:6个乘法器,5个加法器

此题:设A = Ar + Ai*j, B = Br + Bi*j, C = Cr + Ci*j,

A*(B+C) = (Ar*(Br+Cr) - Ai*(Bi+Ci)) + (Ai*(Br+Cr) + Ar(Bi + Ci))*j,令Br+Cr = Dr, Bi+Ci = Di;

则,要求的是复数的模的平方,|A*(B+C)|^2 = 实部的平方 + 虚部的平方 = (Ar*(Br+Cr) - Ai*(Bi+Ci)) ^ 2 + (Ai*(Br+Cr) + Ar(Bi + Ci)) ^ 2

= Ar^2*(Dr^2 + Di^2) + Ai^2*(Di^2 + Dr^2) ,其中Br+Cr = Dr, Bi+Ci = Di;

乘法器使用:Ar*Ar;Ai*Ai;Dr*Dr;Di*Di;Ar^2*(Dr^2 + Di^2);Ai^2*(Di^2 + Dr^2);6个乘法器

加法器使用:Br+Cr;Bi+Ci; Di^2 + Dr^2;Ar^2*(Dr^2 + Di^2) + Ai^2*(Di^2 + Dr^2) ;4个加法器

6. [Python] list1 = [0, 1, 2, 3, 4, 5],则list1[ : -2]=___

答案:[0,1,2,3]。考察python语法。

7.退出仿真的函数是哪个____

答案:$finish。

8. UVM中哪个phase是自下而上执行顺序?____

答案:build_phase

在 UVM 中,build_phase 是自下而上执行的 phase,也是 UVM 中最先执行的 phase。build_phase 用于创建和连接测试组件,其执行顺序与 testbench 中组件的继承关系相关,一般从下往上依次执行,即先创建和连接最底层的组件,再依次向上创建和连接其它组件。在 build_phase 中,我们可以使用 UVM 提供的各种工厂和配置机制,动态地创建测试组件并进行配置,以满足测试需求。

9.某一数模转化器的精度为6位,电压转换范围为0-6.3V,那么当输入数字信号为011011的时候,输出电压是( )V

答案:2'b011011转十进制等于16+8+2+1=27,即2.7V。

10.在进行256点FFT分析时,如果信号采样率为4096Hz,那么FFT变换之后的频谱分辨率为( )Hz。

答案:4096/256=16,分辨率为16Hz。

11.以下verilog代码实现了( )分频(注意:填阿拉伯数字)

module div(

input clk ,

input rst ,

output clk_ out

);

reg [1:0]cnt1;

reg [1:0]cnt2;

reg c1k1;

reg clk2;

always@(posedge clk or negedge rst_n)

if(!rst_n)

begin cnt1<=2' b00;

else if(cnt1==2'b10)

cnt1<=2'b00;

else

cnt1<=cnt1+1'b1;

always@(negedge clk or negedge rst_n)

if(!rst_n)

cnt2<=2 'b00;

else if(cnt2==2'b10)

cnt2<=2'b00;

else

cnt2<=cnt2+1'b1;

always@(posedge clk or negedge rst_n)

if(!rst_ n)

c1k1<=1'b0;

else if(cnt1==2'b00||cnt1==2'b10)

clk1=~clk1;

else

clk1<=clk1;

always@(negedge clk or negedge rst_n)

if(!rst_ n)

clk2<=1'b0;

else if(cnt2==2'b00||cnt2==2'b10)

clk2<=~clk2;

else

clk2<=clk2;

assign clk_out=clk1&clk2;

endmodule答案:clk1和clk2都是占空比为66%的三分频,clk2错开clk1半个周期,两者相与输出占空比为50%的三分频。

12.考虑如下所示的计算机指令:

Loop:

fld f0,0(x1)

fadd.d f4,f0,f2

fsd f4,0(x1)

addi x1,x1,-8

bne x1, x2, Loop已知fld指令需要2T的时间,fadd.d需要3T的时间,fsd, addi, bne个需要1T的时间,那么通过指令的重新排布,完成上述单次Loop所需的最少时间为( )T

答案:

-

fld f0,0(x1):从内存中以x1为基地址,偏移量为0的位置(也就是x1指向的位置)读取一个双精度浮点数,存入浮点寄存器f0中。

-

fadd.d f4,f0,f2:将f0寄存器中的值和f2寄存器中的值相加,结果存入f4寄存器中。

-

fsd f4,8(x1):将f4寄存器中的值存储到以x1为基地址,偏移量为8的内存位置中。

-

addi x1,x1,-8:将x1寄存器中的值减去8,即将x1寄存器指向前一个双精度浮点数所在的内存地址。

-

bne x1,x2, Loop:比较x1寄存器的值和x2寄存器的值,如果不相等,跳转到Loop标签处执行。

观察指令可以发现,fld指令需要等待访存,fadd.d指令需要等待fld指令的结果,fsd指令也需要等待fadd.d指令的结果。因此,可以采用指令重排的方法来减少总的执行时间。

一种可能的指令重排方式如下:

Loop:

fld f0,0(x1)

addi x1,x1,-8

fadd.d f4,f0,f2

fsd f4,8(x1)

bne x1,x2,Loop指令重排后,fld指令和addi指令可以并行执行,fadd.d指令等待fld指令的结果,fsd指令等待fadd.d指令的结果。因此,单次Loop所需的最少时间为:

2T (fld和addi并行执行) + 3T (fadd.d执行) + 1T (fsd执行) + 1T (bne执行) = 7T

因此,完成上述单次Loop所需的最少时间为7T。

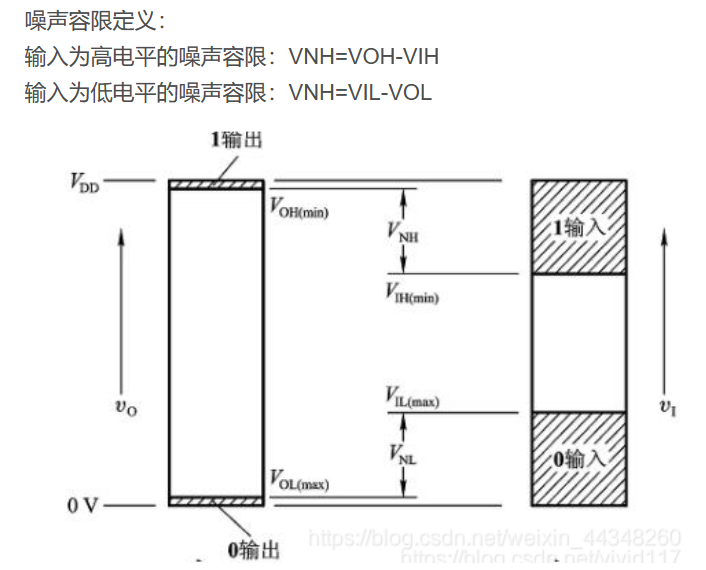

13.已知VIL_max为最大允许输入低电平,VIH_ min为最小允许输入高电平,VOL_max为最大输出低电平,VOH_min为最小输出高电平,则输入高电平的噪声容限VNH=( )V

电路类型 电源电压 VIL_max VIH_min VOL_max VOH_min

CMOS 3.3V 1.1V 2.2V 0.1V 3.2V

答案:1V,如下图:

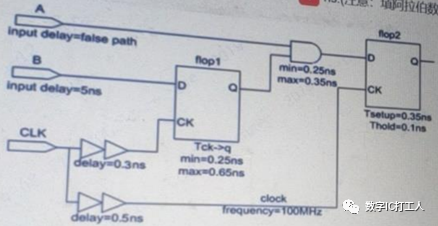

14.下图的电路中,flip-flop 2的setup time slack= ( ) ns.(注意:填阿拉伯数字)

答案:0.3+0.65+0.35+T_slack = 0.5+10-0.35算出T_slack=8.85ns。

15.某一异步FIFO,写时钟频率为200MHz,每100个周期会写入30个数据,读时钟频率为100MHz,每10个周期可以读出7个数据,则此FIFO的最小深度为( ).(注意:填阿拉伯数字)

答案:容易算出,读的速度比写的速度快,所以FIFO不会溢出。写的30个数据,占写时钟的30周期,对应读时钟的15周期。读时钟的15周期最少读出9个数据,所以FIFO最小深度为21。

以下system verilog代码,到55ns时执行了( )次打印(注意:填阿拉伯数字)

initial begin

$display("start");

#10 $display("test");

fork

$display("test");

#50 $display("test");

#10 $display("test");

begin

#30 $display("test");

#10 $display("test");

end

join_any

$display("test");

#80 $display("test");

end答案:7次打印.

1. fork-join语句会等待所有子程序都执行完毕后再继续执行后续代码。当所有子程序都完成后,join语句才会返回。

2. fork-join_any语句会等待至少有一个子程序执行完毕后就会继续执行后续代码。当有一个子程序完成后,join语句就会返回。

3. fork-join_none语句不会等待子程序执行完毕,而是直接继续执行后续代码。这种语句常用于一些无需等待子程序执行完毕的情况。

16.以下verilog代码的印出的值为( )

reg signed [7:0] a, b, c;

initial begin

a=8'h14;

b=8'b11110010;

c=a+b;

$display("%d",c);

end答案:6。b=8'b11110010,有符号位为补码表示,按位取反加1得到b=-14。a=20,所以20-14=6。

17.已知八进制数: (362) 8,求它的

十进制数是:

二进制原码是:

反码是:

补码是:

十进制数:3*8^2+6*8+2=192+48+2=242

二进制原码是:242一直除以2求余。

242/2=121...0

121/2=60 ...1

60 /2=30 ...0

30 /2=15 ...0

15 /2=7 ...1

7 /2=3 ...1

3 /2=1 ...1

1 /2=0 ...1

从下往上写,二进制原码为:11110010(B)

反码是:00001101

补码是:00001110

18.写出图中CMOS电路的输出逻辑表达式:Z1= 、Z2=

左图:不看B的情况下,容易看出A1和A2组成或非门,两者同时为0,则输出1。A1和A2的上拉网络和B并联,下拉网络和B串联。所以最后就是A1和A2的或非再与B与非,Z1=(B(A1+A2)')'=A1+A2+B'。

右图:ABC或非再接一个非门,也就是ABC的或,Z2=A+B+C。

19.Assuming a=1'b1; b=1'b0what's the final values of a and b?

| ① always@(posedge clk) begin a=b; b=a; end | ② always@(posedge clk) a=b; always@(posedge clk) b=a; | ③ always@(posedge clk) begin a<=b; b<=a; end | ④ always@(posedge clk) a<=b; always@(posedge clk) b<=a; |

| a= ? b= ? | a= ? b= ? | a= ? b= ? | a= ? b= ? |

1:阻塞赋值,a=0,b=0。

2:仿真结果为a=0,b=0。

3:非阻塞赋值:a=0,b=1。

4:非阻塞赋值:a=0,b=1。

20.Complete the blanks inthe following question with the appropriate answer.

There is a FIFO, at the input side, there will be atmost 80 valid input out of 100 cycles; at the output side there will be atleast 8 available slots out of 10 cycles, please specify what is the minimized FIFOdepth for this case. Depth=_________

答案:34。写数据100周期最多有80个valid,读数据10周期至少有8个有效,意味着最差情况FIFO也不会溢出。假设输入背靠背传输连续写入160个数据。输出前五周期读3个,最后五周期读3个,中间150周期读15*8=120个,所以写入80个数据,读出6+120=126个,FIFO深度为160-126=34。容易误判32深度。

21.逻辑简化:Y=B+(~A)&(~C) + (~B)&(~C)

Y=B+A'C'+B'C'=B(1+C')+B'C'+A'C'=B+C'+A'C'=B+C'

Y=B+C'

22.下图为组合逻辑Y=F(A,B,C,D)的真值表,请根据真值表,写出相应的逻辑表达式

| AB=00 | AB=01 | AB=11 | AB=10 | |

| CD=00 | 0 | 0 | 0 | 0 |

| CD=01 | 1 | 1 | 1 | 1 |

| CD=11 | 0 | 0 | 1 | 1 |

| CD=10 | 0 | 0 | 1 | 1 |

化简卡诺图,直接写出表达式:Y=C'D+AD+AC.

23.reg类型的初始值是____

答案:x类型。

24.wire类型的初始值是____

答案:z类型。

25. 4'b110x + 4'b0101 = ____

答案:4'bxxxx

26. 0xBE & ~0xFC << 0x02 | 0x01= ___________,其中:

0xBE = 8'b1011_1110;0xFC = 8'b1111_1100;0x02 = 8'b0000_0010;

答案:8'b0000_1101

取反~优先级最高,优先级:取反操作>移位操作>按位与操作>按位或操作

所以结果为:

0xBE & ~0xFC << 0x02 | 0x01

= 8'b1011_1110 & ~8'b1111_1100 << 8'b0000_0010 | 8'b0000_0001

= 8'b1011_1110 & 8'b0000_0011 << 8'b0000_0010 | 8'b0000_0001

= 8'b1011_1110 & 8'b0000_1100 | 8'b0000_0001

= 8'b0000_1100 | 8'b0000_0001

= 8'b0000_1101

499

499

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?