1.已知八进制数:- (362) 8,求它的

十进制数是: -(3*512+6*64+2*1)= -1922 -(3*64+6*8+2*1)=。。。

二进制原码是: 1111_1100_1000

反码是: 1000_0011_0111

补码是: 1000_0011_1000

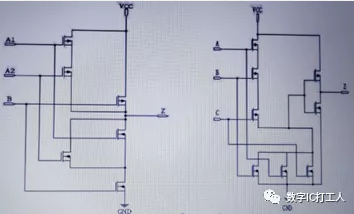

2.写出图中CMOS电路的输出逻辑表达式:Z1= 、Z2=

不会额

第一个

随意感受一下。。a1和a2先或非,然后在和b与非。化简一下a1+a2+b’

第二个 A+B+C

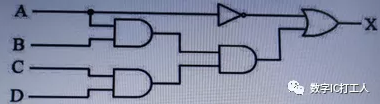

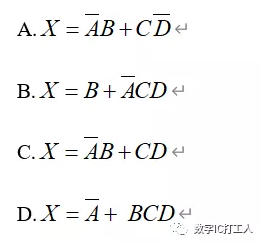

3.如下图的逻辑电路,其逻辑表达式为:( )

解:D

4.布尔代数(A+C) (A+B+C) 等于( )

A. A+BC

B. A+C

C.AB+BC

D.A+B+C

解:D

B

数电忘光了。。

5.十进制数46的格雷码是哪个?( )

A.100011

B.101110

C.111001

D.111110

解:C

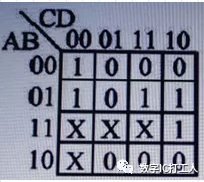

6. X表示任意项,如图所示卡诺图,求化简后的逻辑表达式:

解:B

7.如图所示电路为下列哪种组合逻辑电路( )

A.NAND

B.NOR

C.AND

D.XOR

解:D

8.如图所示逻辑电路,其中FA为全加器,LG为单个逻辑门,若F=0时,输出为X3X2X1X0+Y3Y2Y1Y0;F=1时,输出为X3X2X1X0-Y3Y2Y1Y0,则LG应为:( )

A.OR

B.NOR

C.NAND

D.XOR

解:D

9.如图所示电路的CLK为20kHz,状态图数字排列为Q3Q2Q1Q0,若初始状态为0000,则该电路的状态图为哪个?( )

A.

B.

C.

D.

没有图

10.如图所示逻辑电路,AV/B/C/D四个输入共有几种组合会让Y输出为1?( )

A.6

B.7

C.8

D.9

解:A

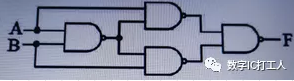

11. 如图所示电路,LG为哪种逻辑门电路,才可以得到如表的实验结果?( )

A.AND

B.NOR

C.NAND

D.XOR

解: 这个表打错了应该是,一行和最后一行的输出一样,输出居然不一样

假设最后一行是 on on 暗

结果为C

12.如图所示电路,其中D触发器的PR、CLR为0有效,若VDD开启前电容已完全放电,则下列叙述正确的是( )

A.电源开启后,LED亮,按下S1放开后,LED暗,之后再按下S1时,LED没有变化

B.电源开启后,LED亮,按下S1放开后,LED开始闪烁,再次按下S1则停止闪烁,LED灭,重复以上动作

C.电源开启后,LED暗,按住S1按钮时,LED亮,放开S1则LED灭,重复以上动作

D.电源开启后,LED暗,按住S1按钮时,LED闪烁,放开S1则LED灭,之后再按S1时,LED没有变化

解:A

D触发器中PRN、CLRN区别以及复位电平选择_郎爱上羊的博客-CSDN博客_d触发器prn

上电,q'输出0;按下s1,clr‘=0,q’=1灯灭;放开s1,停止异步复位,但是没有clk上升沿,所以再怎么按s1也没用了

13.有一个4位计数器,可计数范围为0~9,若输入时钟频率为1MHz,请问最高位的输出频率与正脉冲的宽度为多少?( )

A.输出频率100kHz,正脉冲宽度为2us

B.输出频率100kHz,正脉冲宽度为5us

C.输出频率500kHz,正脉冲宽度为2us

D.输出频率500kHz,正脉冲宽度为8us

解:A

简答

14.什么是亚稳态?如何防止亚稳态传播或减少亚稳态概率?

亚稳态—学习总结 - jerry_cat - 博客园

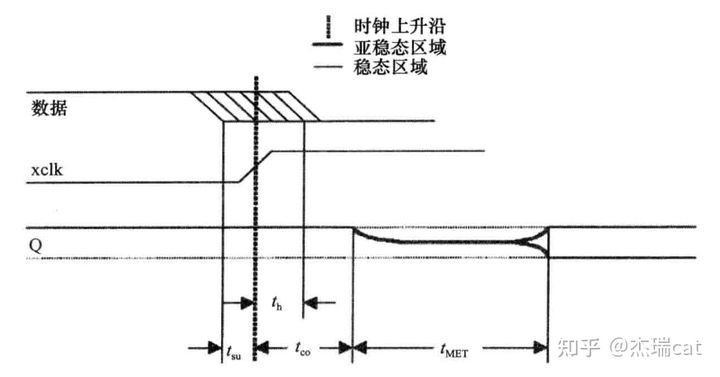

一、什么是亚稳态

首先康康百度怎么解释亚稳态的:亚稳态是指触发器无法在某个规定时间段内达到一个可确认的状态。当一个触发器进入亚稳态时,既无法预测该单元的输出电平,也无法预测何时输出才能稳定在某个正确的电平上。在这个稳定期间,触发器输出一些中间级电平,或者可能处于振荡状态,并且这种无用的输出电平可以沿信号通道上的各个触发器级联式传播下去。

根据百科解释,可以提炼以下特点:

1)亚稳态违背了时序,无法在规定时间成为稳态。

2)亚稳态输出不确定,但是会传给后一级触发器。这会导致后级电路出错。所以亚稳态危害很大。

3)亚稳态最终都会稳定下来,但需要较长的时间。

二、亚稳态是怎么产生的

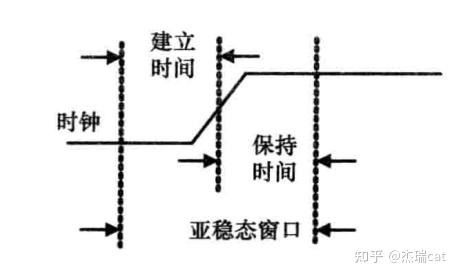

根据1.1,我们知道亚稳态是由于违背了触发器的建立(Tsu)和保持时间(Th)而产生的。

首先解释几个基本概念:

Tsu为建立时间:是指在触发器的时钟信号上升沿到来以前,数据稳定不变的时间,如果建立时间不够,数据将不能在这个时钟上升沿被稳定的打入触发器,Tsu就是指这个最小的稳定时间。

Th为保持时间:是指在触发器的时钟信号上升沿到来以后,数据稳定不变的时间,如果保持时间不够,数据同样不能被稳定的打入触发器,Th就是指这个最小的保持时间。

Tco为输出时间:是触发器在clk时钟上升沿到来之后需多长的时间才能稳定输出的的时间。

Tmet:亚稳态输出恢复到稳定状态所需的超出Tco的额外时间称为稳定时间,即经过这段时间,亚稳态变成稳态了。

如果数据传输中不满足触发器的Tsu和Th,就会造成数据不稳定,从而导致亚稳态。

其核心在于:数据不稳定

三、如何避免亚稳态

如果规定一个特定时间长度,数据在这个时间长度内还不能稳定,则会造成亚稳态。那么定义这个时间长度为亚稳态窗口。

如上面所述,只要满足了建立时间和保持时间,就能避免亚稳态。对于亚稳态窗口来说,窗口越大,进入亚稳态的概率也越大。

在FPGA/IC设计当中,异步信号、跨时钟域信号都是亚稳态高发区。

对于异步信号,一般采用多级同步器,可以避免亚稳态的发生。

相当于拉长了整体的Tsu和Th,让数据有足够的时间稳定下来。

对于跨时钟域信号,采用FIFO对跨时钟域数据进行缓冲,让信号在FIFO中稳定后再输出。

特别注意的是,上述方法只能降低亚稳态发生的概率,如果亚稳态还是发生了,那么上述方法并不能阻止亚稳态传输给后级电路。

15.请用verilog/vhdl实现5分频电路,占空比50%

module div(

input clk ,

input rst_n ,

output clk_div

);

parameter N = 5;

reg clk_p,clk_n;

reg [4:0] cnt_p,cnt_n;

always@(posedge clk or negedge rst_n)begin

if(!rst_n)

cnt_p <='d0;

else begin

if(cnt_p == (N-1))

cnt_p <= cnt_p + 1'b1;

else

cnt_p <= 'd0;

end

always@(posedge clk or negedge rst_n)begin

if(!rst_n)

clk_p <= 'd0;

else begin

if(cnt_p == (N-1)/2) || (cnt_p == (N-1))

clk_p = ~ clk_p;

end

end

always@(negedge clk or negedge rst_n)begin

if(!rst_n)

cnt_n <='d0;

else begin

if(cnt_n == (N-1))

cnt_n <= cnt_n + 1'b1;

else

cnt_n <= 'd0;

end

always@(negedge clk or negedge rst_n)begin

if(!rst_n)

clk_n <= 'd0;

else begin

if(cnt_n == (N-1)/2) || (cnt_n == (N-1))

clk_n = ~ clk_n;

end

end

assign clk_div = clk_p | clk_n;

endmodule

16.用FSM实现一个序列检测模块,a为输入端,b为输出端,如果a连续输入为1101,则b输出为1,否则为0。例如:

a: 0001100110110100100110

b: 0000000000100100000000

请画出状态转移图并写出Verilog代码。

写错了 s3 s4改成s2 s3

module FSM(

input clk ,

input rst_n,

input a ,

output b

);

parameter IDLE = 4'd0;

parameter S0 = 4'd1;

parameter S1 = 4'd2;

parameter S2 = 4'd3;

parameter S3 = 4'd4;

reg [3:0] next_state,state;

always@(posedge clk or negedge rst_n)begin

if(!rst_n)

state <= 'd0;

else

state <= next_state;

end

always@(*)begin

next_state = IDLE;

case(state)

IDLE:

if(a == 1)

next_state = S0;

else

next_state = IDLE;

S0:

if(a == 1)

next_state = S1;

else

next_state = IDLE;

S1:

if(a == 1)

next_state = S1;

else

next_state = S2;

S2:

if(a == 1)

next_state = S3;

else

next_state = IDLE;

S3:

if(a == 1)

next_state = S1;

else

next_state = IDLE;

endcase

end

assign b = (state == S3)?1'b1:1'b0;

endmodule

17.翻译以下段落,并根据描述画出I2C接口的start和stop时序:

The I2C bus employs two signals, SDA(data)and SCL (clock), to communicate between integrated circuits in a system.Thebus transfers data serially, one bit at a time. The 8-bit address and databytes are transferred with the most-significant bit (MSB) first. Inaddition, each byte transferred on the bus is acknowledged by the receiving device with an acknowledge bit. Each transfer operation begins with the master device driving a start condition on the bus and ends with the master device driving as top condition on the bus. The bus uses transitions on the data pin(SDA) whilethe clock is at logic high to indicate start and stop conditions. A high-to-lowt ransition on the SDA signal indicates a start, and a low-to-hightransitionindicates a stop. Normal data-bit transitions must occur within the low time of the clock period.

I2C接口利用两个信号,SDA(数据线)和SCL(时钟线),来在系统中的集成电路之间进行通讯。总线传输方式为串行,每次传输1bit。8bit地址和字节首先传输最高符号位MSB。另外,每个字节通过接受设备的1bit接受信号来确认在总线传输成功。每次传输过程开始时,主设备会驱动一个启动信号,结束时主设备会驱动一个停止信号。总线通过SDA数据总线,在时钟电平为1时,进行发送和接受。时钟下降沿时,SDA开始启动发送,时钟上升沿时,SDA停止发送。正常情况下数据位传输必须发生在时钟为低电平期间。

百度翻译的

I2C总线使用两个信号SDA(数据)和SCL(时钟)在系统中的集成电路之间进行通信。总线一次一位串行传输数据。8位地址和数据字节首先以最高有效位(MSB)传输。此外,总线上传输的每个字节都由接收设备用一个确认位进行确认。每次传输操作从主设备驱动总线上的启动条件开始,到主设备驱动总线上的astop条件结束。当时钟处于逻辑高位时,总线使用数据引脚(SDA)上的转换来指示启动和停止条件。SDA信号从高到低的转换表示启动,从低到高的转换表示停止。正常的数据位转换必须在时钟周期的较短时间内发生。

657

657

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?