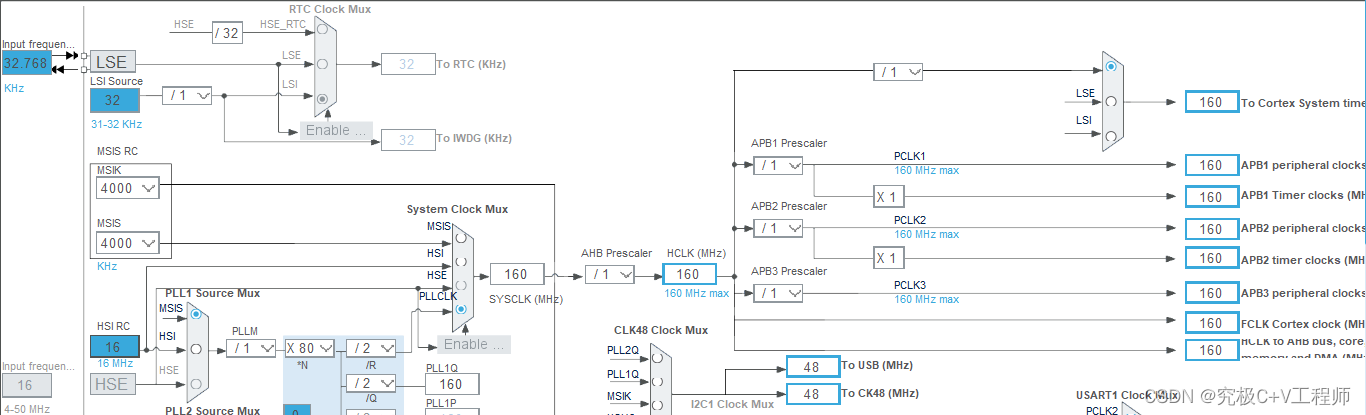

1. RCC时钟树

STM32本身十分复杂,外设非常多,任何外设都需要时钟才能启动,但每个外设所需频率不尽相同,所以利用复杂的MCU采用多时钟源的方法来解决这些问题。

时钟树主要分为三大部分:时钟输入源、选择器/分频器(APB)/倍频器、最终设定频率三大部分。

1.1 内核与外设时钟

内部时钟源主要有以下四种:

| 名字 | 振荡器类型 |

| HSI(高速内部时钟) | RC振荡器,频率为8MHz,精度不高。 |

| HSE(高速外部时钟) | 可接石英/陶瓷谐振器,或者接外部时钟源,频率范围为4MHz~16MHz。 |

| LSI(低速内部时钟) | RC振荡器,频率为40kHz,提供低功耗时钟。 |

| LSE(低速外部时钟) | 接频率为32.768kHz的石英晶体。 |

| PLL(锁相环倍频输出) | 其输出频率最大不得超过72MHz |

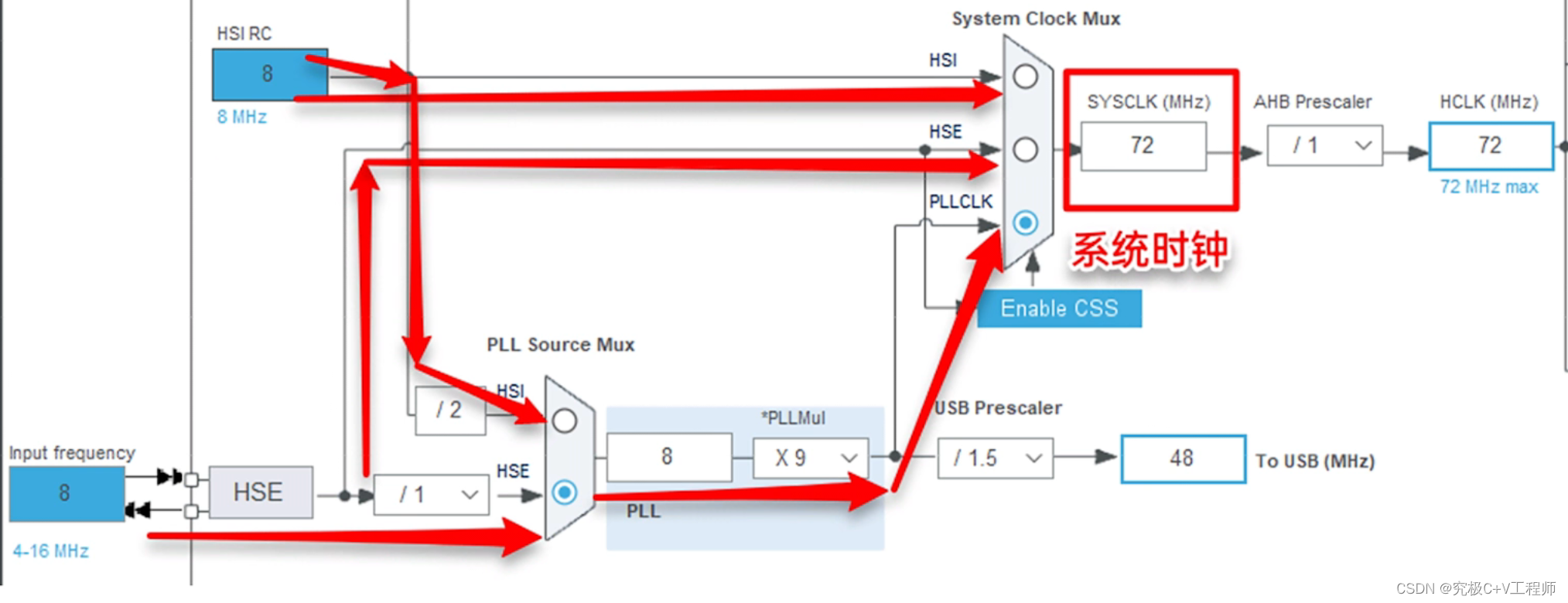

1. SYSCLK

系统时钟SYSCLK最大频率为72MHz,它是供STM32中绝大部分部件工作的时钟源。系统时钟可由PLL、HSI或者HSE提供输出,并且它通过AHB分频器分频后送给各模块使用。

通过此图可以看出HSI无需外接晶振,HSE则需要外接晶振,

PLLCLK输入:经过分频器,倍频器和选择器(图上PLL Source Mux),由于内部具有PLL锁相环电路可以在一定范围内调节频率,通过选择器可切换HSI与HSE内部输入,可以看到他们两个分别还具有一个分频器(图上/2的字样)。

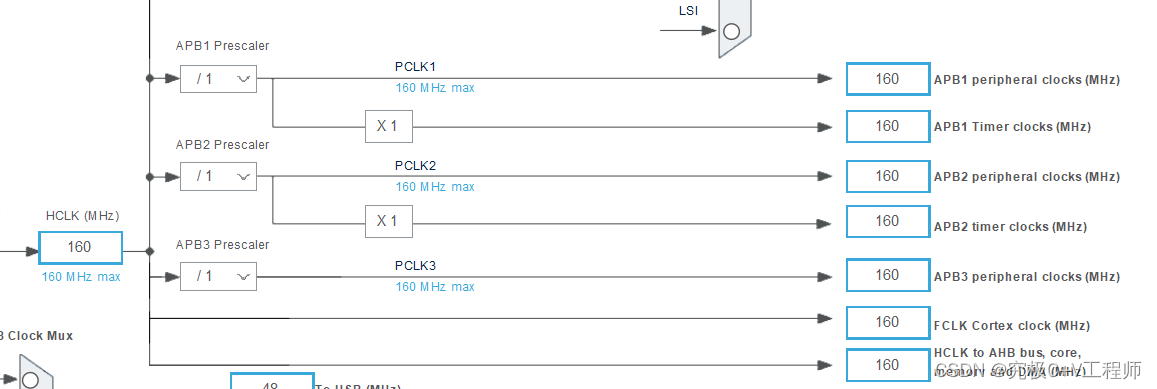

2. HCLK

HCLK为高性能总线AHB(advanced high-performance bus)提供时钟信号。由系统时钟SYSCLK分频得到,一般不分频时等于系统时钟,是给外设使用的,分频时可将频率提供给AHB总线/内核/存储器/DMA等内核。通常HCLK与SYSCLK保持一致。

3. FCLK

FCLK(free running clock)是自由运行时钟,为ARM内核提供运行的时钟信号。我们所说的CPU主频为xxHz,指的就是这个时钟信号频率,CPU时钟周期就是1/FCLK()。FCLK不受总线限制,HCLK还需要经过AHB总线,由于内核时钟与AHB总线时钟需要保持一致所以FCLK与HCLK需要保持同步。

4. PCLK

PCLK为高性能外设总线APB(advanced peripherals bus)提供时钟信号。

5. ADCCLK

ADC的时钟频率由系统时钟经过PCLK2经过分频后得到。

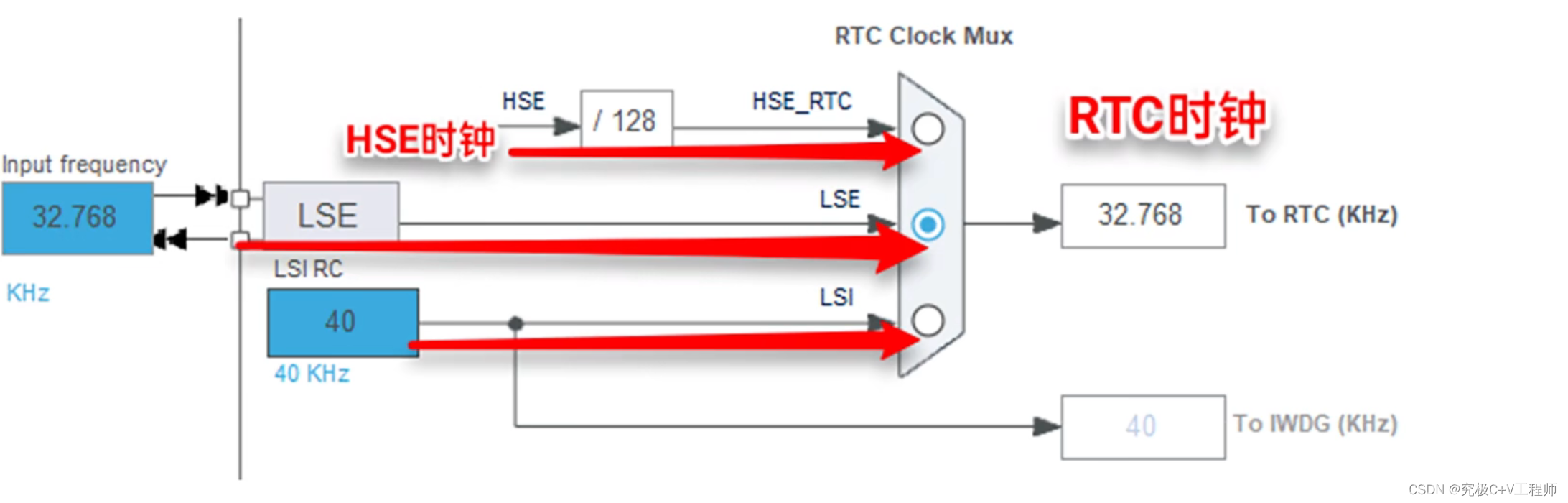

1.2 独立时钟

1. RTC时钟(Real Time Clock)

RTC模块拥有一个连续计数的计数器,在相应的软件配置下,可以提供时钟日历的功能。修改计数器的值可以重新设置当前时间和日期 RTC还包含用于管理低功耗模式的自动唤醒单元。具体可看上图。

2. 独立看门狗(IWDG)

STM32 有两种看门狗,提供了更高的安全性、时间的精确性和使用的灵活性,一个是独立看门狗另外一个是窗口看门狗。独立看门狗通过LSI RC直接提供时钟信号

3. FLASH编程时钟

HSI RC直接给FLASH提供时钟信号 8MHZ不允许修改

4. USB接口时钟

上面说的有

2. RCC程序代码

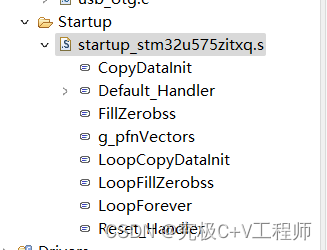

2.1 启动文件中的代码

这里自行查看

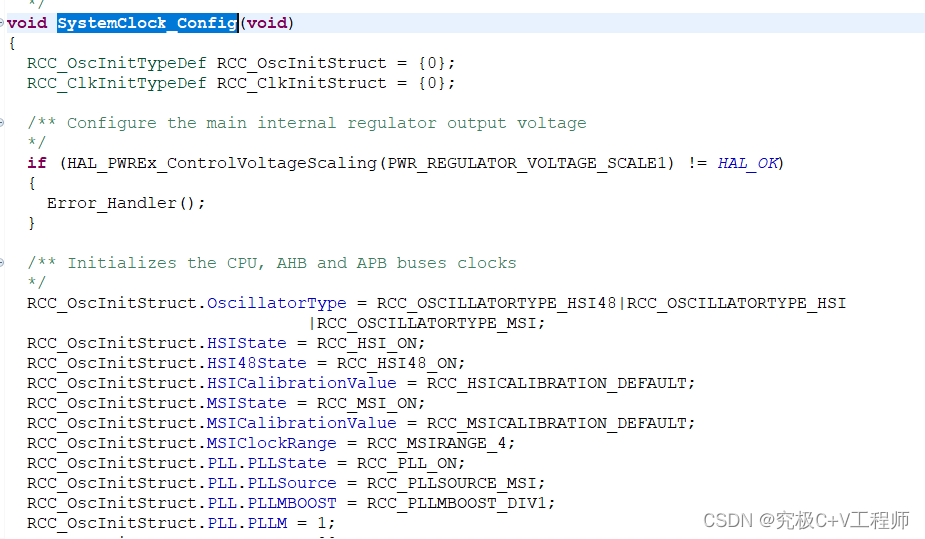

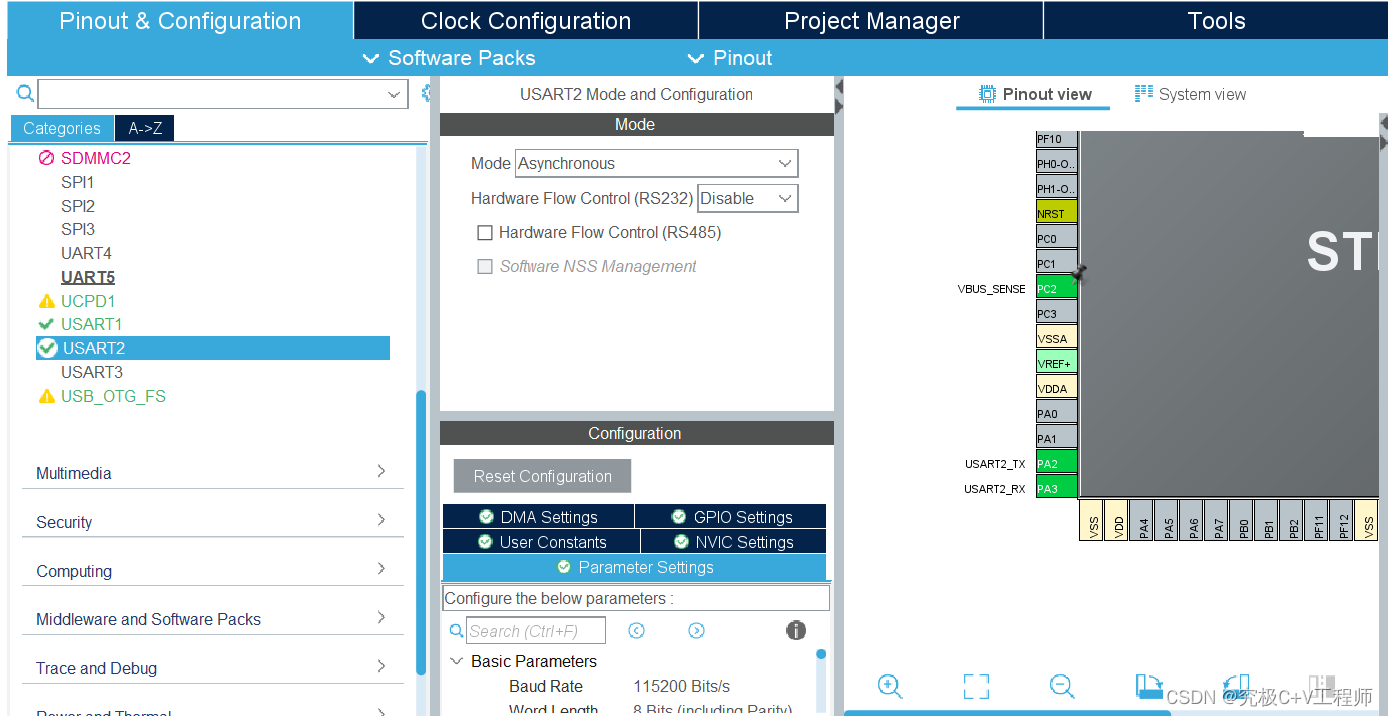

2.2 CubeMX生成的代码

2.3 如何修改时钟设置

一般只需要修改波特率。

3. HAL库中的延时函数

HAL_Delay(1000);这个是HAL库自带的延时函数

1388

1388

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?