2.5.2逻辑功能的仿真与测试

工作原理:

1.产生模拟激励(输入波形);

2.将产生的激励加入到被测试模块并观察其输出响应;

3.将输出响应与期望进行比较,从而判断设计的正确性。

接下来就是仿真激励 Testbench的编写,首先给大家介绍下 Testbench的原理。我们通常给 Testbench 的取名是在被测试的模块名前加个 tb_(也可以在被测试的模块名后面加_tb),容易识别出具体验证的是哪个模块。第一步建立测试平台,我们把待测试模块放进测试平台,进行测试,模块不同输入输出个数和名字会不同。第二步将待测试模块放进测试平台里。第三步就是写测试激励文件对输入信号赋值或者给出相应的信号,来观察输出信号的变化是否符合我们的功能

实验步骤:

1.新建一个文件夹,命名为test.v。

2.打开Modelsim软件,在library图书库中新建一个ygwork;点击:file—new—project新建一个项目,在弹出的小窗口中任意编辑文件名,这里我编辑为:wer.v,点击选择Verilog—ok关闭窗口:再在弹出的小窗口中编辑文件名:wert.v,点击选择Verilog—ok确定关闭窗口。

3.在project页面会出现刚刚编辑的,以“wer.v和wert.v"命名的两个记事本,在记事本中输入相应的激励块代码并保存。

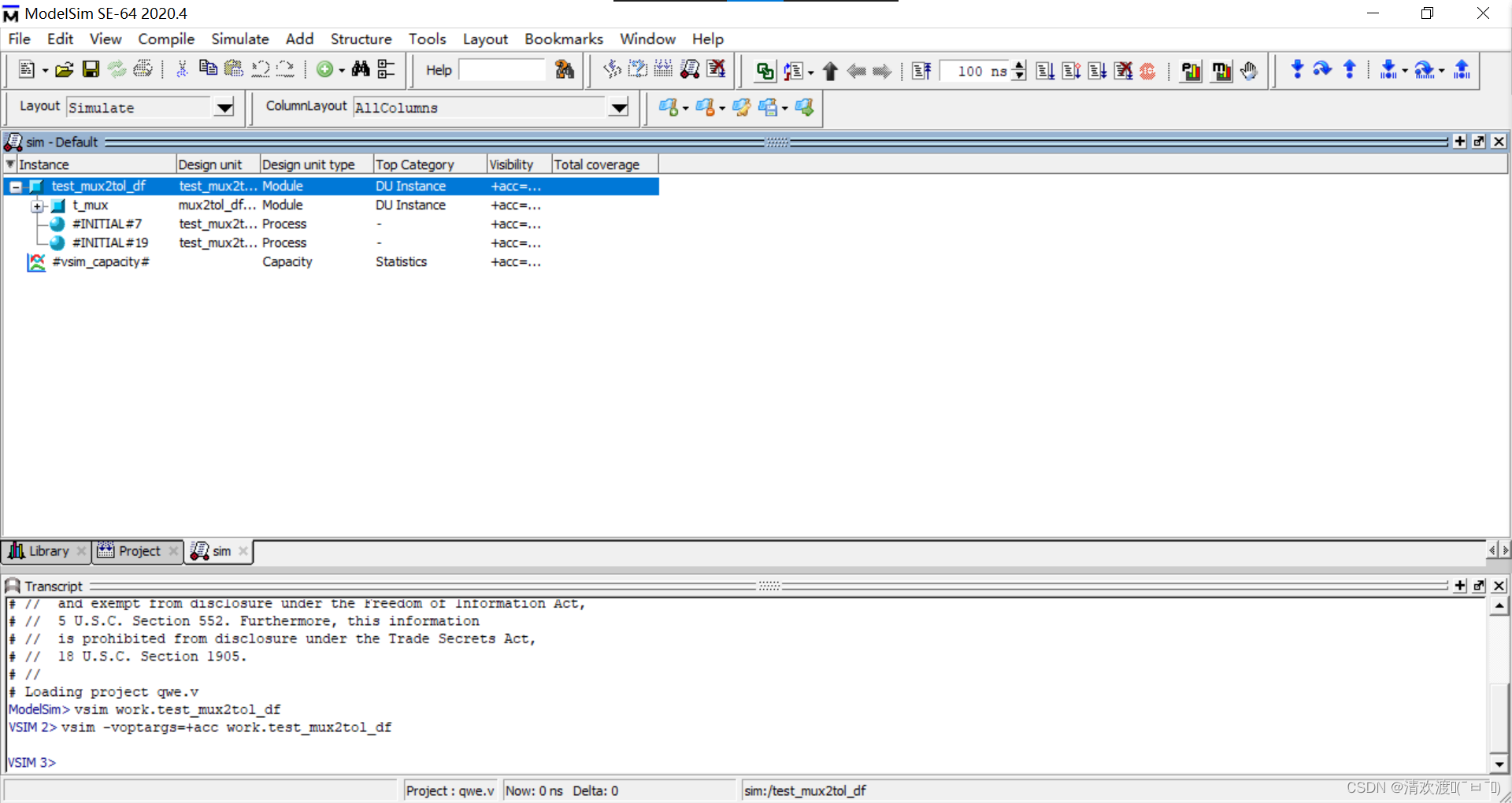

4.点击"library—work—test_mux2tol_df",点击右键选择simulate,进入如下界面。

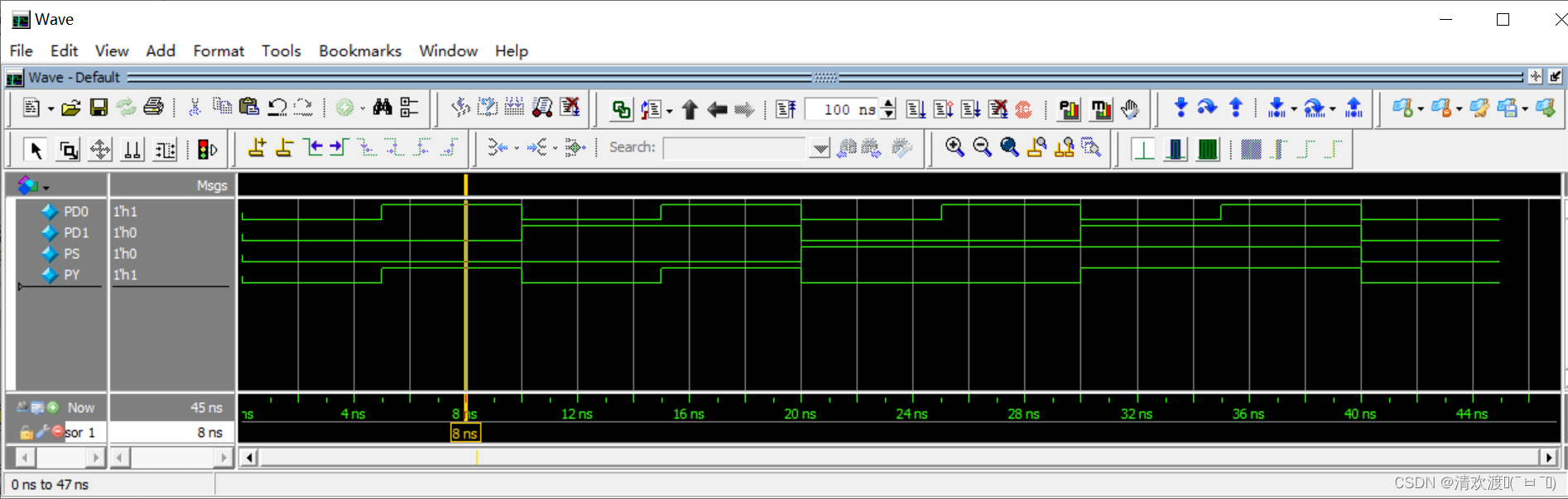

5.右键选择”add to—wave—All items in region",出现仿真输出波形界面,点击All run 进行仿真运行,再点击全显示就可以得到完整的仿真输出波形,如下图。

6.结束仿真,退出Modelsim界面。

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?