ADC IP信号线

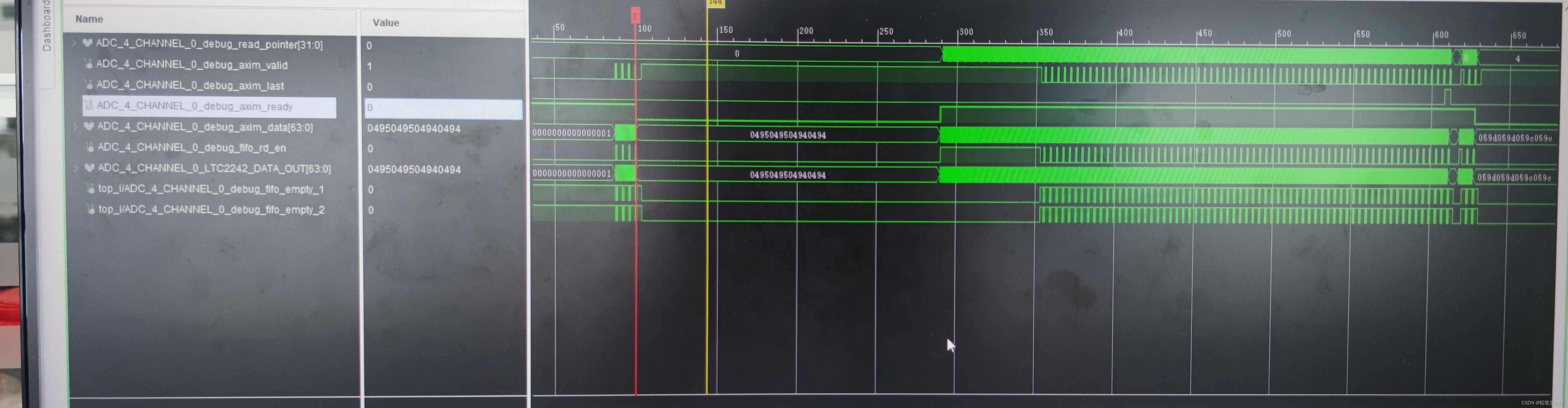

AXIS协议,DEVICE_TO_DMA模式,DMA先拉高READY信号然后,ADC一直拉高VALID信号,当这两个信号同时拉高时数据传输,ADC将LAST信号拉高时传输完成。

在上一次让FPGA工程师修改LAST信号计数后,仍然出现了问题,DMA在LAST拉高后并没有立即拉低READY信号,导致有四个数据进入DMA的缓冲区。

关于使用AXI_DMA使用的问题,我实现的功能是使用AXI_DMA采集ADC数据写入DDR,每次数据包128个,数据包大小64bit,但是AXI总线在LAST信号拉高之后,并没有立即拉低READY信号,而是又接收了4个时钟数据然后拉低,并且这4个时钟数据并没有写入DDR,仍然存在DMA的缓冲数组中,在下一次传输开始时,这4个时钟数据会最开始写入,然后重复这个过程。

这是最初从ADC传过来的数据,可以看到,REDAY信号在4个数据包发送过来之后拉低,在我开启DMA传输之后再次拉高,然后在最上面的read_pointer计数到127时,ADC把LAST信号拉高,按理来说,此时这一轮数据已经传输完成,可是DMA并没有将READY信号拉低,在又接收了四个数据后拉低,于是导致这4个数据变成我下一轮DMA传输的前四个数据,最终让我写入DDR的数据在第四个数据这里断开了。

头痛,暂时放弃。

5435

5435

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?