interface reg_intf(input clk, input rstn);

logic [1:0] cmd;

logic [`ADDR_WIDTH-1:0] cmd_addr;

logic [`CMD_DATA_WIDTH-1:0] cmd_data_s2m;

logic [`CMD_DATA_WIDTH-1:0] cmd_data_m2s;

clocking drv_ck @(posedge clk);

default input #1ns output #1ns;

output cmd, cmd_addr, cmd_data_m2s;

input cmd_data_s2m;

endclocking

clocking mon_ck @(posedge clk);

default input #1ns output #1ns;

input cmd, cmd_addr, cmd_data_m2s, cmd_data_s2m;

endclocking

endinterface

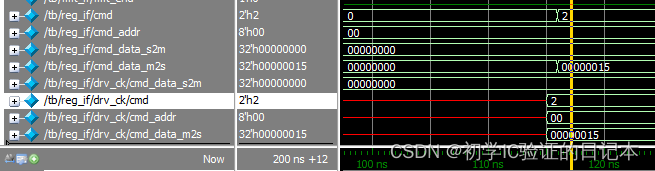

1:对于,reg_if.drv_ck .xx信号,在时钟沿边沿变化,但reg_if.xx信号会加入提前采样和延后驱动并且连接到dut上。

2:

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

496

496

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?