说明:

FPGA:A7系列,例如:xc7a35tfgg484;

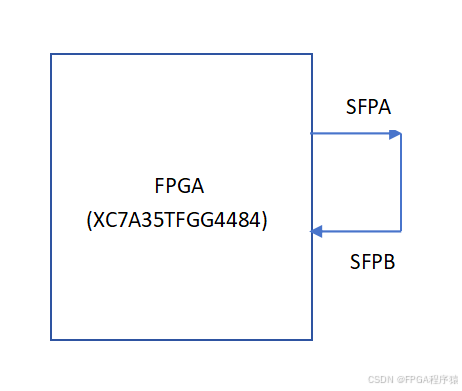

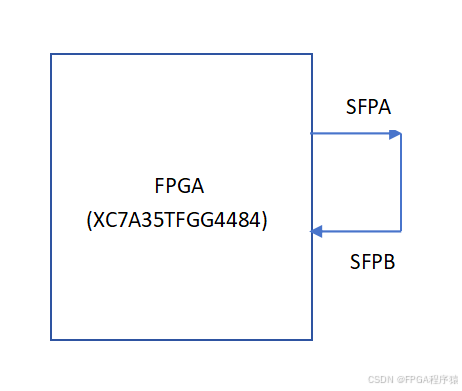

FPGA开发板通过SFPA(光口)与SFPB(光口)通过光纤相连进行GTP的数据还回通信;

运行环境:Vivado2018.3。

所用IP核:7 Series FPGAs Transceivers Wizard(3.6),因为是A7系列芯片,GT资源为GTP高速串行收发器,最大线速率为6.6Gb/s。

SFP模块:SFPA和SFPB

实验原理连接示意图:

目录

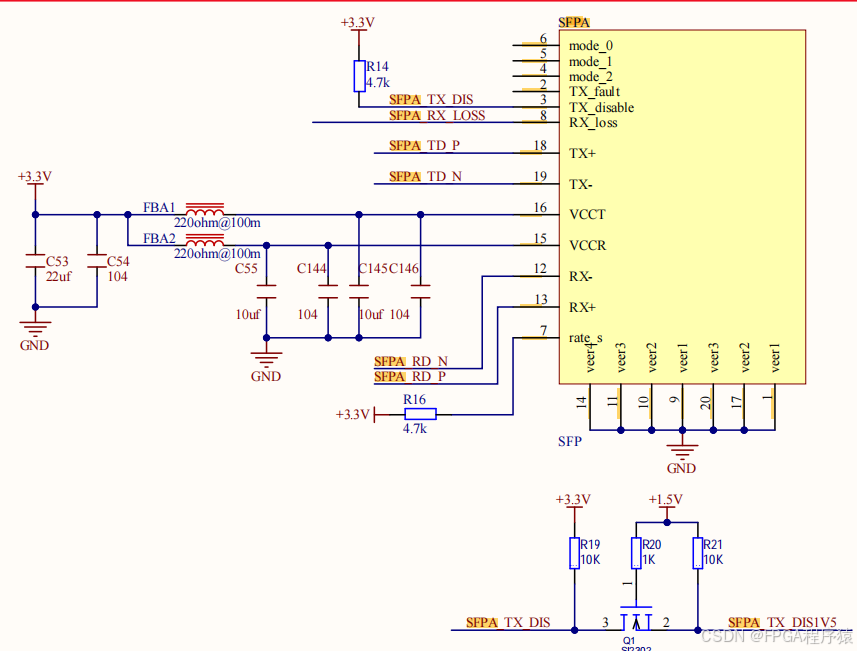

1.IP核配置前先熟悉硬件原理图

2. IP核配置

3.生成IP Example 工程并做相应修改

4.Implementation

5.调试结果

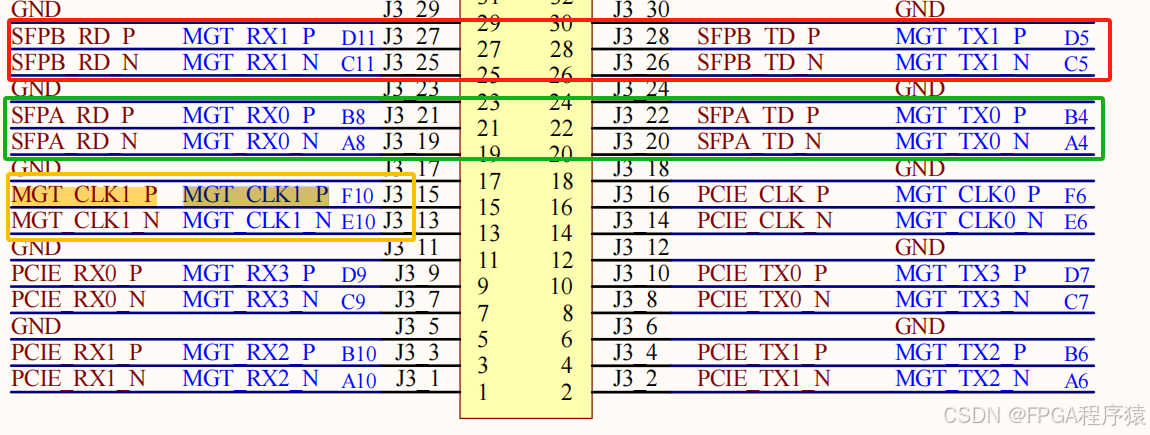

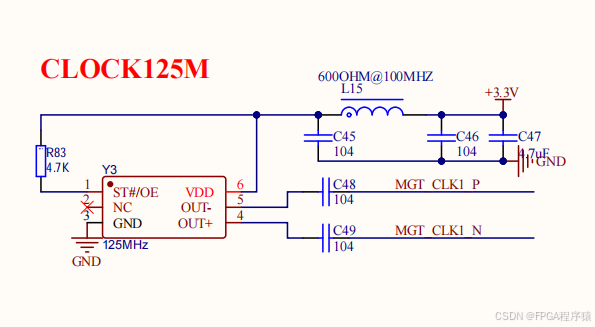

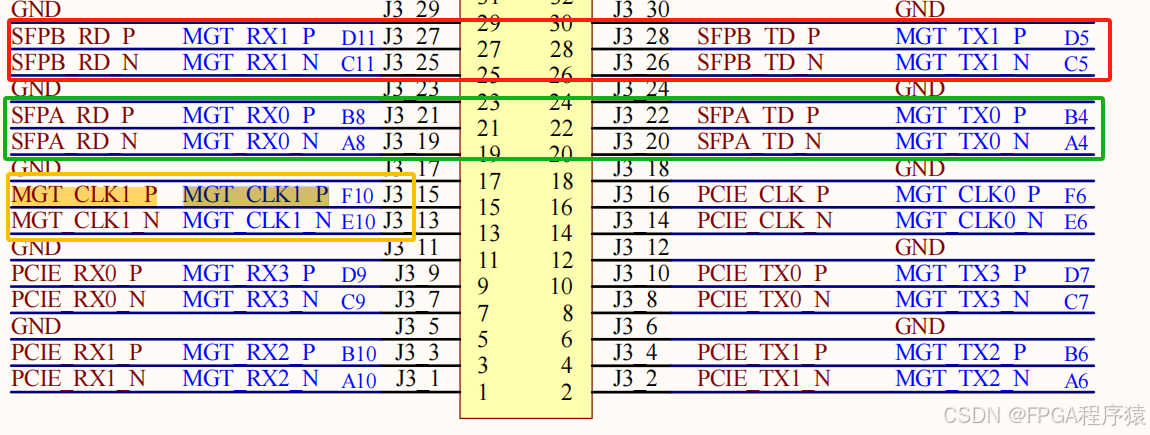

1.IP核配置前先熟悉硬件原理图

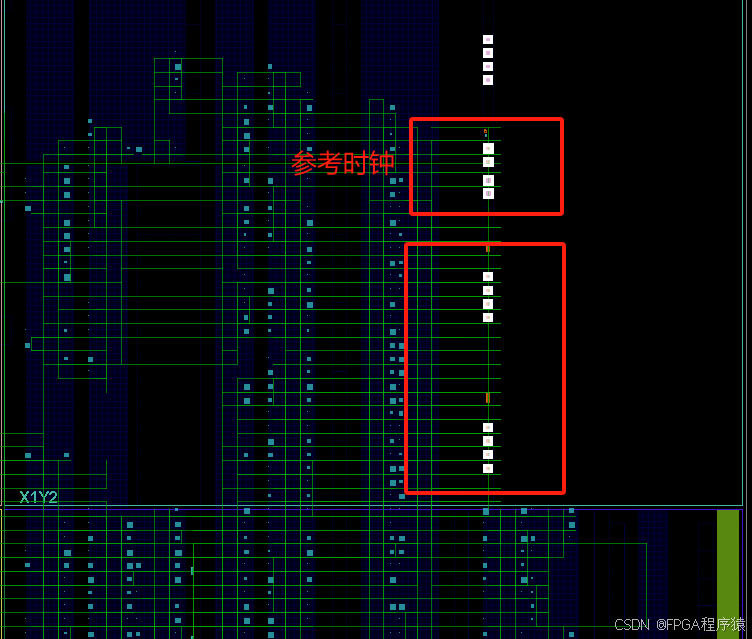

红线框内是SFPB光口模块所对应的GTP通道,

绿线框内是SFPA光口模块所对应的GTP通道,

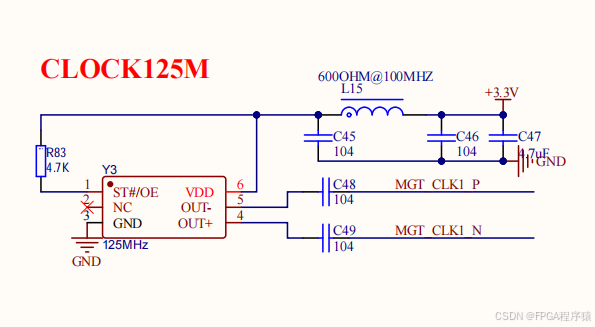

黄线框内是板子GT所需要的125M的参考差分时钟;

板载参考差分时钟,注意:后面在IP核勾选界面需要依据这个选择。

板载参考差分时钟,注意:后面在IP核勾选界面需要依据这个选择。

接下来我们回到最重要的环节,vivado软件GTP配置;

2. IP核配置

page1:

注意这里GT Type直接就是默认的GTP,因为我们是A7系列,所含的GT资源就是GTP,这里软件会帮我们默认选择,如果是更高端比如K7或者V7系列等芯片,即为GTX/GTH;

这里选择include shared logic in the example design,具体两个选择有什么区别自行搜索;

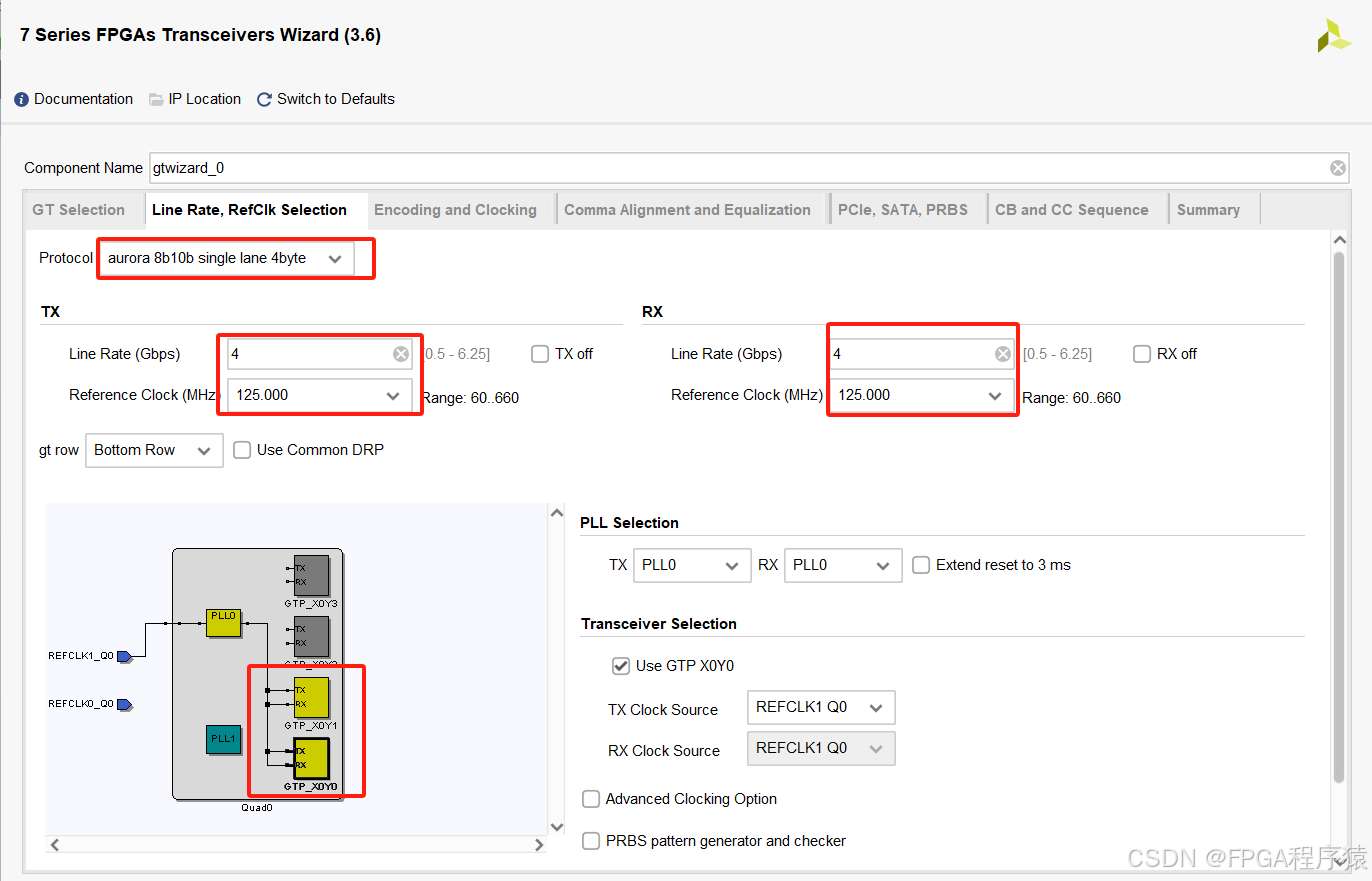

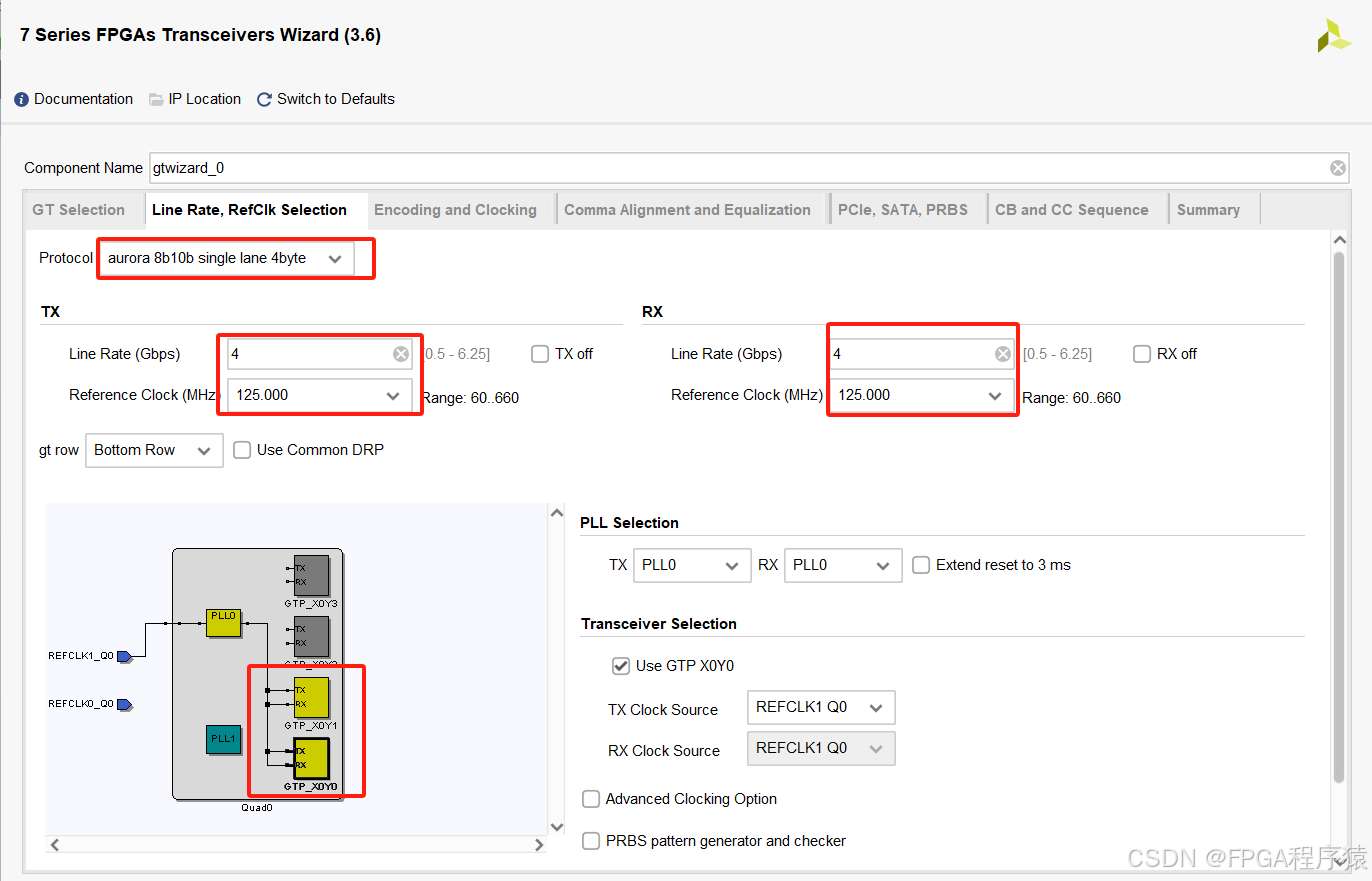

page2:

高速收发器支持多种标准协议,可以选择一个标准协议,这样后续的选项均已配置好了,然后根据自己的需求改动。此处选择点对点传输的Aurora 8b10b single lane 4byte。这里我们用的光模块传输是单路的,所以选择 single lane, 数据接口为 4byte, 就是 32 位。此处设置较低速率 4Gbps 用于功能验证,参考时钟为 125M。注意参考时钟为收发器输入时钟,频率必须与开发板上为 GTP 提供时钟的晶振一致。

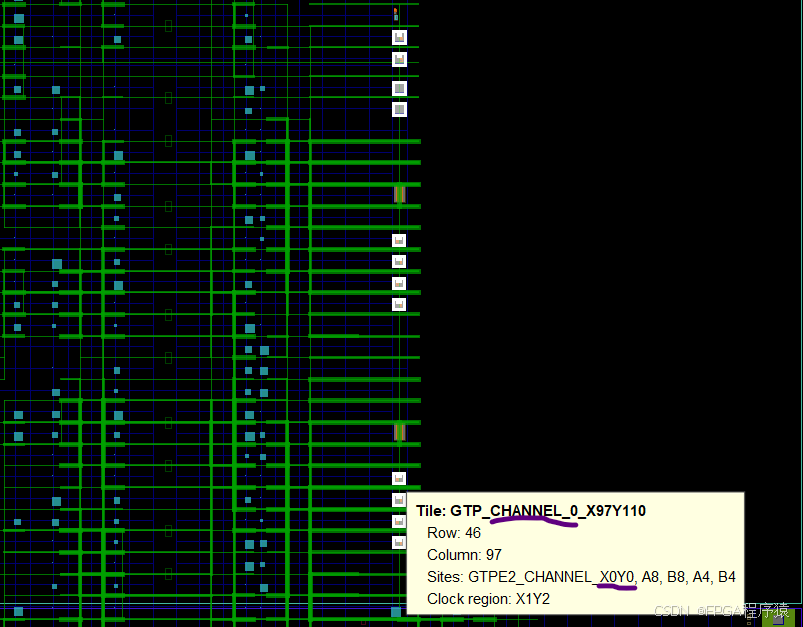

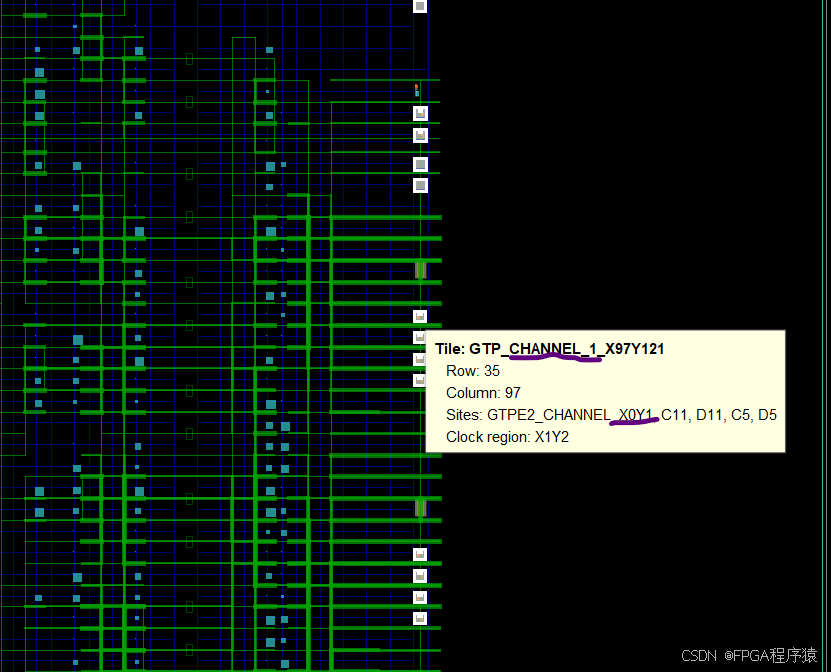

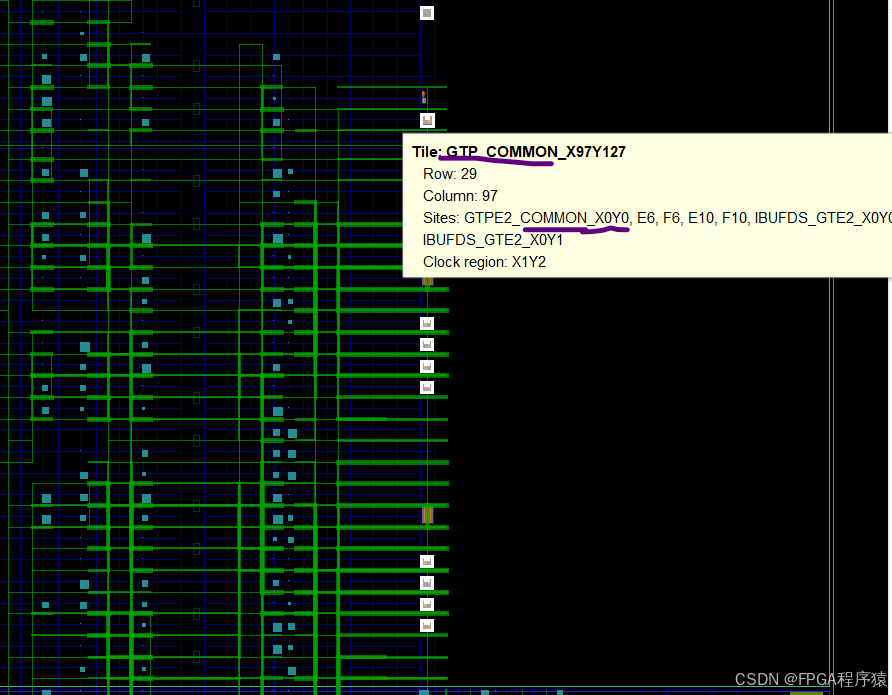

GTP 的 2 个参考输入时钟都能连到 PLL0 和 PLL1,所以在 ip 核中可以任意选择用 PLL0还是 PLL1。因为本次实验的收发速率是一致的,所以 RX 和 TX 可以共用一个锁相环,否则必须用两个锁相环。本次开发板的外部参考时钟是接在 GTPREFCLK1,故在 ip 核中将参考时钟设为 GTPREFCLK1。本次开发板用了 2 个 SFP 接口,这 2 个接口分别连接到 GTP_X0Y0 和 GTP_X0Y1。

这里我们也可以发现有四个channal,刚好组成一个quad,对应原理图所展示的资源;

page3:

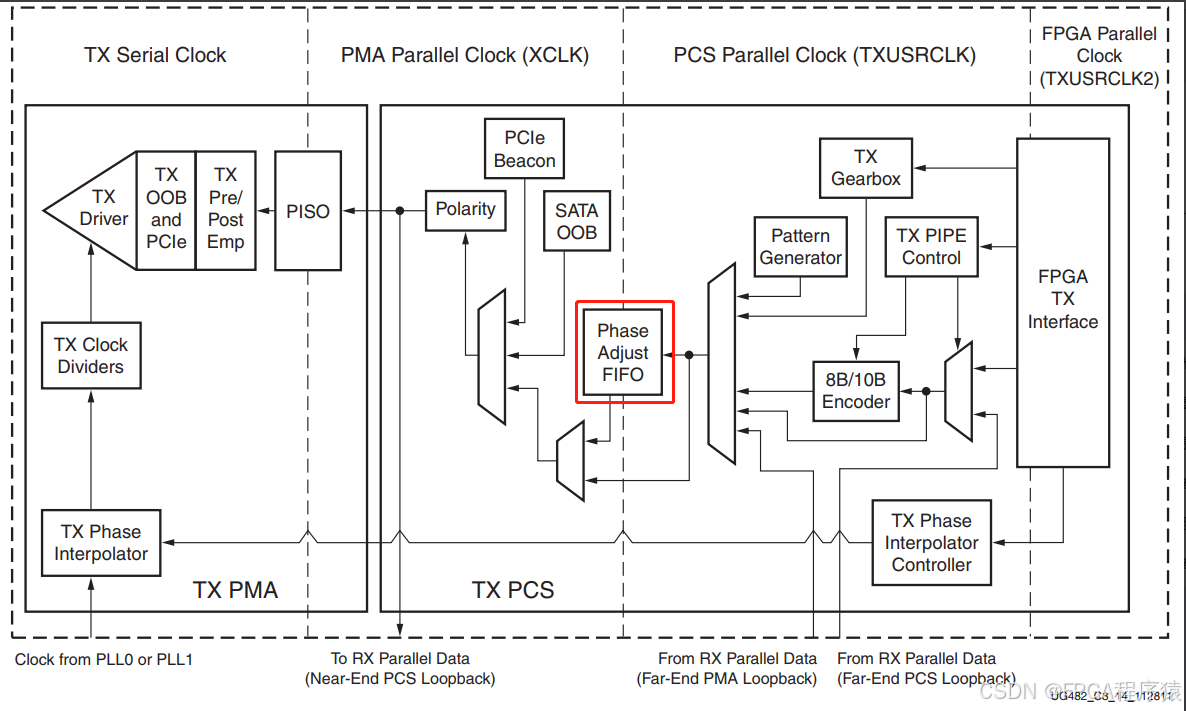

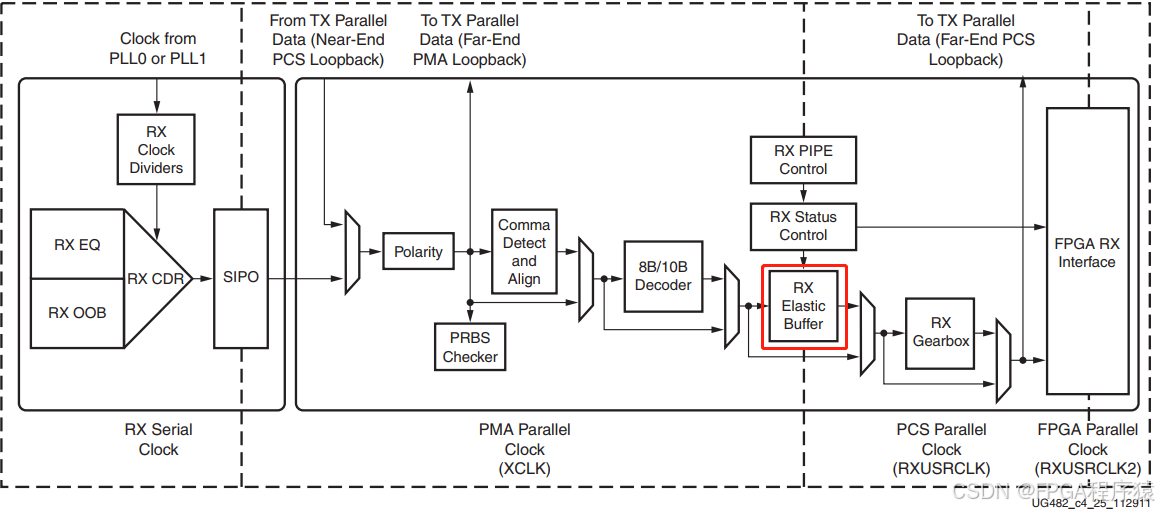

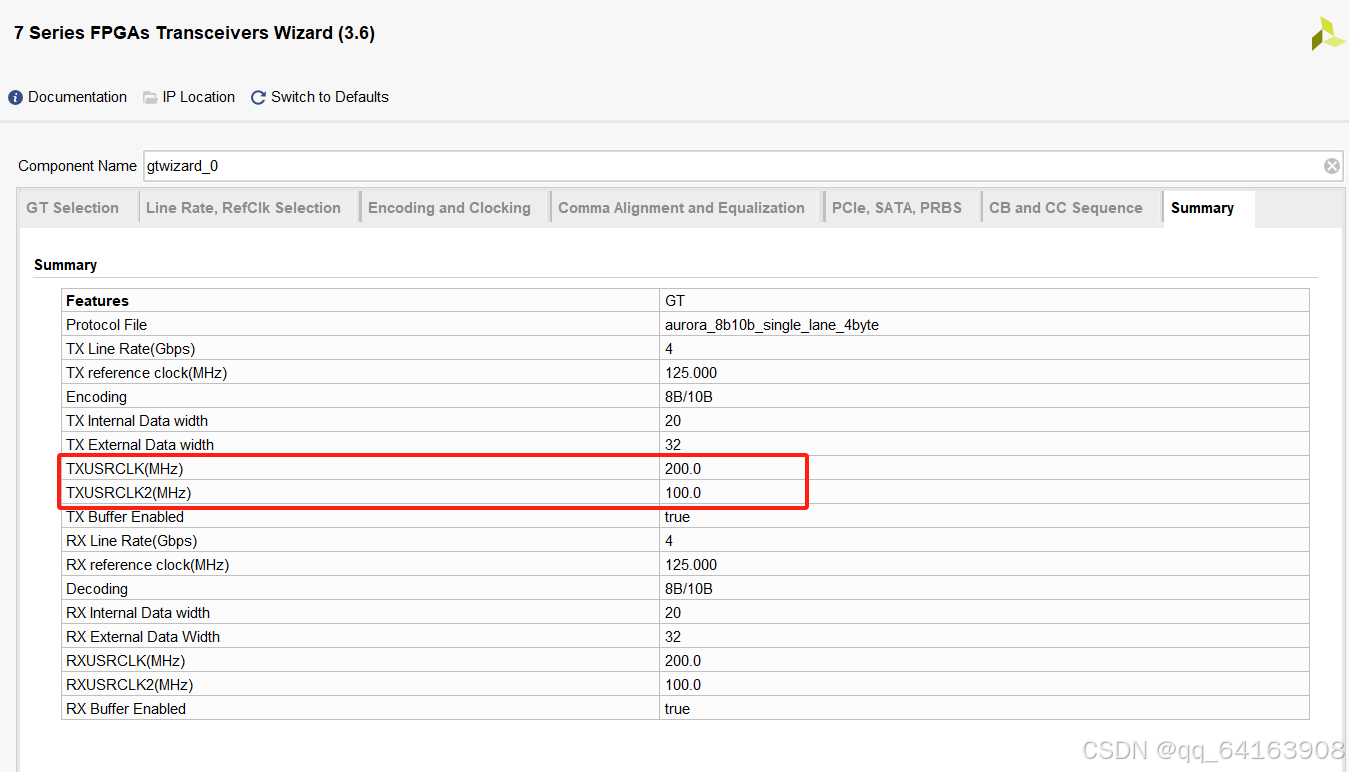

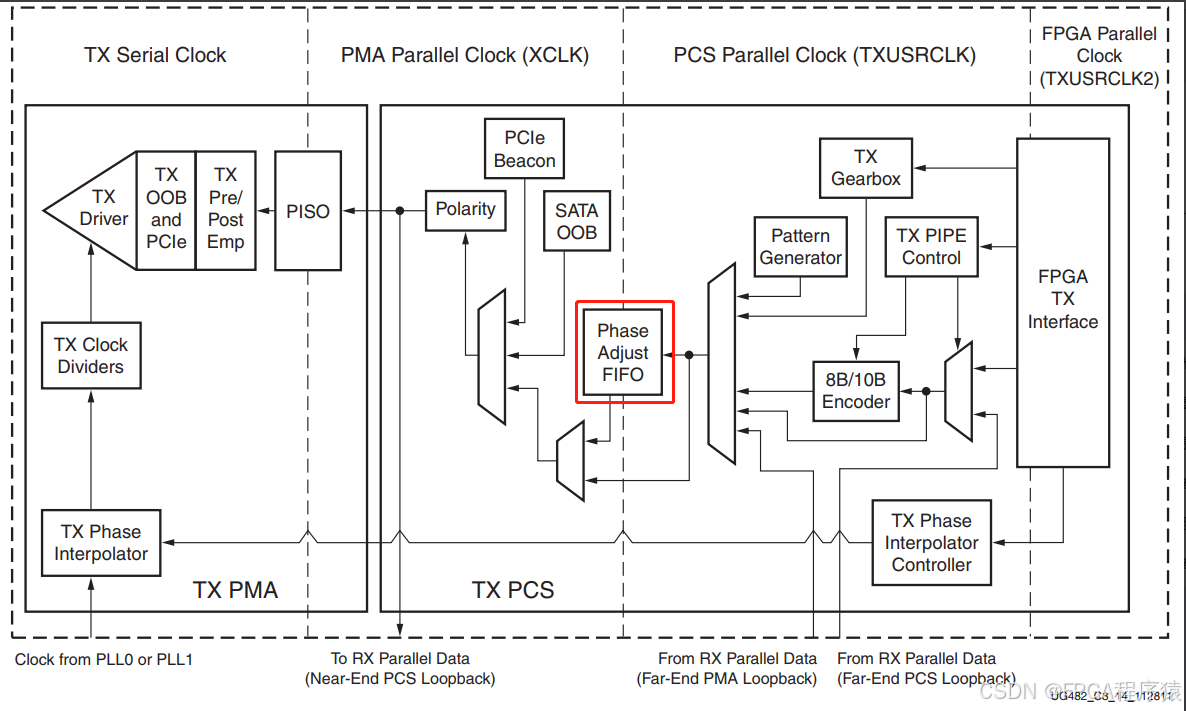

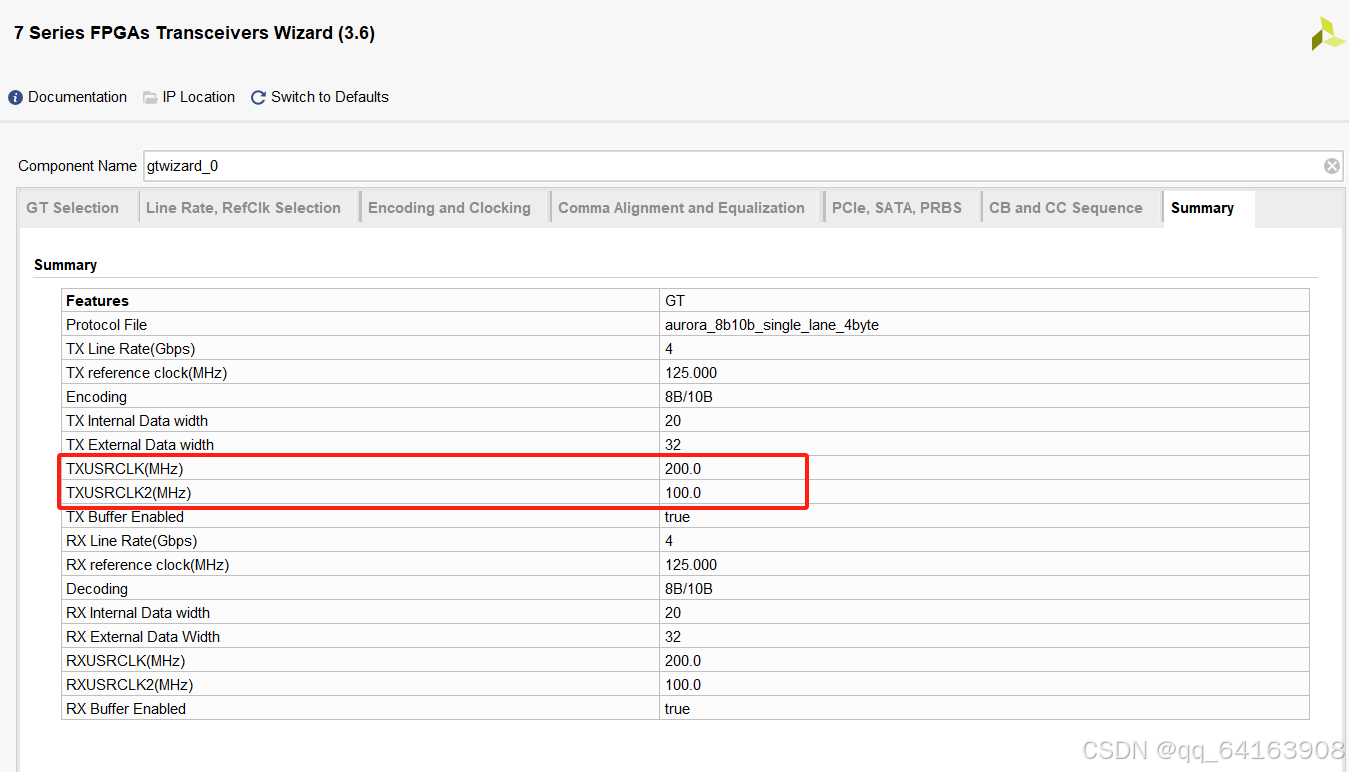

因为在上一页选的是 Aurora 8b10b single lane 4byte 协议,所以这里的外部数据位宽为 32bit(此处的数据接口为FPGA内部用户逻辑与IP核的接口)。本次实验是做 Aurora 8b10b 环回实验,所以在编码方式这栏中选择 8B/10B 编码;内部数据位宽也是默认20bits,这里提到一点,在前面我们设置的线速率为4Gbps,这里内部数据位宽为20bits,因此可以计算出TXUSRCLK=200MHZ,TXUSRCLK2=TXUSRCLK/2即为100MHZ;

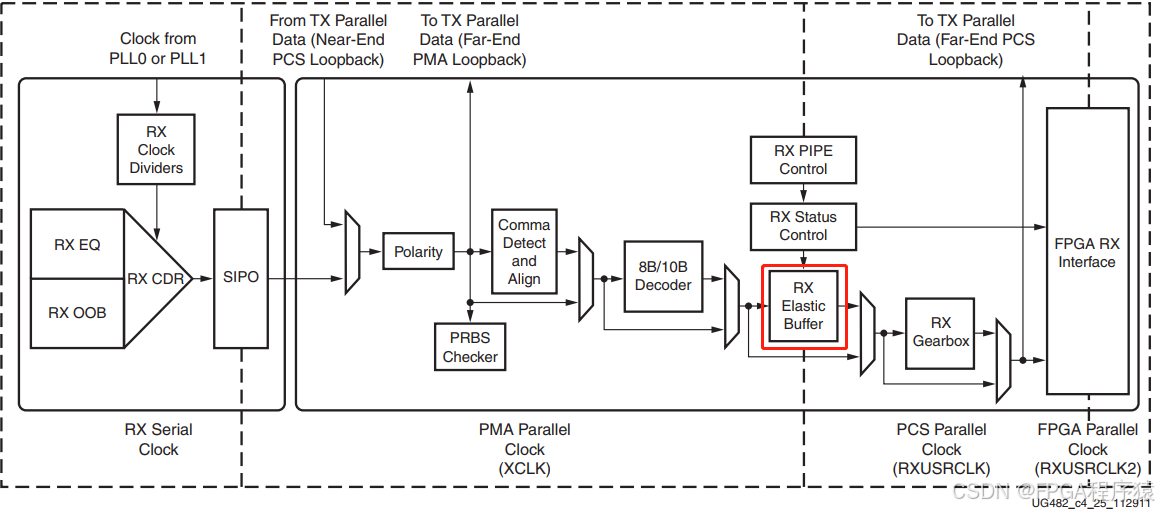

DRP/System Clock Frequency 是动态重配置或系统工作时钟,通过 DPR 可以让设计者根据所选线速率和定义的协议实时调整收发器参数。该时钟可以通过锁相环来配置,本次实验将该时钟设为 50M。此外,数据不管是从时钟 TSUSRCLK 到 XCLK 还是从时钟 XCLK 到 RSUSRCLK都经过了时钟域的转换,所以 TX 端和 RX 端都需要一个缓存区缓存下,因此把 ip 核中的 Enable TX Buffer 和 Enable RX Buffer 这 2 个选项给勾上(这里你可能会有疑惑,想知道为什么这样需要你进一步了解GTP内部结构)。因为本次实验的发送端和接收端使用的是同一个晶振产生的差分时钟,按照 2 个时钟的使用规则,RSUSRCLK 这里采用 TXOUTCLK 来驱动,否则不满足时序要求。

至于为什么需要勾选buffer,请看下图xilinx官方指导手册介绍:

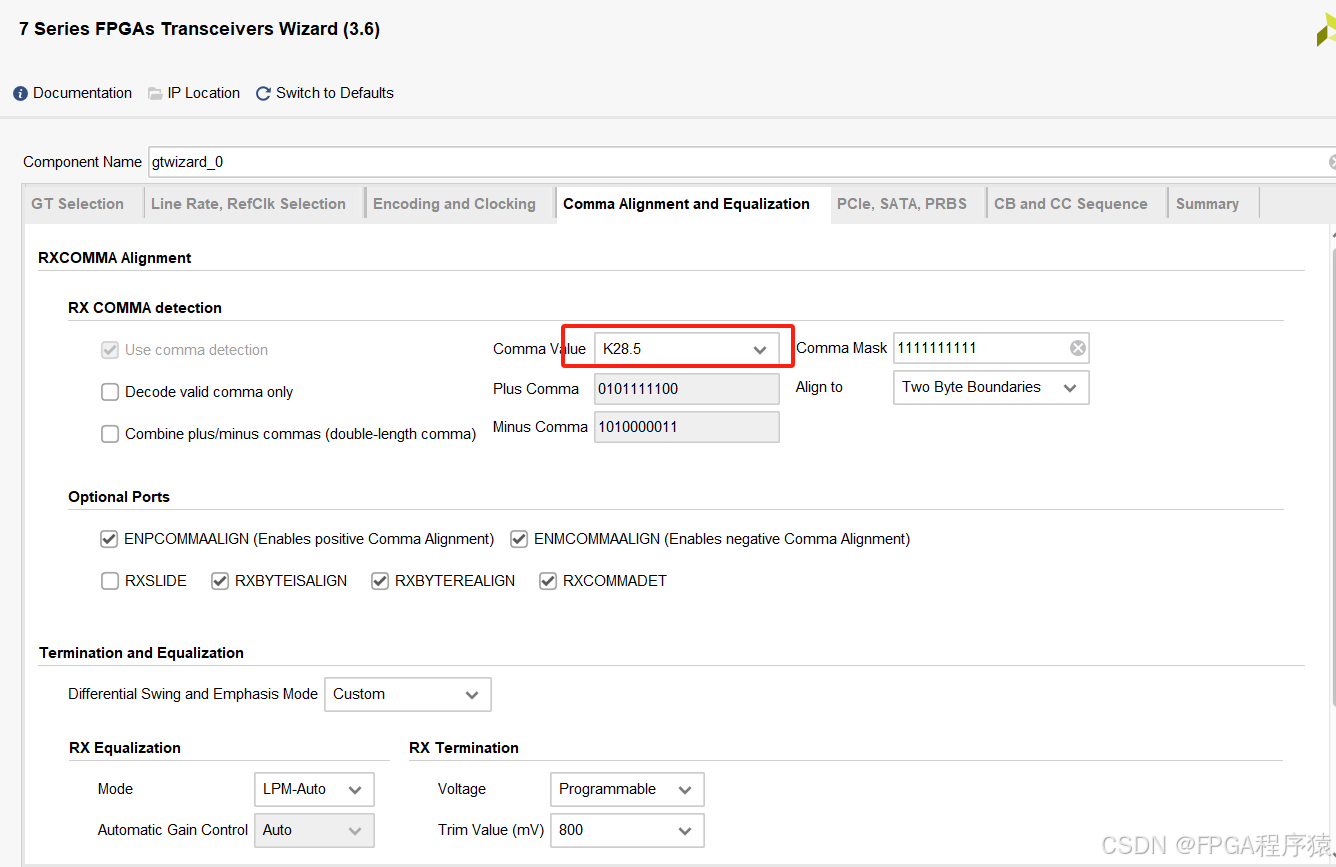

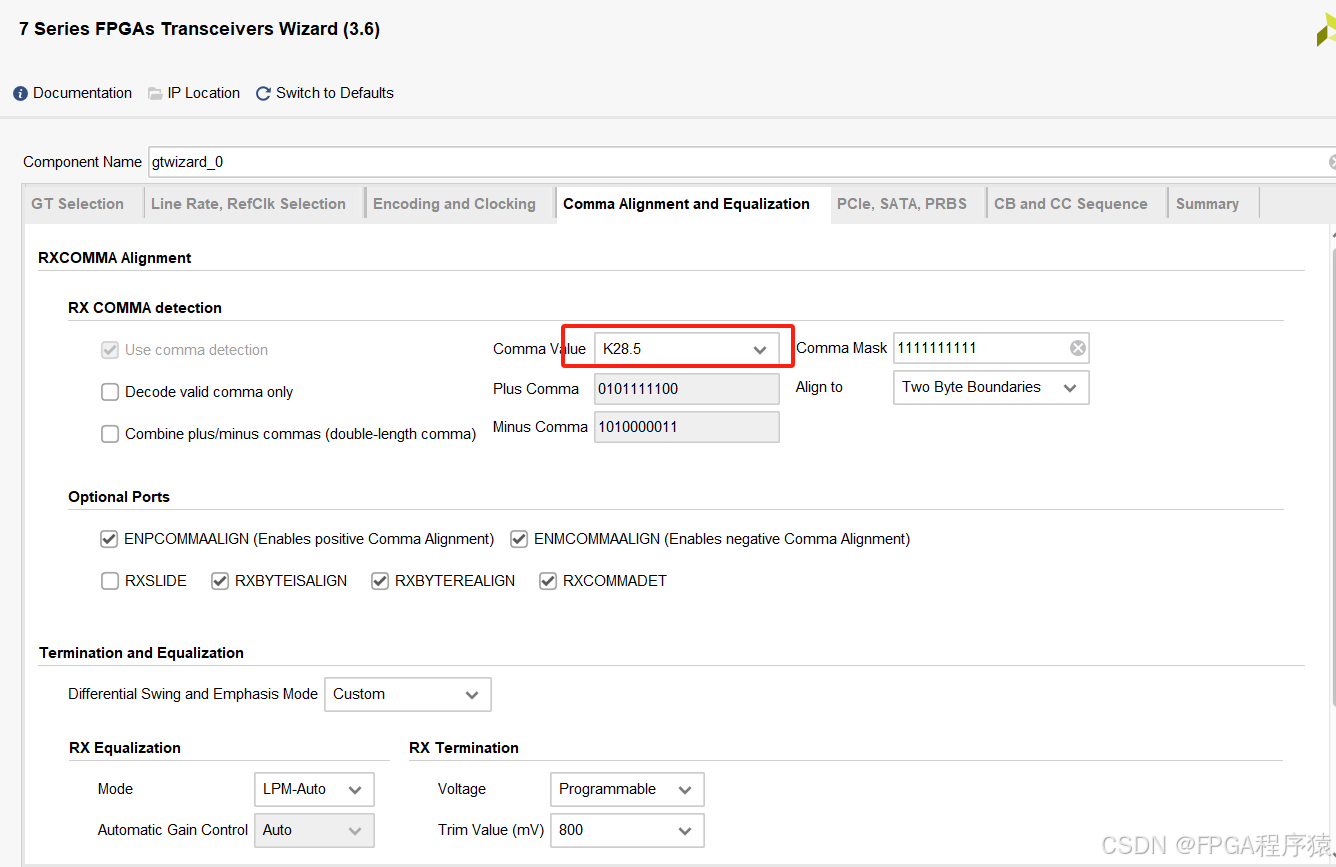

page4:

这里要引入 comma 码的概念。8B/10B 编码表中有 12 个控制字符,以大写字母 K 开头,用于一些控制功能。

K 码中的 comma 码用于接收端时钟校准和数据对齐,K28.5(对应用户数据为 16'hbc)最为常见, 所以本次实验将 comma 码设为 K28.5(逗号码)。串行收发器接收到一个一个的1bit数据,就像汉字一样,接收到一个一个的汉字。我们需要逗号把汉字隔开才能明白句子的意思,而数据也是一样;

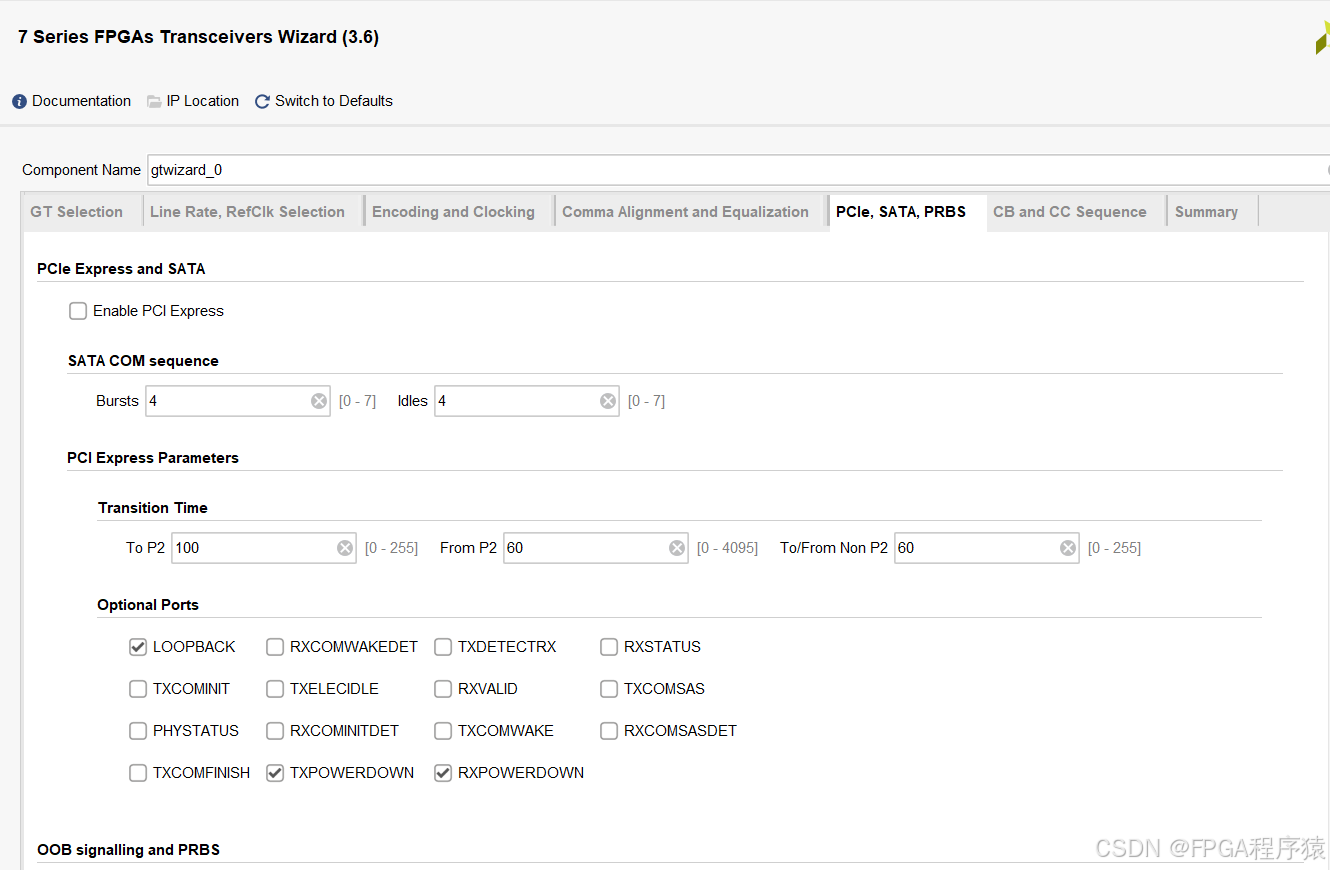

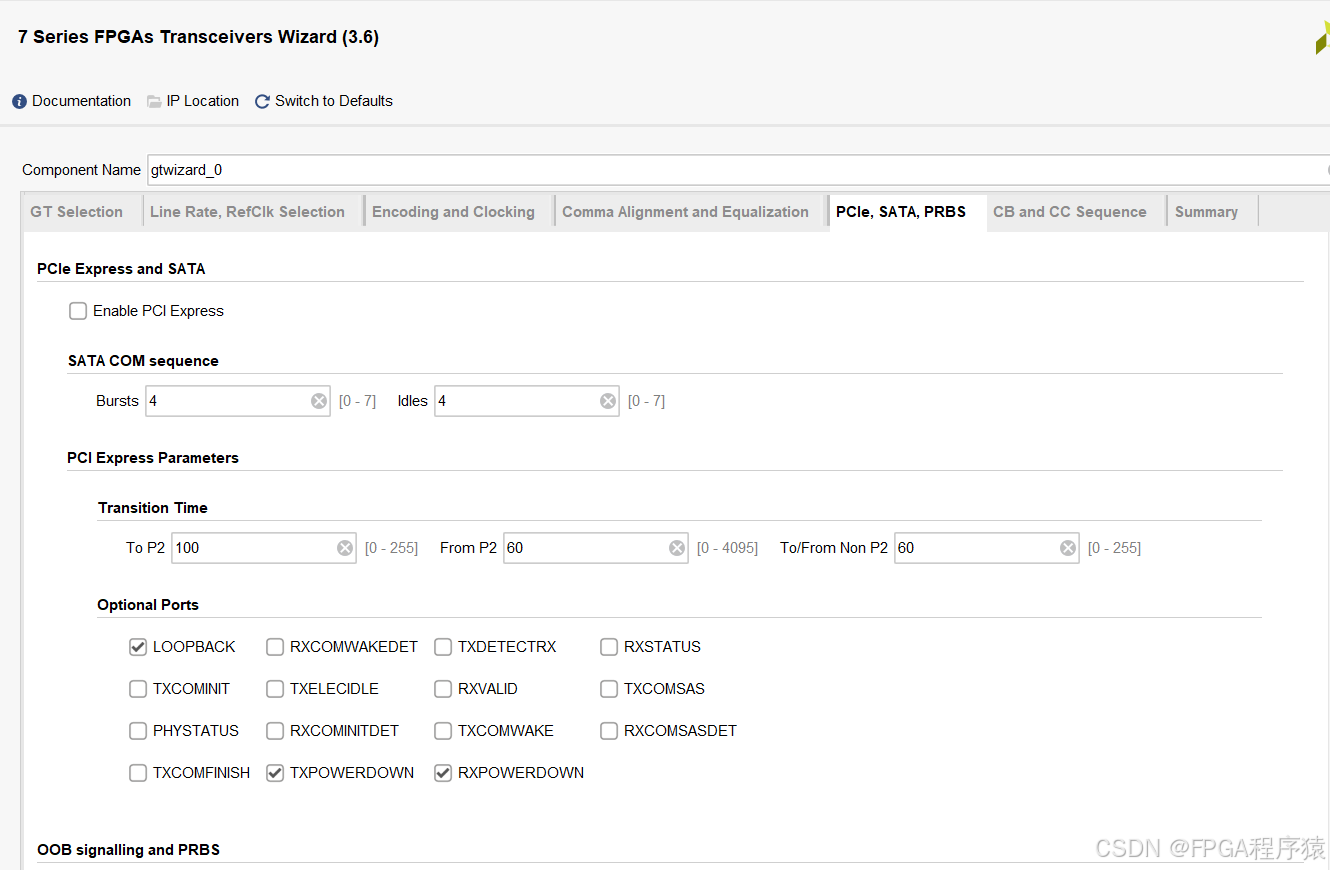

page5:

这一页说的都是 PCIE、SATA 和 PRBS 相关的内容,保持默认即可。

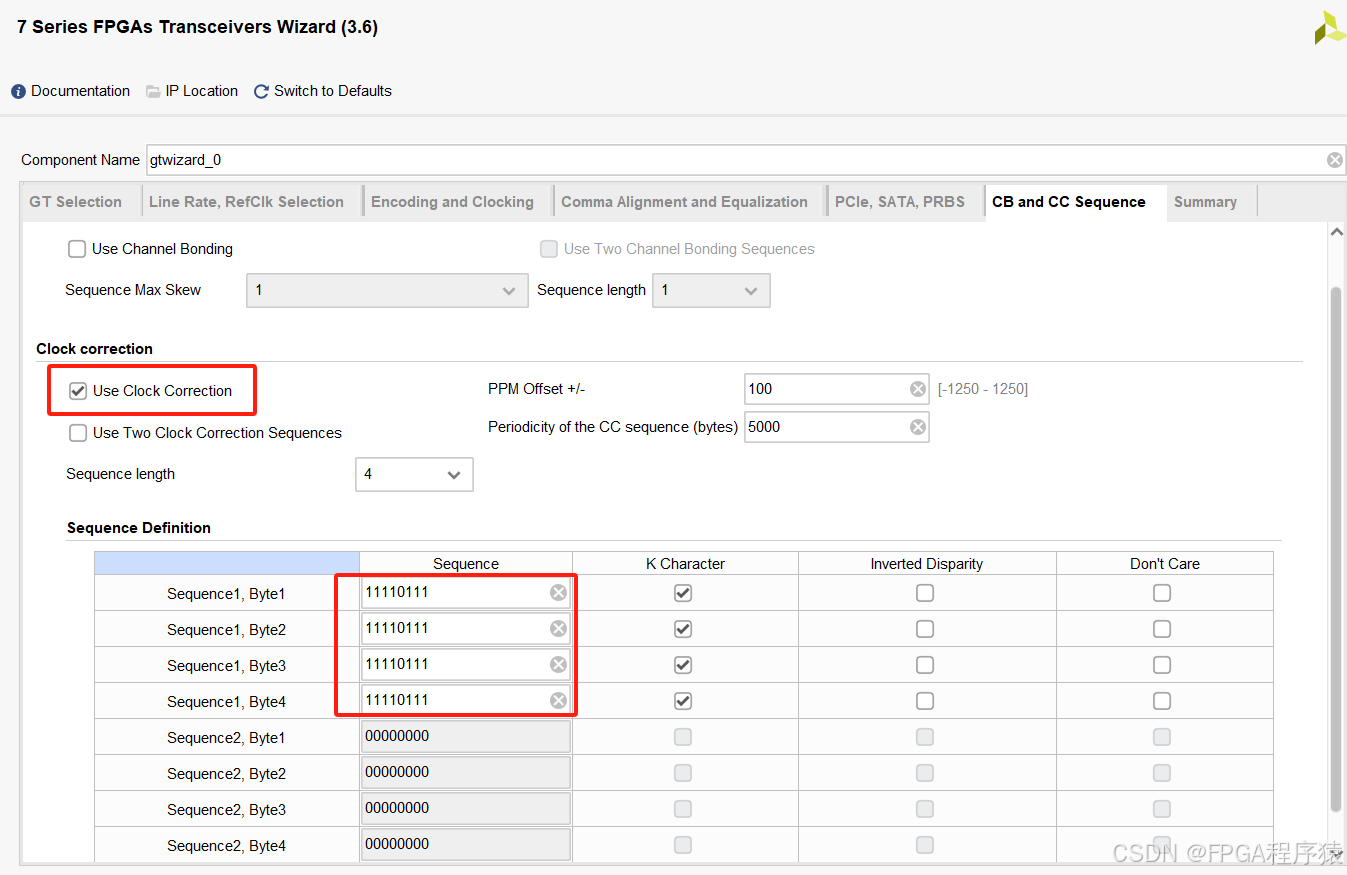

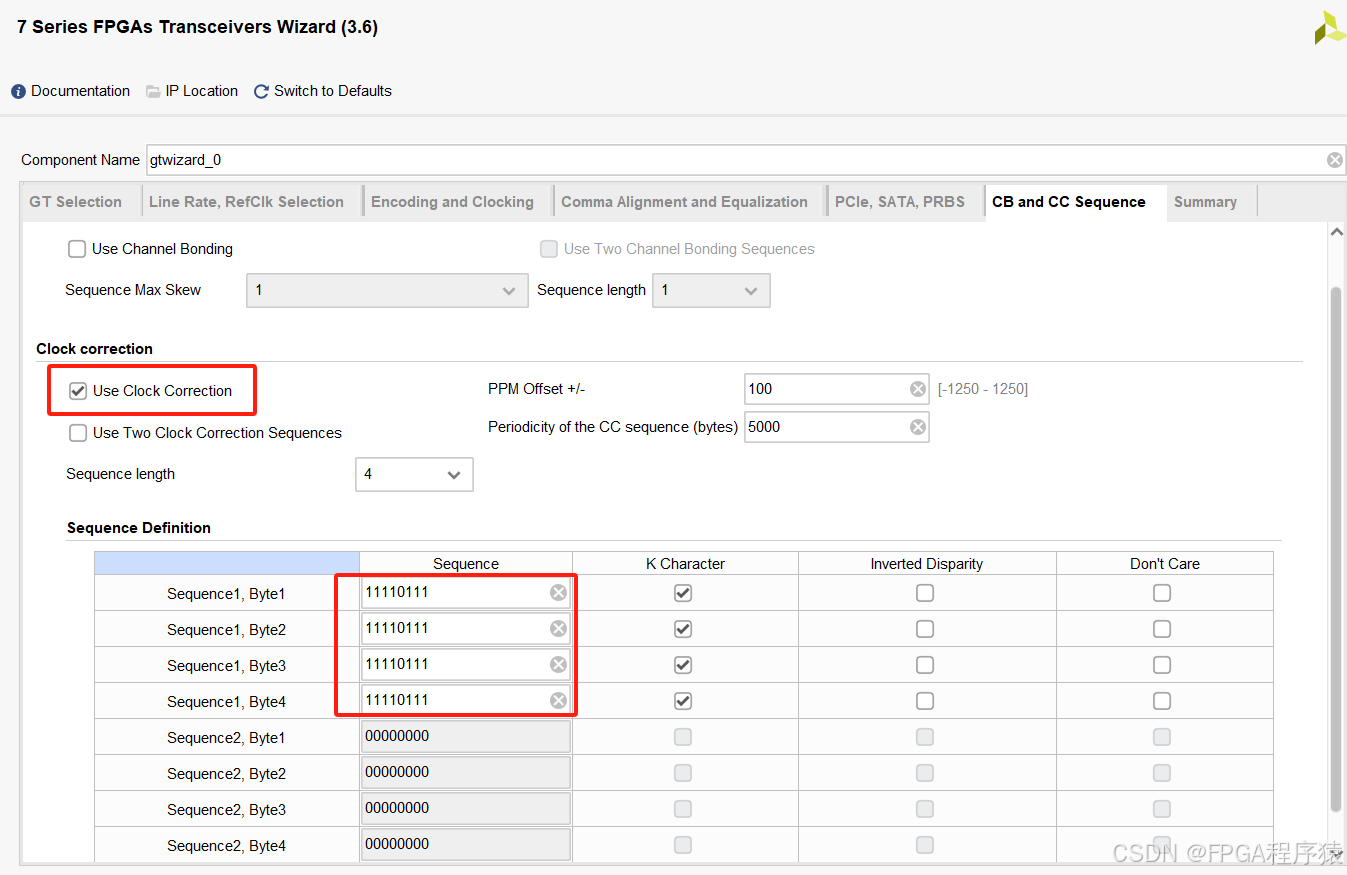

page6:

该选项卡用来选择时钟校正和通道绑定等参数,通道绑定一般用于多通道通信时,所以本次实验采用时钟校正的模式来保证数据的稳定接收。(Sequence默认配置值其实就是K27.7所对应的原码)具体二者有什么区别这里就不再赘述了。

page7:

此时大家看下页面所显示的参数与大家所设的是否一样,一样的话就点击 OK 选项。

3.生成IP Example 工程并做相应修改

用户可以把该 IP 看作是 FPGA 与光口交流信息的桥梁,当然这个“桥梁”的实现代码不需要用户自己写,Xilinx 官方已帮大家写好,并封装成了一 个 IP 供用户调用,用户只需要根据实际应用配置该 IP 即可。

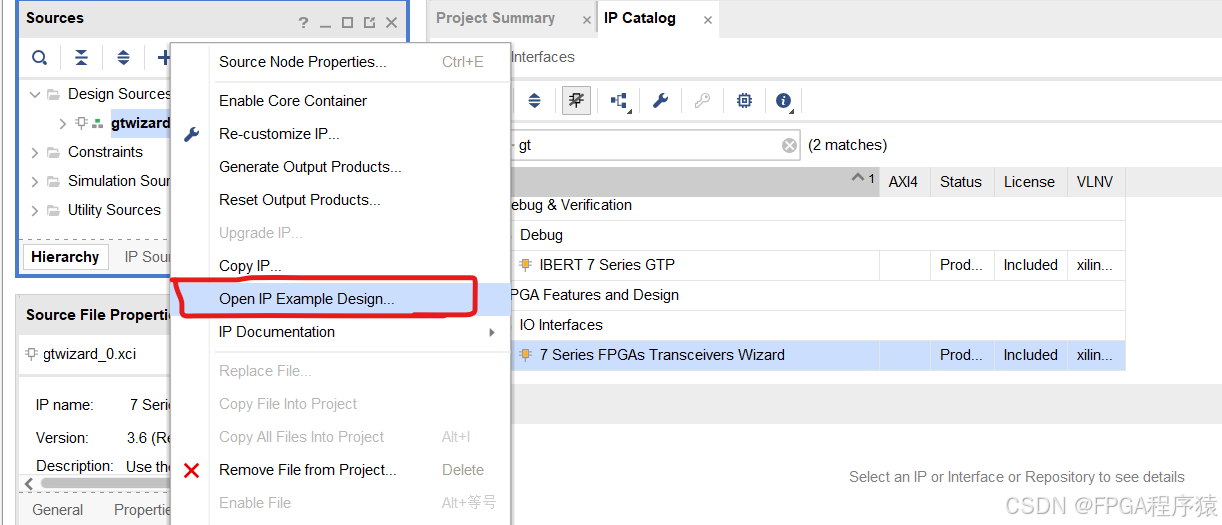

step1:配置IP核后,点击Open IP Example Design生成IP核的Example工程。

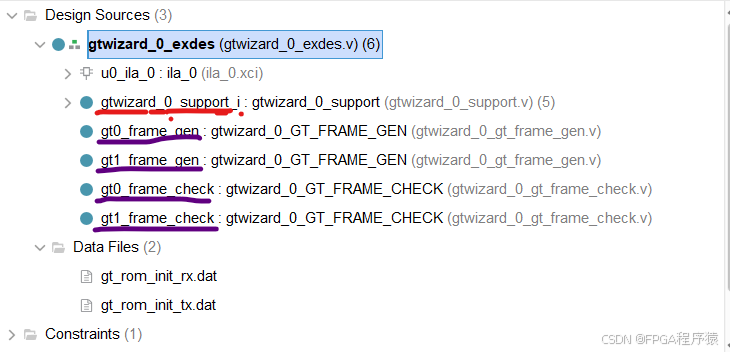

step2:打开Example工程,包含以下模块。

数据产生模块和接收数据模块以及时钟处理等模块。

ILA用于抓取信号检验环回是否成功。

●注:

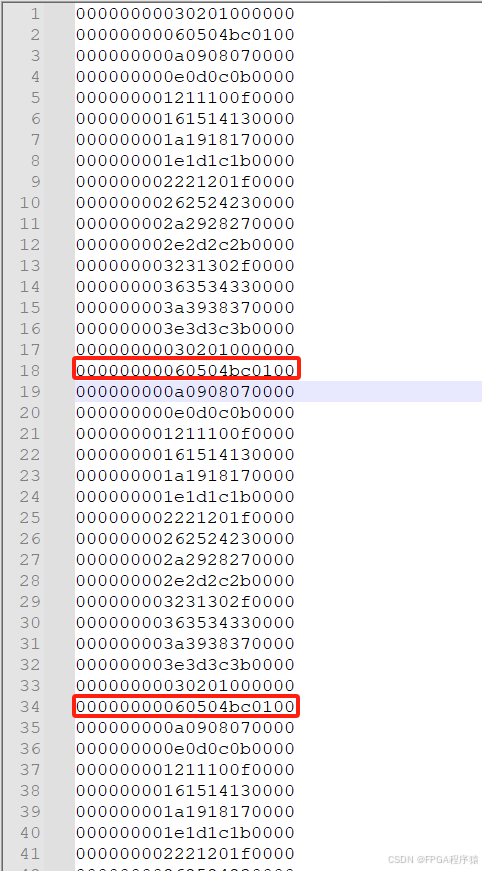

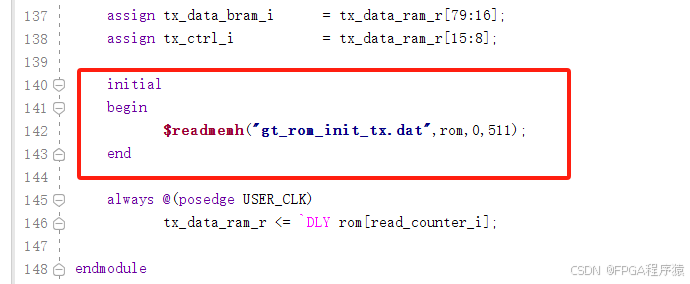

1.GT_FRAME_GEN为数据获取模块,在此模块中将本地文件gt_rom_init_tx.dat中的数据读取FPGA内部进行数据的传输。数据如下:

2.数据中BC为K码:K28.5,当K码出现时charisk信号为1(具体的16bit数据和charisk怎么从如下数据中提取出来的详细看GT_FRAME_GEN中代码)。如下:

在GT_FRAME_GEN模块中可以看出读入的数据长度为512。

代码中需要修改的地方

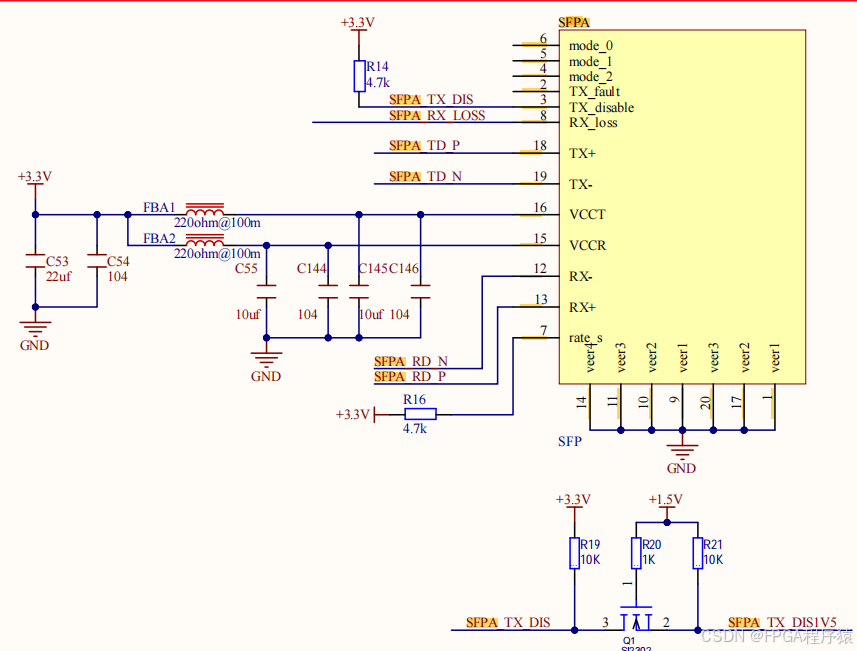

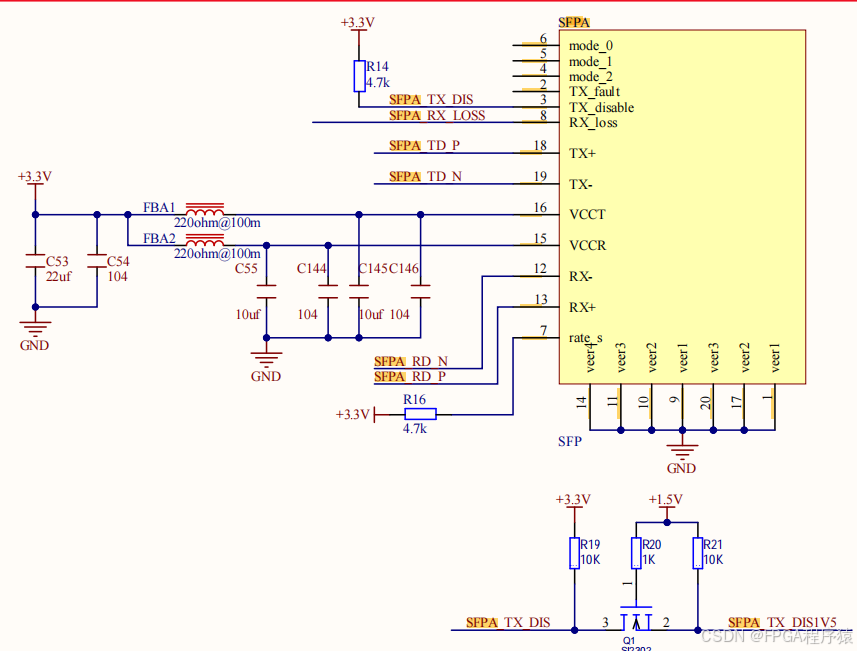

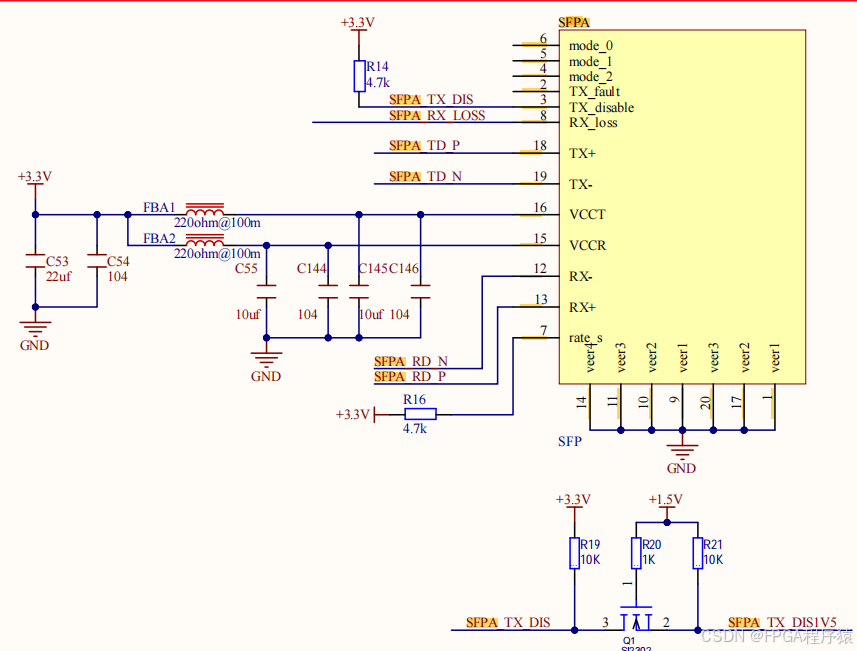

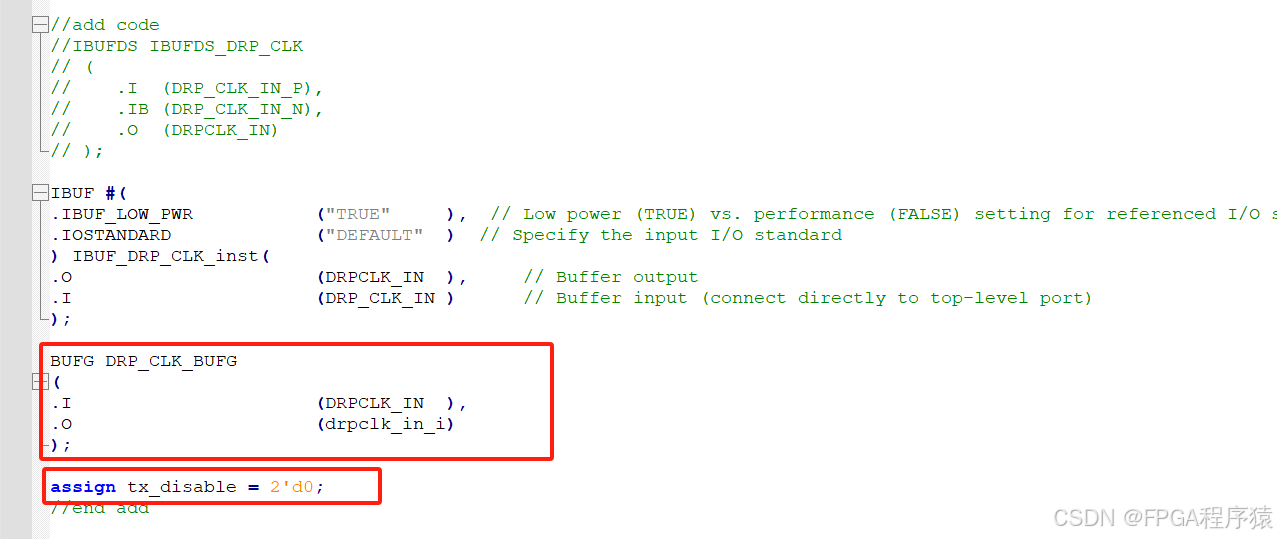

1.需要注意的是因为开发板在设计时将 tx_disable 信号接了个上拉电阻,要想环回实验正常进行就必须要将 tx_disable 信号赋 0。

2.原例程中 DRP 的输入时钟为差分时钟输入,而我们的开发板只带载了一个 50M 时钟的单端晶振,所以要将 DRP 的输入时钟改为单端时钟输入,这里需要用到单端时钟输入原语以及BUFG。

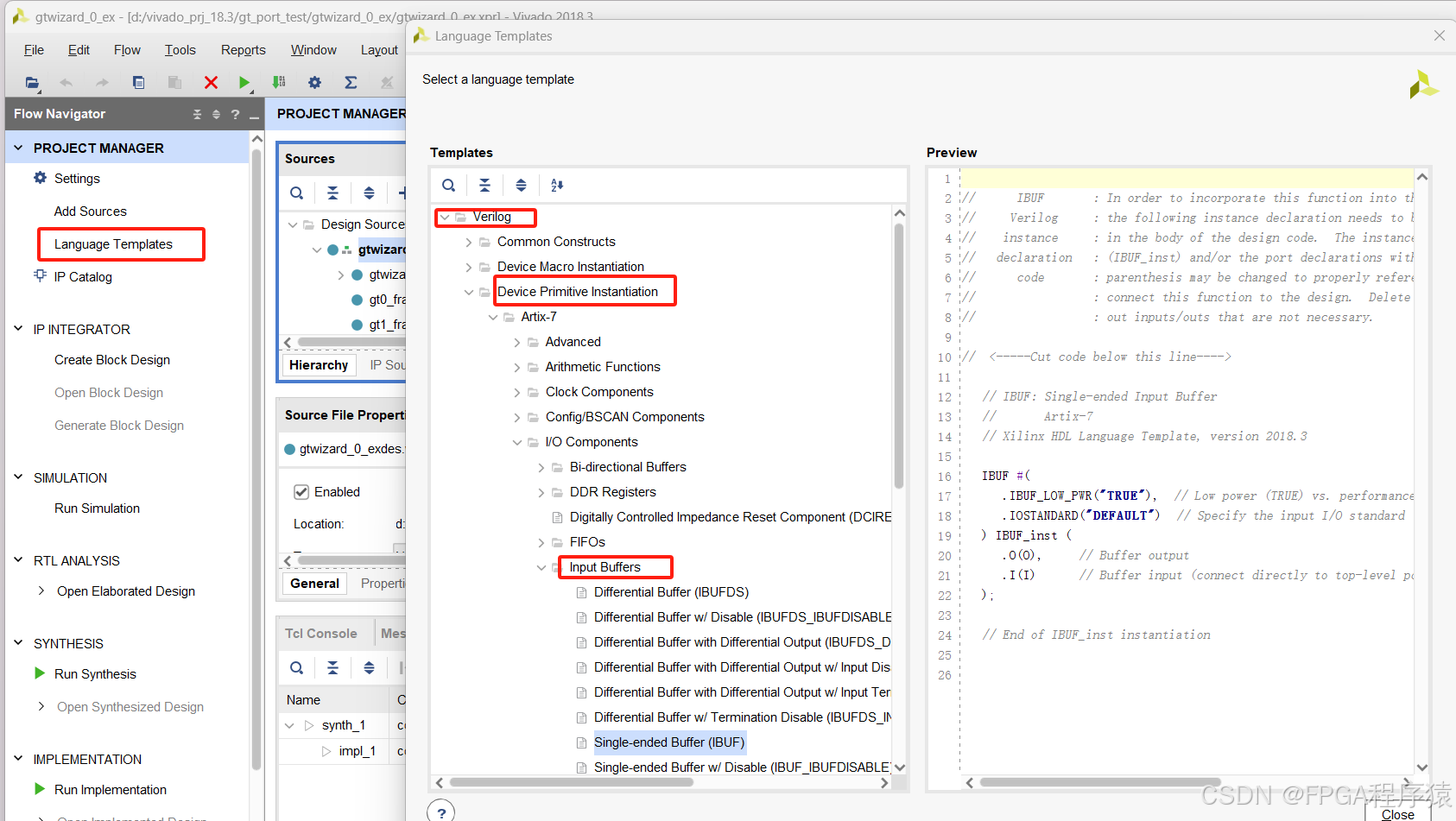

这里要将 IBUFDS 修改为 IBUF,那 IBUF 原语又是在哪里呢?

4.Implementation

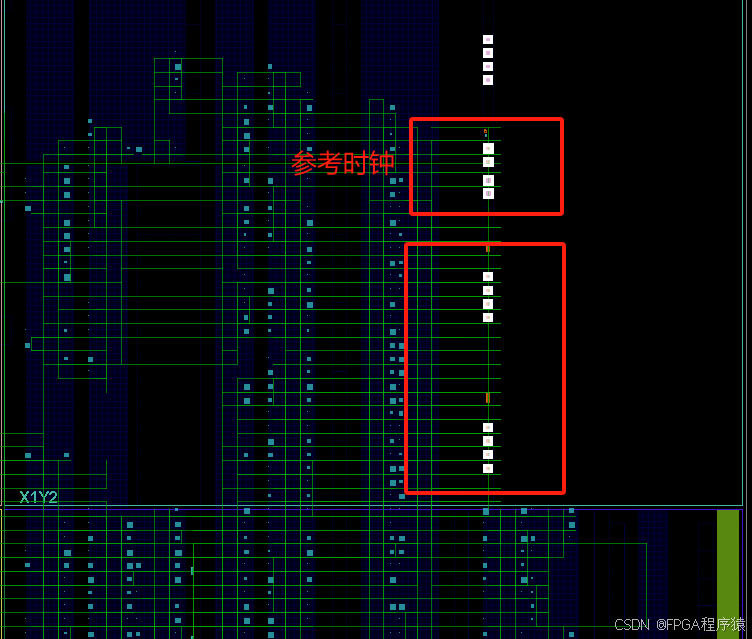

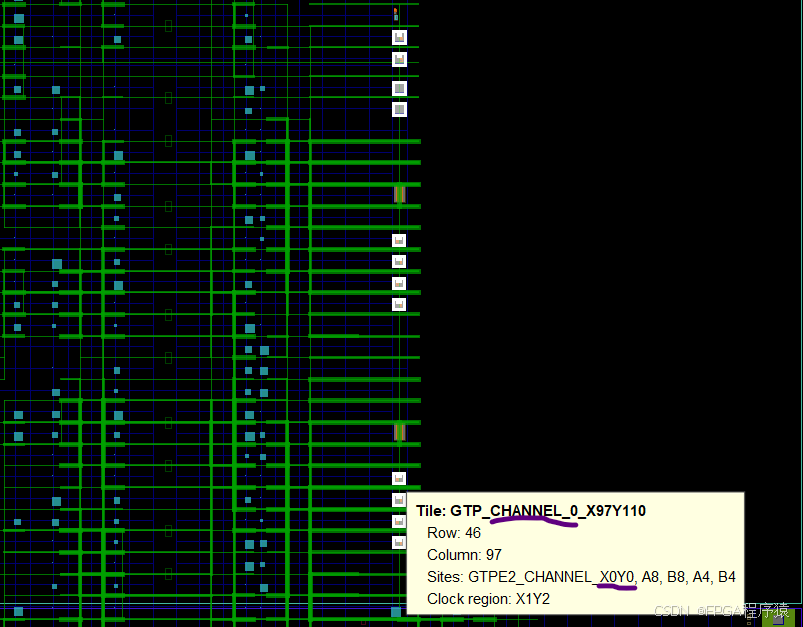

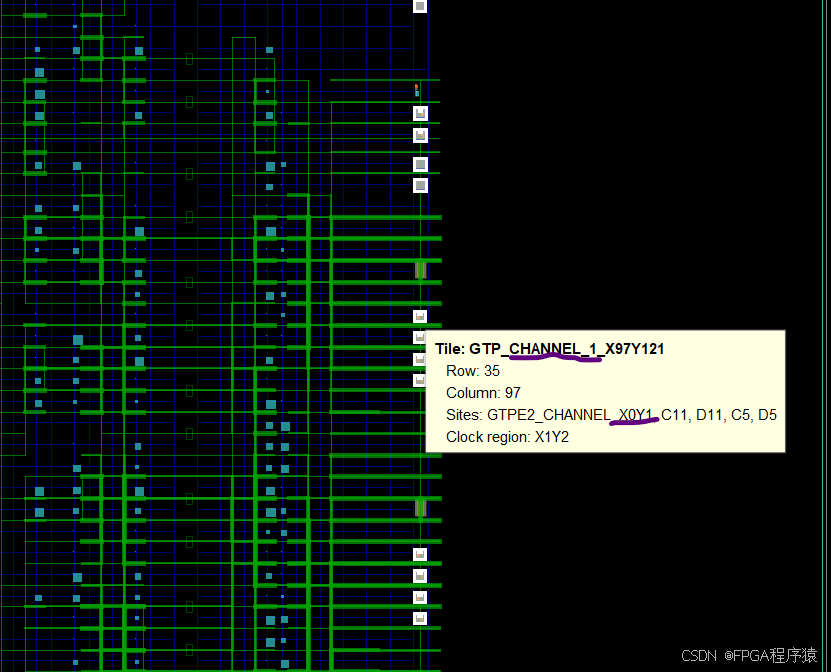

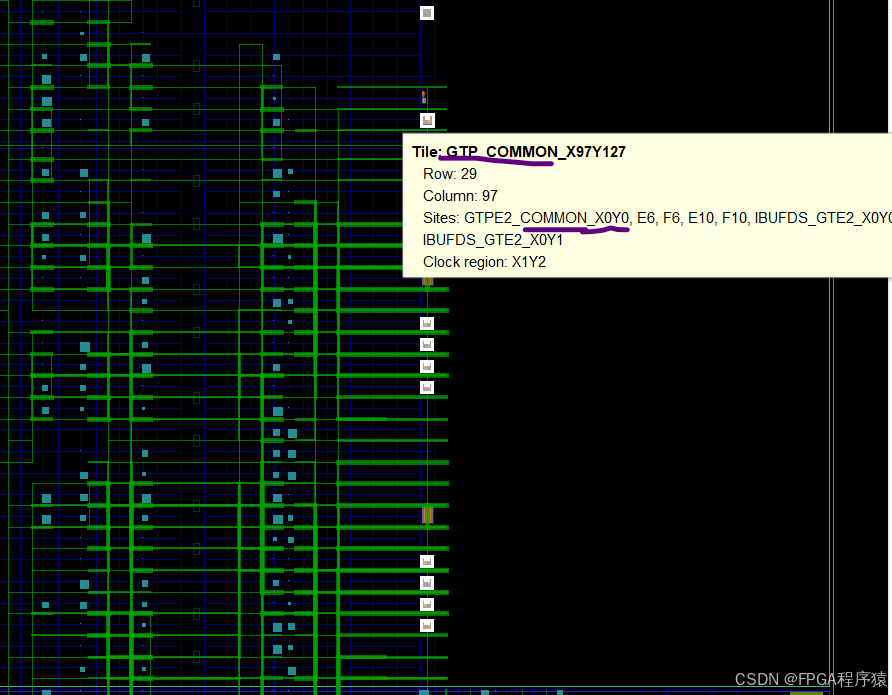

下面我们看一下实际当中的布局布线是怎样的:

显而易见,和我们配置IP核界面所约束的位置一致。

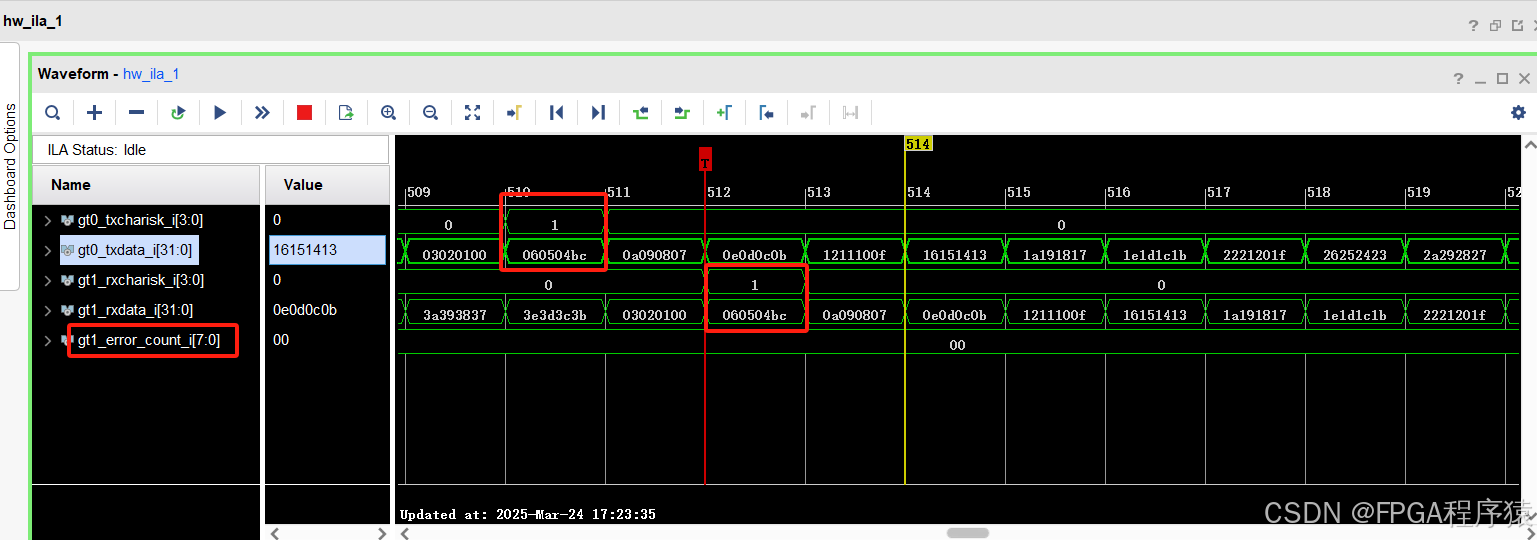

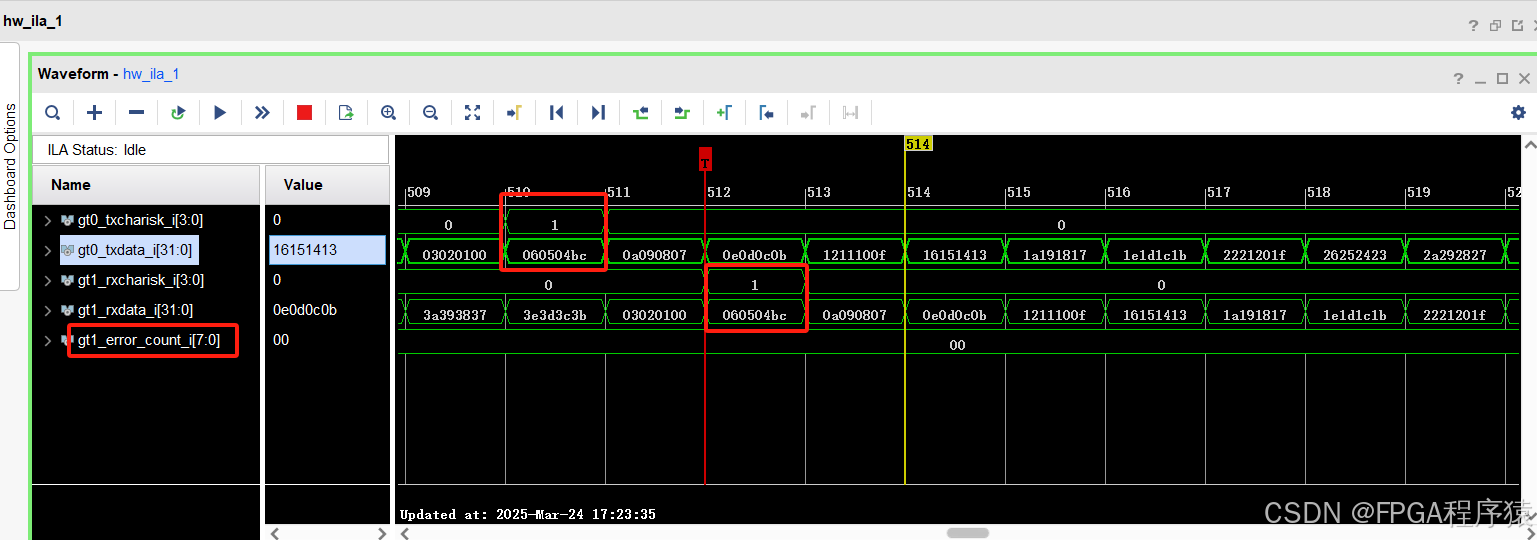

5.调试结果

rx 端代码中的gt0_error_count_i 信号一直为 0,说明光纤接口 8b10b 环回正确。

以上内容属于个人学习时的记录分享,旨在梳理思路,若有不当或错误,期待各位前辈能给予指导!

板载参考差分时钟,注意:后面在IP核勾选界面需要依据这个选择。

板载参考差分时钟,注意:后面在IP核勾选界面需要依据这个选择。

2058

2058

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?