HLS入门

文章目录

HLS

HLS是什么?与VHDL/Verilog编程技术有什么关系?

HLS(High-Level Synthesis)是一种技术,它允许开发者使用高级编程语言如C/C++来描述硬件设计,然后自动转换为硬件描述语言(HDL),例如VHDL或Verilog。这种技术使得软件开发人员能够利用他们现有的编程技能来设计和优化硬件结构,而无需深入了解底层硬件描述语言的细节。HLS与VHDL/Verilog编程技术的关系体现在互补关系、抽象层次不同、提高开发效率等方面。

HLS有哪些关键技术问题?目前存在什么技术局限性?

HLS(高层次综合)技术,在将高级语言如C/C++转换为RTL硬件描述语言的过程中,存在若干关键技术问题和技术局限性。关键技术问题主要体现在文件管理、性能优化和工具依赖等方面。而技术局限性则包括对平台依赖性、开发难度、性能与资源利用率等多个方面。

FPGA——HLS入门实践之led灯闪烁

创建工程

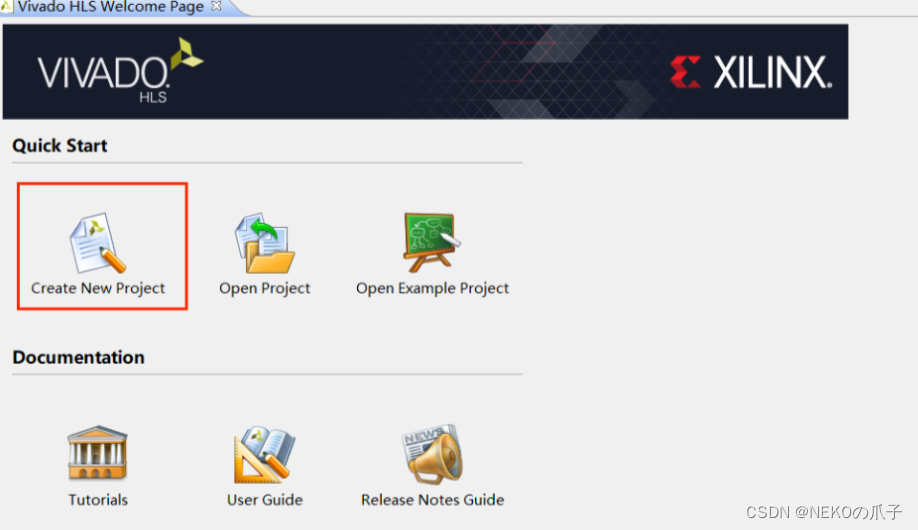

1.创建工程

图片1

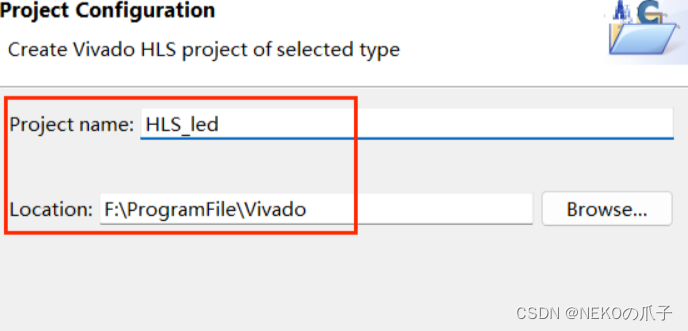

2.输入相关工程信息

图片2

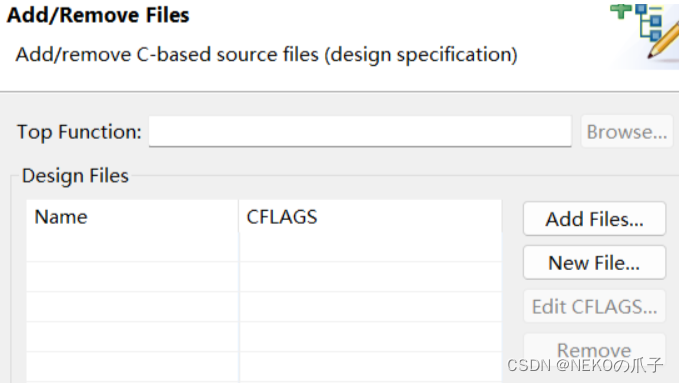

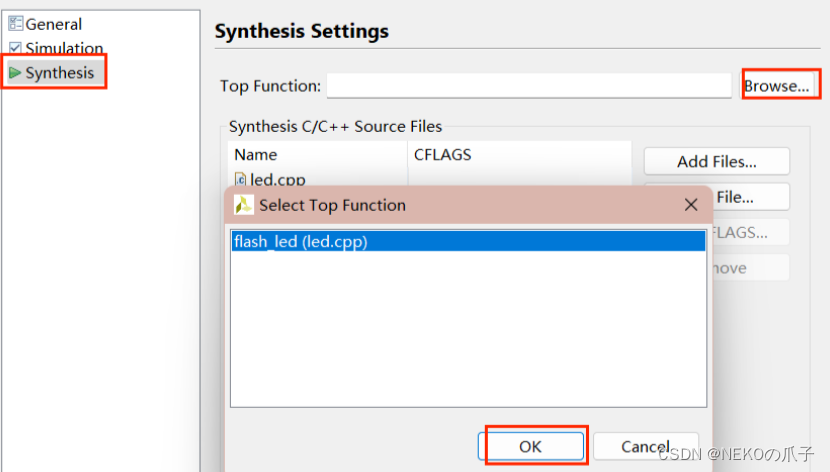

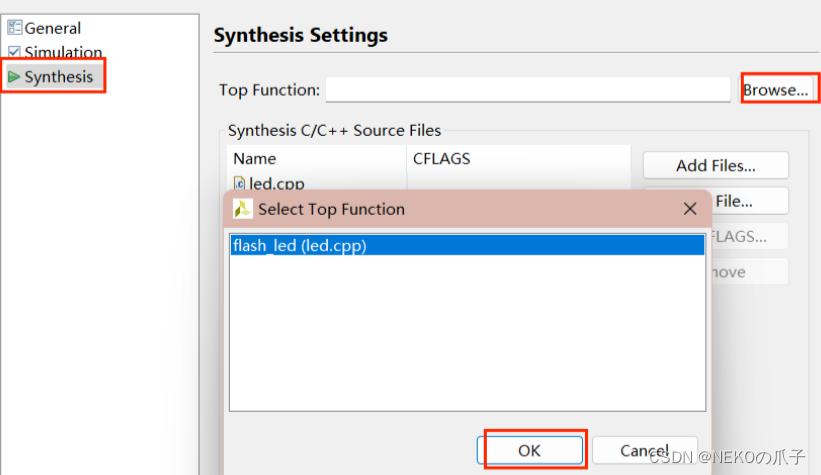

3.选择顶层函数

图片3

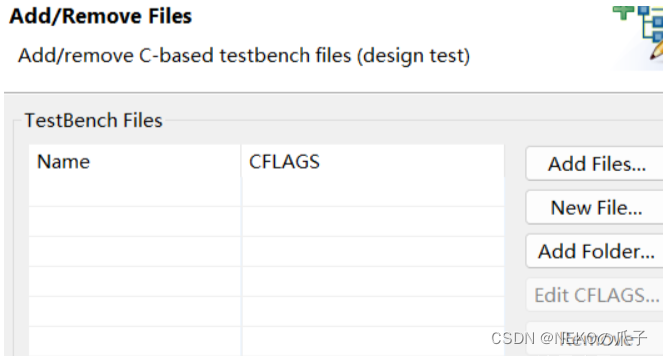

4.选择添加C仿真文件

图片4

5.选择器件

图片5

添加文件

1.添加源文件

led.h

``

#ifndef SHIFT_LED_H

#define SHIFT_LED_H

#include “ap_int.h”

#define CNT_MAX 100000000

//#define CNT_MAX 100,100M时钟频率下计数一秒钟所需要的计数次数

#define FLASH_FLAG CNT_MAX-2

// typedef int led_t;

// typedef int cnt_t;

typedef ap_int<1> led_t;

typedef ap_int<32> cnt_t;

void flash_led(led_t *led_o , led_t led_i);

#endif

``

led.cpp

``

#include “led.h”

void flash_led(led_t *led_o , led_t led_i){

#pragma HLS INTERFACE ap_vld port=led_i

#pragma HLS INTERFACE ap_ovld port=led_o

cnt_t i;

for(i=0;i<CNT_MAX;i++){

if(i==FLASH_FLAG){

*led_o = ~led_i;

}

}

}

``

添加仿真文件

test_led.cpp

``

#include “led.h”

#include <stdio.h>

int main(){

led_t led_i=0x01;

led_t led_o;

const int SHIFT_TIME = 4;

int i;

for(i=0;i<SHIFT_TIME;i++){

flash_led(&led_o , led_i);

led_i = led_o;

printf(“shift_out is %d \n”,(int)(led_o&0x01));

}

}

``

仿真

1.点击project->project settings->synthesis->browser->选择顶层函数

图片5

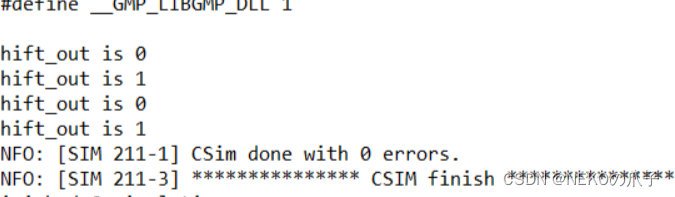

2.点击project->Run C Simulation

图片6

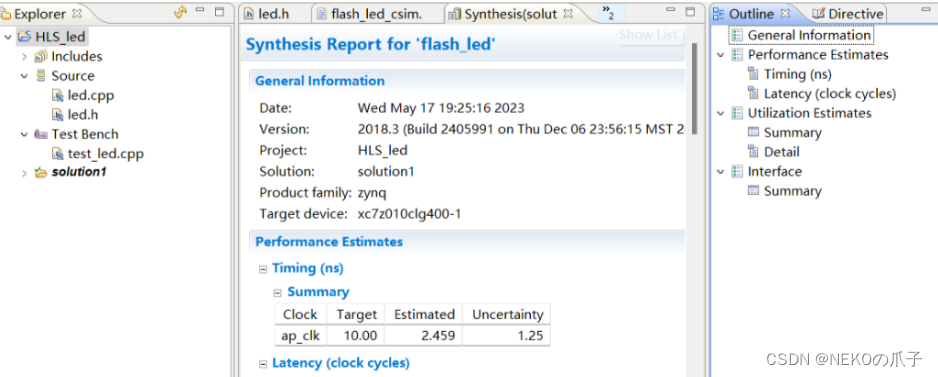

3.点击Solution->Run C Synthesis->Active Solution

图片7

总结

通过这次学习,我知道了HLS是什么,VHDL/Verilog编程技术有什么关系。我知道了许多之前没有接触了解过的新东西,使我产生了许多兴趣。同时,通过一次实践,我初步学习了如何使用该知识。

1000

1000

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?