有关边缘检测的两道题

一、Edgedetect

https://hdlbits.01xz.net/wiki/Edgedetect

(1)题目

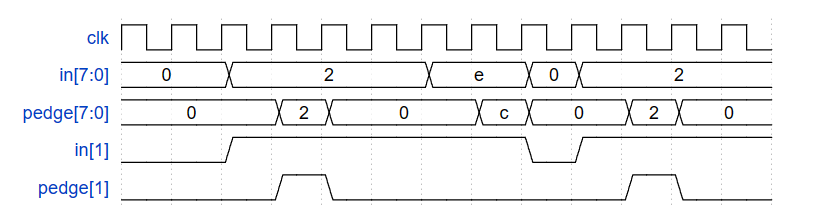

For each bit in an 8-bit vector, detect when the input signal changes from 0 in one clock cycle to 1 the next (similar to positive edge detection). The output bit should be set the cycle after a 0 to 1 transition occurs.

Here are some examples. For clarity, in[1] and pedge[1] are shown separately.

对于 8 位矢量中的每个位,检测输入信号何时从一个时钟周期的 0 变为下一个时钟周期的 1(类似于正边沿检测)。输出位应在发生 0 到 1 转换后的周期内设置。

(2)分析+代码

1. 设置一个last变量记录输入in的上一个状态

2. 我使用的for循环来比较每一位in和last的值,进而判断每一位pedge是否为1

module top_module (

input clk,

input [7:0] in,

output reg [7:0] pedge

);

reg [7:0] last=8'b0;

integer i;

always@(posedge clk)begin

for (i=0;i<8;i++)begin

if (last[i]==0&&in[i]==1)

pedge[i]=1;

else pedge[i]=0;

end

last=in;

end

endmodule

二、Edgecapture

https://hdlbits.01xz.net/wiki/Edgecapture

(1)题目

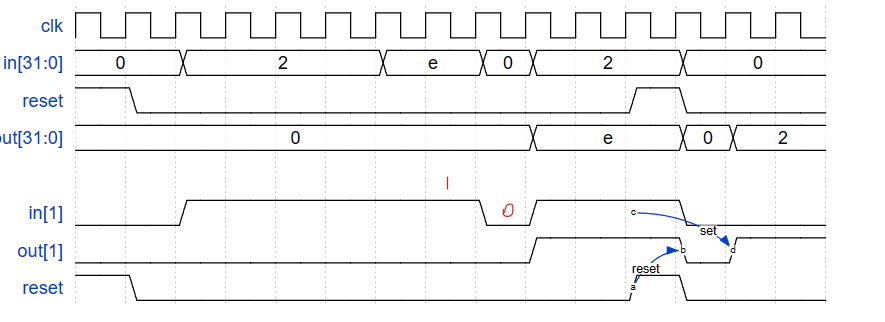

For each bit in a 32-bit vector, capture when the input signal changes from 1 in one clock cycle to 0 the next. "Capture" means that the output will remain 1 until the register is reset (synchronous reset).

Each output bit behaves like a SR flip-flop: The output bit should be set (to 1) the cycle after a 1 to 0 transition occurs. The output bit should be reset (to 0) at the positive clock edge when reset is high. If both of the above events occur at the same time, reset has precedence. In the last 4 cycles of the example waveform below, the 'reset' event occurs one cycle earlier than the 'set' event, so there is no conflict here.

In the example waveform below, reset, in[1] and out[1] are shown again separately for clarity.

(2)分析+代码

1. reset:当reset为1时,下一时刻的out为0.

2. out为1的条件:当前的in=0,上一时刻的in=1,则下一时刻的out=1;

或者上一场时刻的out为1时,下一时刻的out仍为1。

module top_module (

input clk,

input reset,

input [31:0] in,

output [31:0] out

);

reg [31:0] last=32'b0;

integer i;

always @(posedge clk)begin

if (reset==1) out<=0;

else begin

for(i=0;i<32;i++)begin

if ((last[i]==1&&in[i]==0)||(out[i]==1))

out[i]<=1;

else out[i]<=0;

end

end

last<=in;

end

endmodule

201

201

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?