目录

前言

延时模型+仿真激励信号

一、 Tb/and

(1)题目

You are given the following AND gate you wish to test:

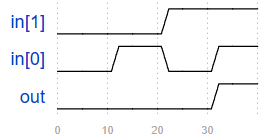

module andgate ( input [1:0] in, output out );Write a testbench that instantiates this AND gate and tests all 4 input combinations, by generating the following timing diagram:

(2)分析+代码

1. initial块通常用于在仿真开始时初始化一些变量或状态,或者在需要产生一些特定的初始激励信号时使用。

2. 仿真激励信号的产生:写一个波形发生器来测试模块。

例如本题中module top_module();中写了输入in的波形变化,来检验module andgate的功能。

module top_module();

reg [1:0] in;

reg out;

initial begin

in=2'b00;

#10 in=2'b01;

#10 in=2'b10;

#10 in=2'b11;

end

andgate andgate_i(in,out);

endmodule

二、Tb/tb2

(1)题目

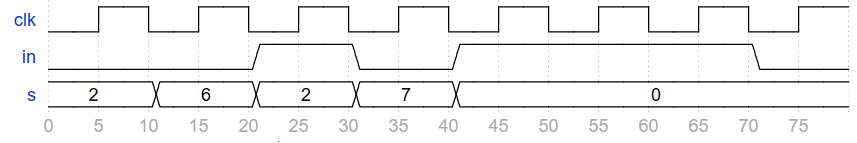

The waveform below sets clk, in, and s:

Module q7 has the following declaration:

module q7 ( input clk, input in, input [2:0] s, output out );Write a testbench that instantiates module q7 and generates these input signals exactly as shown in the waveform above.

(2)分析+代码

clk波形的简单写法:先要使用initial赋初值 initial clk=0;

然后是每5个时间单位反转一次:always #5 clk=~clk;

注意:这里不能用always @ (*)

module top_module();

reg clk;

reg in;

reg [2:0] s;

reg out;

initial clk=0;

always begin

#5 clk=~clk;

end

initial begin

in=0; s=2;

#10 in=0; s=6;

#10 in=1; s=2;

#10 in=0; s=7;

#10 in=1; s=0;

#30 in=0; s=0;

end

q7 q7_i(clk,in,s,out);

endmodule

170

170

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?