流水线含义

如1个器件加工需要三个步骤,1个人干,需要时间时间是t1+t2+t3;如果是流水线,将任务变成三个小模块,三个人每人负责一个模块,完成一个器件的时间就等于max(t1,t2,t3),效率就高了。

目的

速度换面积,提高运行速度。

实现方法

1、组合逻辑插入触发器,模块变小

如要完成

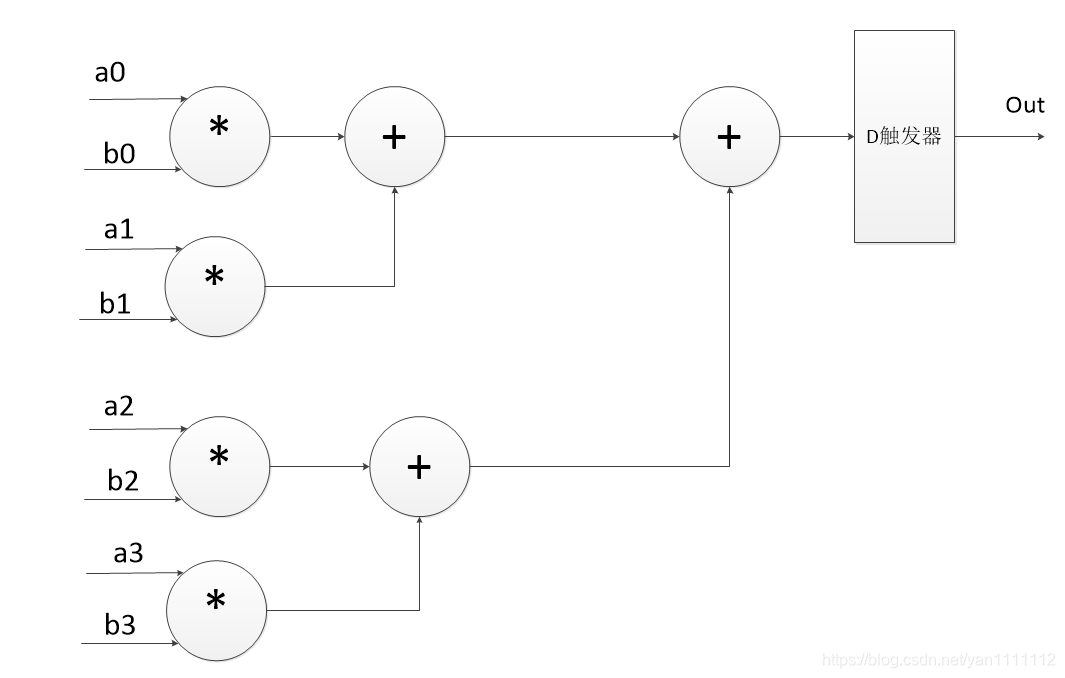

out=a0b0+a1b1+a2b2+a3b3;

1)直接写程序:

module head(

input clk,

input rst_n,

input [7:0] a0,a1,a2,a3,

input [7:0] b0,b1,b2,b3,

output reg [15:0] out

);

always@(posedge clk or negedge rst_n)

begin

if(!rst_n)

out<=0;

else

out<=a0*b0+a1*b1+a2*b2+a3*b3;

end

endmodule

RTL图参看我的文章

fpga速度(流量、时滞、时序)

流量:16/1。一个周期处理16位

时滞:1个周期

时序:一个乘法器加三个加法器的延时

2)并行化

out=(a0b0+a1b1)+(a2b2+a3b3);

module head(

input clk,

input rst_n

本文介绍了FPGA中的流水线设计原理,旨在提高运行速度。通过组合逻辑插入触发器和拆开环路等方法,实现了模块并行化,从而减少了处理时间。流水线设计允许在一个周期内处理更多数据,提高了流量,而并行处理则显著加快了运算速度。

本文介绍了FPGA中的流水线设计原理,旨在提高运行速度。通过组合逻辑插入触发器和拆开环路等方法,实现了模块并行化,从而减少了处理时间。流水线设计允许在一个周期内处理更多数据,提高了流量,而并行处理则显著加快了运算速度。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

212

212

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?