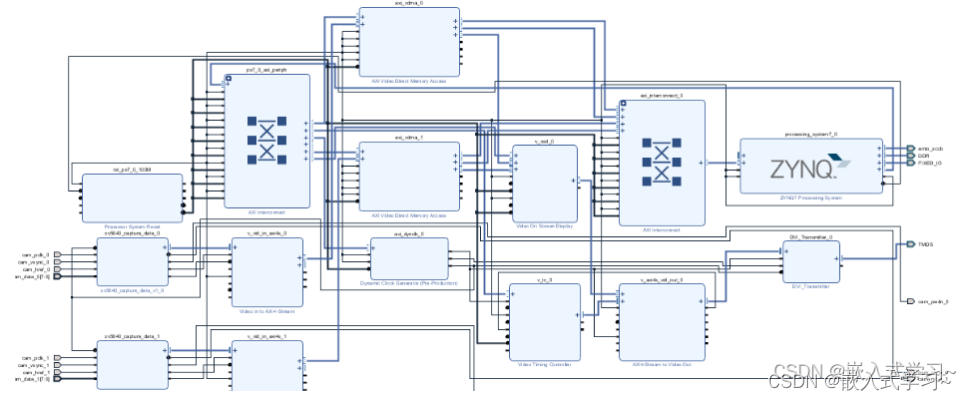

项目框架

本项目使用的开发板为zynq7020,框架为正点原子提供的hdim显示双目摄像头例程,

并在此基础上进行双目视觉处理,最终生成视差图和深度图; 所有双目视觉处理部分均在pl端采用Verilog实现

视差缓存

在左右图像的census计算完成之后会获得左目的5*5的windows窗口

input [24:0] data_in_L,//WIndows input [24:0] data_in_R,//WIndows

在获取到窗口后需要定义一个最大视差范围,这里我选择的是64,并且以左目相机为基准计算代价空间,这就需要对右目数据进行缓存,共需要缓存64个Windows,我这里直接选择用寄存器缓存

//============= 缓存 视差范围内的census向量 以便并行处理========================

integer i;

reg [24:0] census_array_L [0:`MAX_DISP-1];

reg [24:0] census_array_R [0:`MAX_DISP-1];

always@(posedge clk,negedge rst_n)begin

if(~rst_n)begin

for (i=0;i<`MAX_DISP;i=i+1)begin

census_array_L[i]<=0;

census_array_R[i]<=0;

end

end

else if(data_in_L_valid)begin

census_array_R[0]<=data_in_R; //第一拍

census_array_L[0]<=data_in_L;

for (

文章详细描述了在Zynq7020开发板上使用HDI-M框架进行双目摄像头视觉处理的过程,包括Census计算、视差缓存、汉明距离计算以及最终的视差图和深度图生成。FPGA被用于PL端的Verilog实现,通过异或运算和多步加法优化视差计算。

文章详细描述了在Zynq7020开发板上使用HDI-M框架进行双目摄像头视觉处理的过程,包括Census计算、视差缓存、汉明距离计算以及最终的视差图和深度图生成。FPGA被用于PL端的Verilog实现,通过异或运算和多步加法优化视差计算。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

3622

3622

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?