一.为什么需要复位?

①主要是为了确保FPGA在启动时处于已知状态,以便正确地执行其功能。

②复位还可以用于在FPGA运行时重新启动系统或清除错误状态。同时,复位的存在也会对FPGA的综合面积产生影响,需要在设计中合理考虑复位电路的设计,避免资源的浪费和消耗。

二.复位的方式

在FPGA设计过程中,分为外部复位和内部复位:

内部复位和外部复位都是用来实现FPGA的复位功能的。

外部复位是指复位信号主要来自外部引脚的输入,如复位按钮,电源模块输出等;

内部复位主要由FPGA内部电路产生。

总的来说:内部复位可以更加精确地控制复位的时序和复位的范围,而外部复位则受限于外部电路的设计和实现。

三.同步复位和异步复位

| 同步复位 | 异步复位 | |

| 特点 | 复位信号只有时钟上升沿或者下降沿到来时才有效 | 无论时钟边沿是否到来,只要复位信号有效,就进行复位 |

| Verilog描述 | always@(posedge clk) | always@(posedge clk,negedge rst_n) |

| 优点 | 1.有利于仿真 | 1.大多数的逻辑器件的目标库内的DFF都有异步复位端口,可以节省资源 2.设计相对简单 3异步复位信号识别方便,而且可以很方便的使用FPGA的全局复位端口 |

| 缺点 | 1.复位信号的有效时长必须大于时钟周期,才能真正的被系统识别并完成复位任务。 | 1.复位信号容易受到毛刺的影响 2.复位信号释放的过程中容易出现问题(若复位释放在时钟有效沿附近时,很容易使寄存器输出出现亚稳态) |

| 总结 | 推荐使用异步复位,同步释放,而且复位信号为低电平有效 | |

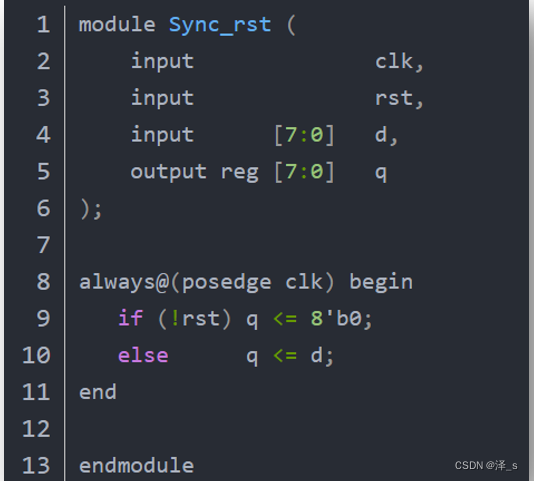

(1)同步复位

同步复位是指在时钟上升沿或下降沿时,根据复位信号的状态确定是否对系统进行复位。

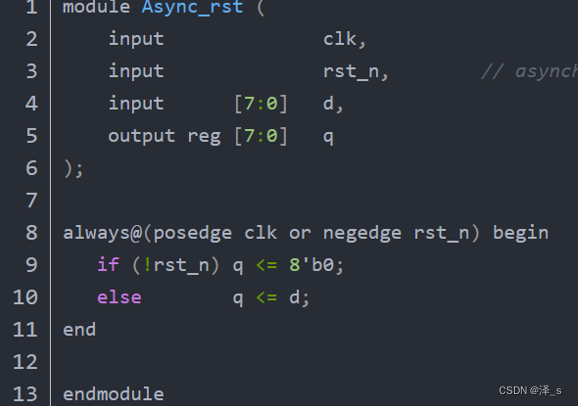

(2)异步复位

异步复位是指无论时钟信号处于何种状态,只要复位信号有效,就对系统进行复位。

复位信号释放的随机性,可能导致时序违规,倘若复位释放时恰恰在时钟有效沿附近,就很容易使电路处于亚稳态

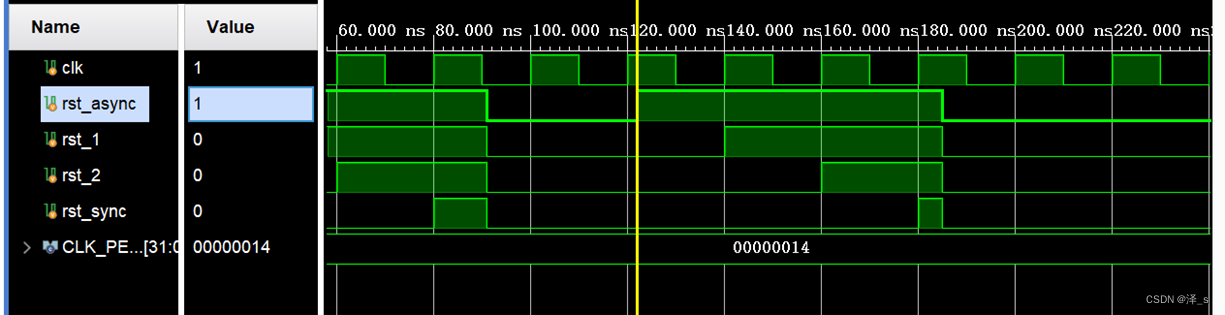

(3)同步复位异步释放

异步复位同步释放是一种FPGA设计方法,通常用于确保电路在重新启动后能够正常工作。在异步复位同步释放的设计中,一组异步复位信号用于重置电路的状态,而另一组同步释放信号则用于释放电路的状态。这种设计方法是在采用复杂的操作逻辑或时钟信号时,需要保证电路的可靠性和可重复性的一种必要措施。

在异步复位同步释放设计中,当发生复位时,电路中所有的寄存器和状态都会被清零,以保证电路的初始状态是正确的。然而,由于信号延迟和时序问题,复位信号可能无法同步到电路中的每个寄存器和状态中。这就可能导致一些不稳定性或不可预期的问题,因此需要同步释放信号来释放电路的状态。同步释放信号通常用来告诉电路,所有的复位操作已经完成,可以在正确的时刻重新启动电路。

总之,异步复位同步释放是一种FPGA设计方法,用于确保电路在重新启动后能够保持正确的状态,并在正确的时刻重新启动。它是保证电路可靠性和可重复性的必要措施,在复杂的操作逻辑或时钟信号时使用。

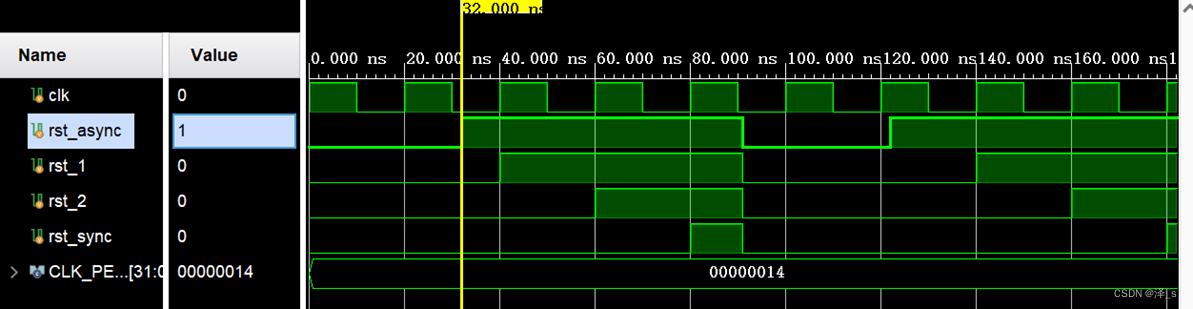

下面是仿真测试的代码:

module reset_test(

input clk,

input rst_async,

output reg rst_sync

);

reg rst_1;

reg rst_2;

always@(posedge clk or negedge rst_async)begin

if(!rst_async)begin

rst_1 <= 1'b0 ;

rst_2 <= 1'b0 ;

rst_sync <= 1'b0 ;

end

else begin

rst_1 <= 1'b1 ;

rst_2 <= rst_1;

rst_sync <= rst_2;

end

end

endmoduleTB文件:

module tb_reset_test;

reg clk ;

reg rst_async ;

reg rst_sync ;

//模块例化

reset_test u_reset_test(

/*input*/ .clk (clk),

/*input*/ .rst_async (rst_async),

/*output reg*/ .rst_sync ( rst_sync)

);

//时钟

localparam CLK_PERIOD = 20;

initial clk = 1'b1;

always #(CLK_PERIOD/2)

assign clk=~clk;

//激励

initial begin

rst_async = 1'b0;

#(32);

rst_async = 1'b1;

#(59);

rst_async = 1'b0;

#(31);

rst_async = 1'b1;

#(63);

rst_async = 1'b0;

end

endmodule仿真波形:

本文详细讨论了FPGA复位的重要性,包括复位功能的目的、外部和内部复位的区别、同步复位与异步复位的特点及其在电路设计中的选择。异步复位同步释放被推荐用于确保电路的可靠性和可重复性,通过实例代码展示了其实现方法和仿真测试。

本文详细讨论了FPGA复位的重要性,包括复位功能的目的、外部和内部复位的区别、同步复位与异步复位的特点及其在电路设计中的选择。异步复位同步释放被推荐用于确保电路的可靠性和可重复性,通过实例代码展示了其实现方法和仿真测试。

1974

1974

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?