1、RTL设计图

2、Quartus扫描生成的电路RTL图

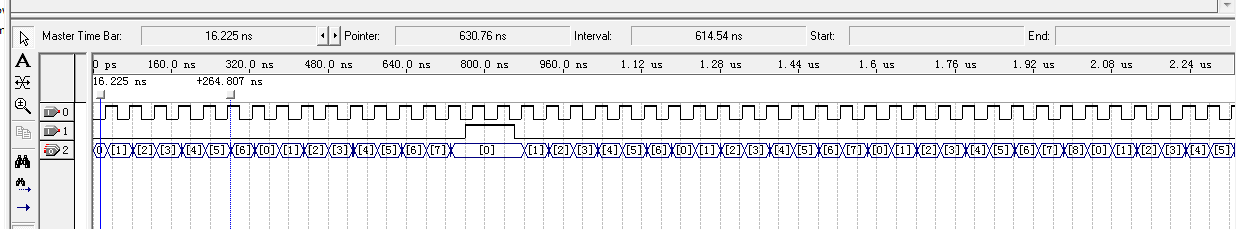

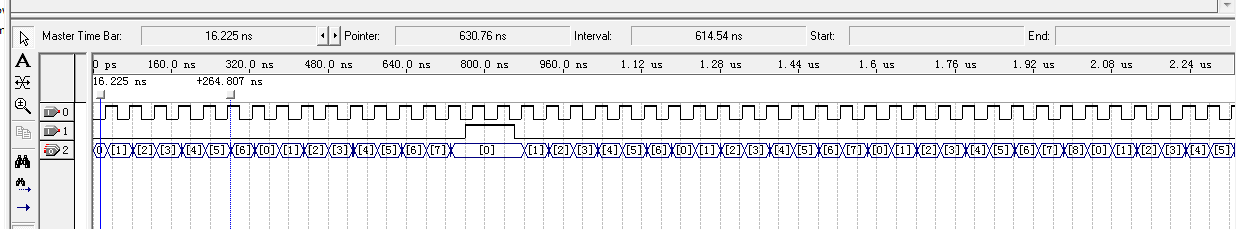

3、计数器的波形仿真截图

4、计数器代码

module count(

RST , // 异步复位, 高有效

CLK , // 时钟,上升沿有效

CNTVAL); // 输出的计数值信号

input RST , CLK ;

output [3:0] CNTVAL;

reg [3:0] CNTVAL, CNT_MAX_VAL = 6;

always @(posedge CLK  本文详细介绍了使用Quartus进行变模循环计数器的RTL设计,展示了扫描生成的电路RTL图,并通过波形仿真截图验证了计数器的正确工作。同时提供了计数器的源代码。

本文详细介绍了使用Quartus进行变模循环计数器的RTL设计,展示了扫描生成的电路RTL图,并通过波形仿真截图验证了计数器的正确工作。同时提供了计数器的源代码。

1、RTL设计图

2、Quartus扫描生成的电路RTL图

3、计数器的波形仿真截图

4、计数器代码

module count(

RST , // 异步复位, 高有效

CLK , // 时钟,上升沿有效

CNTVAL); // 输出的计数值信号

input RST , CLK ;

output [3:0] CNTVAL;

reg [3:0] CNTVAL, CNT_MAX_VAL = 6;

always @(posedge CLK  4714

4714

6626

6626

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?