名称:基于FPGA的计数器设计VHDL代码Quartus仿真(文末获取)

软件:Quartus

语言:VHDL

代码功能:

期末考核

设计一个异步清零同步置可逆计数器,要求如下:

1.计数范围:0~N,N为 ...

2.具有工作模式控制端:复位端、预置数控制端、计数使能端,计数方式控制端(控制递增或递减计数),并需要给出功能表

3.设计完后进行功能仿真,并结合功能表对仿真结果进行分析。

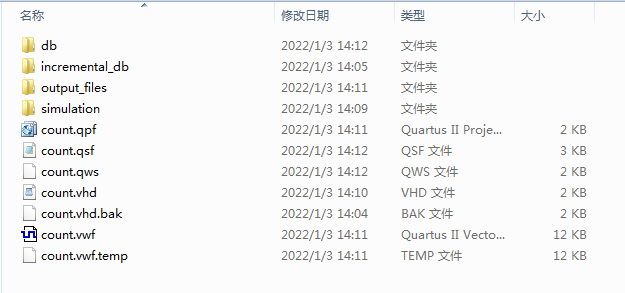

1. 工程文件

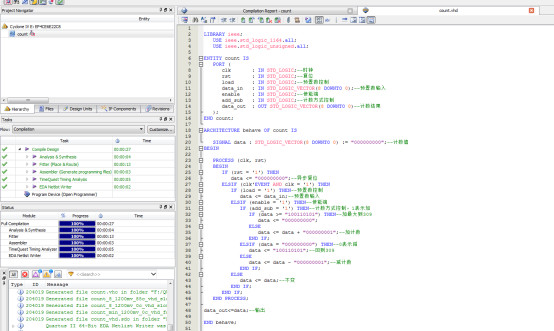

2. 程序文件

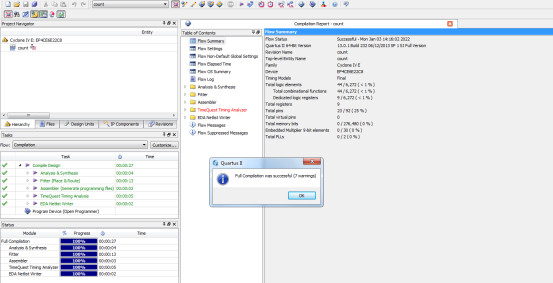

3. 程序编译

4. 仿真图

功能表

| rst | load | enable | Add_sub | 功能 |

| 1 | x | x | x | 复位 |

| 0 | 1 | x | x | 置数 |

| 0 | 0 | 1 | 1 | 加计数 |

| 0 | 0 | 1 | 0 | 减计数 |

| 0 | 0 | 0 | x | 不变 |

异步清零同步置数可逆计数器设计

1题目要求

要求设计一个异步清零同步置数可逆计数器,要求如下:

1.计数范围:0~N,N为309。

2.具有工作模式控制端:复位端、预置数控制端、计数使能端、计数方式控制端(控制递增或者递减计数),并需给出功能表。

3.设计完成后进行功能仿真,并结合功能表对仿真结果进行分析。

2电路设计

电路设计的输入端口包括时钟信号clk,异步清零复位端信号rst、同步预置数控制端load、预置数输入data_in(8 downtown 0)、计数使能端enable信号、计数方式控制端add_sub信号(高电平控制递增,低电平控制递减计数)。输出端口为data_out(8 downtown 0),表示计数的结果。

3建立项目

1)在计算机的E盘,建立文件夹count文件夹,项目名称为count,顶层设计文件名也为count。

2)启动QuartusII软件,在添加文件对话框的file name中输入count.vhd,然后单击add 按钮,添加该文件。

3)设置完成,单击finish按钮,关闭新项目建立向导。

4编辑与编译

编辑,单击file->new对话框,在Design Files下选中VHDL File选项,单击OK按钮,在文本编辑区输入以下程序:

LIBRARY ieee;

USE ieee.std_logic_1164.all;

USE ieee.std_logic_unsigned.all;

ENTITY count IS

PORT (

clk : IN STD_LOGIC;--时钟

rst : IN STD_LOGIC;--复位

load : IN STD_LOGIC;--预置数控制

data_in : IN STD_LOGIC_VECTOR(8 DOWNTO 0);--预置数输入

enable : IN STD_LOGIC;--使能端

add_sub : IN STD_LOGIC;--计数方式控制

data_out : OUT STD_LOGIC_VECTOR(8 DOWNTO 0)--计数结果

);

END count;

ARCHITECTURE behave OF count IS

SIGNAL data : STD_LOGIC_VECTOR(8 DOWNTO 0) := "000000000";--计数值

BEGIN

PROCESS (clk, rst)

BEGIN

IF (rst = '1') THEN

data <= "000000000";--异步复位

ELSIF (clk'EVENT AND clk = '1') THEN

IF (load = '1') THEN--预置数控制

data <= data_in;--预置数输入

ELSIF (enable = '1') THEN--使能端

IF (add_sub = '1') THEN--计数方式控制,1表示加

IF (data >= "100110101") THEN--加最大到309

data <= "000000000";

ELSE

data <= data + "000000001";--加计数

END IF;

ELSIF (data = "000000000") THEN--0表示减

data <= "100110101";--回到309

ELSE

5波形仿真

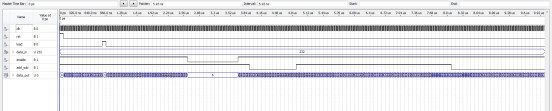

1)建立波形输入文件,设定仿真时间和周期后,将波形文件以count为名,放在文件夹E:\count文件夹下。

2)加入元件引脚,调整波形坐标间距后编辑波形,通过鼠标拖动选中要编辑的波形部分,再点击上方的波形设置按钮设置对应的波形。本次计数器波形设置最终如下图所示:

图1

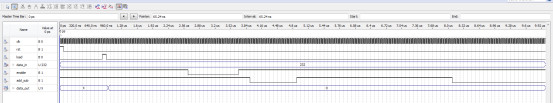

3)单击processing->start simulation 选项,启动仿真器。使用调制焦距工具调整波形坐标间距,异步清零同步置数可逆计数器仿真波形如下图所示:

图2 整体仿真图

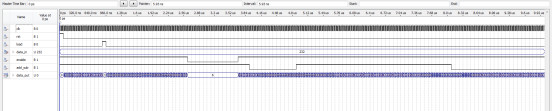

图3 局部放大仿真图

图4 局部放大仿真图

其中图2为整体仿真图,图3图4为局部放大后的仿真图。

6功能表

异步清零同步置数可逆计数器的如下表所示。

表1 功能表

| rst | load | data_in | enable | Add_sub | data_out(输出) | 功能 |

| 1 | x | xx | x | x | 0 | 复位 |

| 0 | 1 | M | x | x | M | 置数(M) |

| 0 | 0 | xx | 1 | 1 | 从M开始递增 | 加计数 |

| 0 | 0 | xx | 1 | 0 | 从M开始递减 | 减计数 |

| 0 | 0 | xx | 0 | x | 保持不变 | 不变 |

7 仿真分析

通过功能表可以看出,若rst信号为高电平,则为异步复位功能,data_out将输出0,对应仿真图3可以看到rst信号控制data_out输出低电平。若rst为低电平,则不复位,此时若load为高电平,则为置数功能,此时data_out的输出将等于data_in信号,对应可以看到上面仿真图图3,当load为高电平,输出为232,即data_in信号,因此置数功能仿真验证正确。若rst和load均为低电平,此时enable控制计数器的运行,若enable为低电平,则计数器停止计数,数据保持不变,对应仿真图图2可以看到,enable低电平时,输出保持为6不变,enable为高电平时,正常计数,因此计数使能功能仿真正确。Enable高电平时,若add_sub信号为高电平,则为递增计数,否则为递减计数。对应仿真图图4可以看到,add_sub信号为高电平时,计数值从11一直计数到18,此时add_sub信号变为低电平,计数器从18开始递减,一直减到0,然后重新回到309继续开始递减,因此计数方式控制功能仿真正确。

部分代码展示:

LIBRARY ieee; USE ieee.std_logic_1164.all; USE ieee.std_logic_unsigned.all; ENTITY count IS PORT ( clk : IN STD_LOGIC;--时钟 rst : IN STD_LOGIC;--复位 load : IN STD_LOGIC;--预置数控制 data_in : IN STD_LOGIC_VECTOR(8 DOWNTO 0);--预置数输入 enable : IN STD_LOGIC;--使能端 add_sub : IN STD_LOGIC;--计数方式控制 data_out : OUT STD_LOGIC_VECTOR(8 DOWNTO 0)--计数结果 ); END count; ARCHITECTURE behave OF count IS SIGNAL data : STD_LOGIC_VECTOR(8 DOWNTO 0) := "000000000";--计数值 BEGIN PROCESS (clk, rst) BEGIN IF (rst = '1') THEN data <= "000000000";--异步复位 ELSIF (clk'EVENT AND clk = '1') THEN IF (load = '1') THEN--预置数控制 data <= data_in;--预置数输入 ELSIF (enable = '1') THEN--使能端 IF (add_sub = '1') THEN--计数方式控制,1表示加 IF (data >= "100110101") THEN--加最大到309 data <= "000000000"; ELSE data <= data + "000000001";--加计数 END IF;

源代码

扫描文章末尾的公众号二维码

2万+

2万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?