视频1:https://www.youtube.com/watch?v=1zw1HBsjDH8&list=PLkqJVNOiuuHtNrVaNK4O1BSgczja4obeW

(What is AXI?)我名之为”为什么需要AXI?“

先看最原始的内存接口,如图

只有五个port

读写数据时,在当前周期设置 read_addr 和 write_addr, write_valid,数个周期之后,就能读到数据或者写到数据

但是这种内存接口太拉了,对硬件部件有很高的限制,如下

第一个限制的原因:内存没有接口来表述读出的数据什么时候是有效的,因此只能通过“约定”的方法来确定 read_data 数据什么时候有效

总而言之,这种内存读写接口,对内存会有很高的限制,不适用于环境多变的情况

所以,我们需要 AXI

AXI协议的优点如下:

bursts: 读写请求可以以”流“的形式发送,我们叫这个为 bursts

AXI 的接口远多于 5个 ports,我们不会很细节地去讲它,但总体上来说,AXI的接口可以分为五组

我们通常用 ”channel“ 来描述一组端口

可以看到第五个channel名为 write response

这是因为在 AXI 中,写操作是可以失败的,因此需要它

-------------------------------------------------------------------------------------------------------------------------------

视频2:https://www.youtube.com/watch?v=okiTzvihHRA&list=PLkqJVNOiuuHtNrVaNK4O1BSgczja4obeW&index=2

(What is AXI Lite?)

在 5-port 接口中,我们设想内存每周期都读数据,因为我们没有 read_enable信号

然而read_enable信号是必要的,加上read_enable,我们可以节省功耗,这样内存自己可以根据 read_enable 减少自己内部的活动

如图,加上一个 read_valid 信号,就可以在需要读数据时设置 read_valid 为1,接着一个时钟周期过后,read_data的数据就会被内存设置为我们所需的数据

由于内存并不总是准备好了内存读写(比如有其它的部件正在使用它),还需要给它加上 read_ready 和 write_ready 端口,如下图

当 read_valid 和 read_ready 都为1时,内存就会触发一个 read 操作,几个时钟周期后,我们就会读出数据

write_ready 也是同样的道理

当用户想要在不同时刻发送写地址和写数据时,该怎么办呢?

回答:给 write_addr 和 write_data 信号分别加上 valid/ready 信号

如果内存不能够在固定的时间返回读数据,该怎么办呢?

解决方案:跟write差不多

目前为止,我们已经有了四个 channel

如果内存读写会失败怎么办呢?(比如该内存区域设置成不可读,或者内存地址不合法,内存地址不对齐等等)

1. 需要内存给user发送一个回复,表明read是否成功

2. 需要内存给user发送一个回复,表明write是否成功

解决方案:

read_data_resp 用来表示 读数据是否成功

write_resp 和 其它两个信号 用来表示 写数据是否成功

resp信号通常有两位,意思如上

OKAY -> everything okay

EXOKAY -> 部分事情 Okay

SLVERR -> slave error

DECERR -> ? 自己查手册吧

我们目前的内存接口,能够适应 读写内存 的 variable time response,还有错误处理

这5个通道,就是 AXI-Lite 协议的核心

我们介绍一点 AXI4-Lite 的额外特性

特性1:Strobed Writes (选通写)

strobe 是一个 data mask,效果如图,应该很好理解

加上 write_data_strb 信号后,如图

AXI 还支持 prot filed,拥有一些访问权限信息

读写加上 prot 信号后,如图,prot 信号的值的含义如右表

如图所示,负责处理请求的模块一般被称为 Slave,负责发送请求的模块一般被称为 Master

如图是AXI4-Lite 接口的信号,一共21个端口,被分为5个组。其中有两个是 Clk 信号 和 Reset 信号,不被分组(或分为Global组)

-------------------------------------------------------------------------------------------------------------------------------

视频3:https://www.youtube.com/watch?v=ydSy7uO60Is&list=PLkqJVNOiuuHtNrVaNK4O1BSgczja4obeW&index=5 (What is AXI: Read Bursts)

什么是 Read Bursts 呢?考虑如下代码:

我们需要从一块连续的内存里,连续地读出数据

设想读出的数据位宽是 4 字节,我们将要读取的内存地址将是 0, 4, 8 , 12, ..., 36

另一种方式来表述:读10个连续的 4字节内存块,起始地址为0

对于这种内存访问的一个比较紧密的描述 ,就是burst

在一个burst里,每一个transfer都可以叫做一个 beat

在AXI中,如图的这种连续、串行的 burst 模式也叫做 incremental burst

那么,如何使用内存接口中的 read channel 去描述 incremental burst 呢?

(未完待续。。。英文真难读)

-------------------------------------------------------------------------------------------------------------------------------

视频:https://www.bilibili.com/video/BV1mD4y1p7UK/?spm_id_from=333.788&vd_source=7a1a0bc74158c6993c7355c5490fc600 (实现AXI总线自由之AXI解读-从0手敲一个AXI总线)

AXI支持非对齐数据传输,使用 byte strobe(掩码控制)

AXI-FULL: 功能齐全的AXI总线协议

AXI-LITE: 简化版AXI总线协议

AXI-STREAM: 面向数据流的 AXI总线协议

APB, AHB 比AXI简单很多,掌握了AXI,APB和AHB就都不在话下了。

AXI 并不难,上面两幅图(5个通道)基本就说明了AXI总线做的事情:

读数据:Master向Slave发送读地址,等待读数据返回

写数据:Master向Slave发送写地址和写数据,等待响应,等到valid响应说明写入成功

AXI总线是一种突发总线,突发(burst)传输。一直连续地传输,比如说突发8次传输,就是指传输数据连续的传输。

(为什么要支持突发传输?因为这种传输方式效率高、速度快)

======= 写地址通道 ========

AWLEN: 突发长度,表示连续传输几次

AWSIZE: 表示一次传输的数据的位数

AWBURST: 突发类型。分为FIXED(固定内存地址), INCR(自增),WRAP

AWLOCK: AXI4并不支持锁事务 -- 不会用到,skip

AWPORT: unprivileged/privileged access, secure/nonsecure access, data/instruction access

AWQOS:quality of service(服务质量). -- 一般不会用到,skip

AWREGION: 一般不会用到,skip

AWUSER: 用户自定义信号

AWVALID: 有效信号,表示当前传输的信号是有效的(握手信号)

AWREADY: 准备信号,表示当前模块准备好接收信号(握手信号)

当有效信号和准备信号同时有效时,就会传输信号,称为 Fire

======= 写数据通道 ========

WDATA: 写数据

WSTRB: 掩码信号

WLAST: 写数据结束信号

======= 写响应通道 ========

。

。

。

波形解读:

1. VALID和READT同时为高,表示当前数据有效

2. 先写地址,紧接着写数据,最后一个数据跟随LAST

3. 先读地址,紧接着读数据,最后一个数据跟随LAST

4. 写完数据,有一个响应信号

-------------------------------------------------------------------------------------------------------------------------------

视频:https://www.bilibili.com/video/BV1tv4y1y7VX/?spm_id_from=333.337.search-card.all.click&vd_source=7a1a0bc74158c6993c7355c5490fc600 (从0手敲AXI总线接口)

NOTES:

突发传输长度有限制,根据协议,只能是 1, 2, 4, 8 ... 256

AXI 写实现的步骤:

1. 写首地址

2. 紧接着写首地址,突发传输数据

3. 控制LAST信号

4. LAST脉冲之后,等待一个响应信号

AXI 读实现的步骤:

1. 写首地址

2. 紧接着等待从机传输过来的数据,当有效信号和准备信号同时为高时,读取数据

3. 接收LAST信号

(目前在看从0手敲)

-------------------------------------------------------------------------------------------------------------------------------

接下来阅读《深入AXI4总线(一) 握手机制》 https://zhuanlan.zhihu.com/p/44766356

VALID/READY 握手机制

AXI 总线共有 5 个独立的通道,分别为写地址、写数据、写回应、读地址、读数据通道。5 条通道相互独立,有一些细小的差别,但共同使用一套握手机制:VALID/READY 机制,来实现信息的传递。

VALID/READY 机制这个赛高啊,这个好啊,ARM 的手册上这么夸:

作为一种双向流控机制,VALID/READY 机制可以使发送接收双方都有能力控制传输速率。

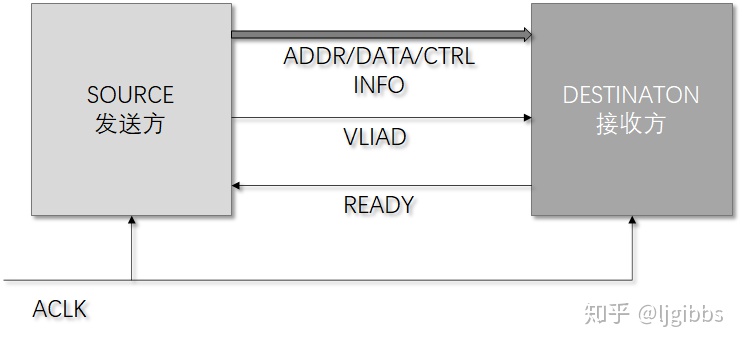

在握手机制中,通信双方分别扮演发送方(Source)和接收方(Destination),两者的操作(技能)并不相同。

发送方置高 VALID 信号表示发送方已经将数据,地址或者控制信息已经就绪,并保持于消息总线上。(发送方是valid,接收方是ready)

接收方置高 READY 信号表示接收方已经做好接收的准备。

当双方的 VALID/READY 信号同时为高,在时钟 ACLK 上升沿,完成一次数据传输。所有数据传输完毕后,双方同时置低自己的信号。

所谓的双向流控机制,指的是发送方通过置起 VALID 信号控制发送的时机与速度,接收方也可以通过 READY 信号的置起与否控制接收速度。(速率控制机制)

发送方拥有传输的主动权,但接收方在不具备接收能力时,也能够置低信号停止传输,反压发送方。

VALID/READY 的三种情况

VALID/READY 信号按照到达的先后顺序可以分为 3 种情况:

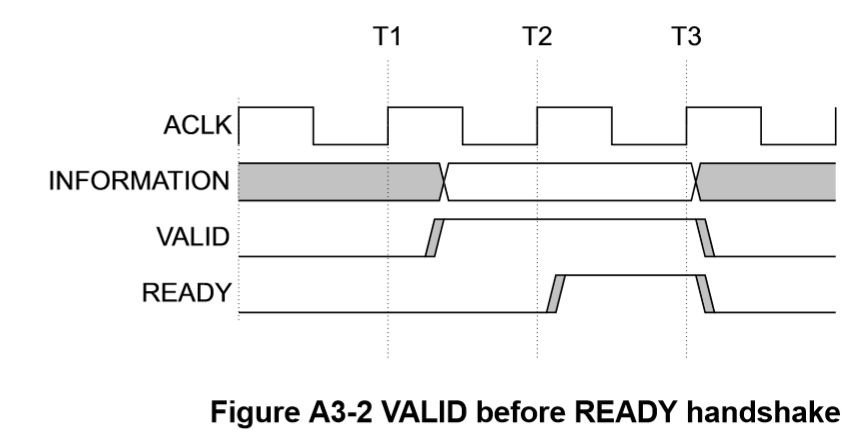

1.VALID 信号先到达

发送方 VALID 信号早早就到了,这时还不到 T2 时刻,并带来了新鲜的数据(数据通道),地址或者控制信息(地址通道),总之是信息(Information)。

但过了 T2 也没见到接收方的 READY 信号。原来是接收方还忙着,可能上一次的数据还没存完,还堵在数据通路上,忙过了 T2 才来。

好吧,那也行,T3 时刻传输完成。

在这种情况下,接收方通过 READY 信号控制了传输速度,反压了发送速度。

协议规定在这种情况下,VALID 信号一旦置起就不能置低,直到完成握手(handshake occurs),至少传输一周期数据。

在设计接收方逻辑时,检测到 VALID 信号置起,如果系统正忙,完全可以让发送方等待,发送方在完成传输之前都不会置低 VALID 信号,不需要考虑发送方撤销传输的可能。

协议另外规定:发送方不能通过等待接收方 READY 信号来确定置起 VALID 信号的时机

这句中文阅读理解有点难,原文为:

A source is not permitted to wait until READY is asserted before asserting VALID.

笔者个人理解,READY 信号可能先到达,如下图的情况。但是设计发送方逻辑时,不能将 READY 信号作为置高 VALID 逻辑的条件,比如将 READY 信号通过组合逻辑生成 VALID 信号。

换句话说,发送方准备发送,置起 VALID 信号是完全主动与独立的过程。接收方 READY 信号按照协议可以依赖发送方 VALID 信号,但如果此时发送方也依赖接收方信号,就会造成死锁的情况,所以协议在这里强调了 VALID 信号的主动性。

module axi_src

...

//assign VALID = SRC_CONDITION && READY;//NOT permitted and may cause deadlock

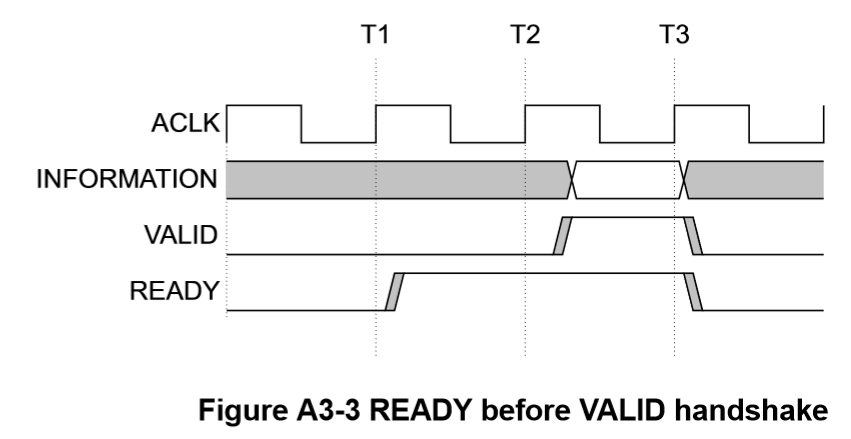

assign VALID = SRC_CONDITION;//permitted ... endmodule module axi_dst ... assign READY = CONDITION && VALID;//permitted ... endmodule 2.READY 信号先到达

READY 信号很自由,可以等待 VALID 信号到来再做响应,但也完全可以在 VALID 信号到来前就置高,表示接收端已经做好准备了。

而且,READY 信号与 VALID 不同,接收方可以置起 READY 之后发现:其实我好像还挺忙,然后置低 READY 信号。只要此时 VALID 信号没有置起,这种操作是完全可以。

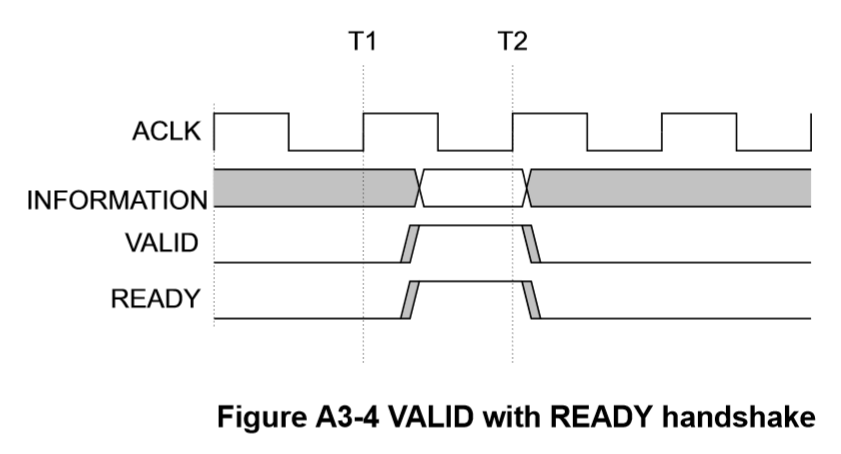

3.同时到达

同时到达就很简单,等到下一个时钟上升沿 T2,传输就这么轻松愉快地在一个时钟周期里完成了。

实现细节

本文的最后讨论一个协议的实现细节。如果读者仅仅想了解 AXI 协议的使用,那么每篇文章的实现细节章节可以跳过。这个章节面向有实现 AXI 协议需求的读者。

前文我们讨论过, READY 信号原则上由接收方自身的接收状况以及 VALID 信号控制。(或者仅由接收方自身的接收状况决定)协议中没有规定 READY 信号的默认状态,即未进行传输时的电平状态(default value)。

协议建议 AW/AR READY 信号(这里 AW/AR 指的是读写地址通道的 READY 信号,将在第二章中正式引入)的默认电平为高电平。若默认电平为低,则每次传输至少需要 2 个周期才能完成,第一个周期置高 VALID 信号,第二个周期从机才会置高 READY 信号。相当于每次传输增加 1 个周期时间开销,这在某些情况下会对传输效率有较大的影响。

结语

好了,今天的文章就到这里了,就像本文开头说的 : 一点儿也不深入。

文章讨论了 AXI 总线的基本特征:VALID/READY 握手机制,并了解到握手的三种情况以及一些协议的规定。

接下来我们会具体到 5 个通道讨论握手问题,并且进一步了解这 5 个通道。

这似乎可以分成两篇文章水。。啊不,分成两篇文章可能结构更加清晰。

传送门在这里:

-------------------------------------------------------------------------------------------------------------------------------

接下来看 唐浩晋 的分享视频,请看这个笔记 https://www.cnblogs.com/yinhuachen/p/17163329.html

5875

5875

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?