写在前面: 我的微信公众号: xiaoshi_IC,小石谈IC,近期已完成了PCB系列,后续后续会逐步完成 IC版图,FPGA设计,信号完整性,IC设计,通信原理系列,做开源的微电子,电子公众分享,坚持做有价值的分享,欢迎持久关注。该公众号内容同步分享 csdn,B站,知乎,youtube等,用户搜索相关的文章标题,即可很方便找到,同步更新。

使用allegro设计pcb板卡上,有时阻抗的设计,要求同一层的不同线宽都要求匹配到50欧姆,这个怎么设计?如 top层有20mil线宽的射频走线,有5mil宽的其他走线,都要求匹配到50欧姆,这样,需要进行隔层参考,如下图阻抗所示。L1层(top层)18mil线宽阻抗,参考L3层,匹配到50欧姆。 L1层(top层)6.3mil线宽阻抗,参考L2层(GND层),匹配到50欧姆。 细心读者发现,L3是信号层,没有GND怎么办? 那么,需要在第三层加一部分GND,后续讲详细的操作。

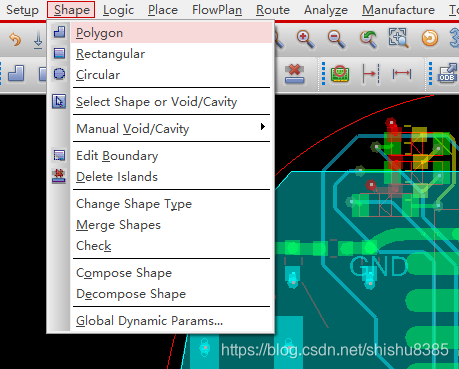

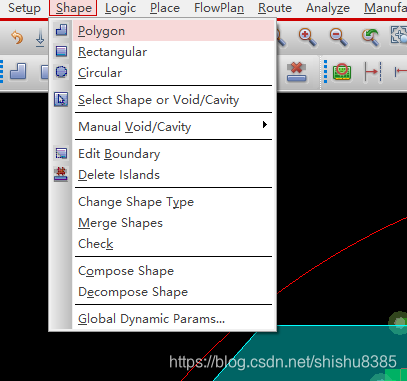

添加shape,铜皮,

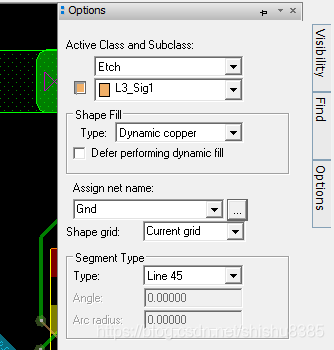

选择 etch-- L3 ,动态铜皮,网络属性 GND

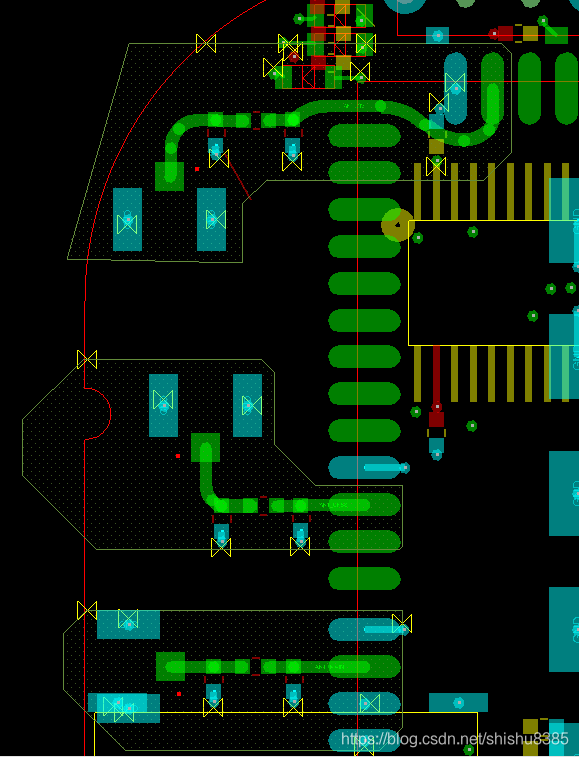

铺好的样子如下:

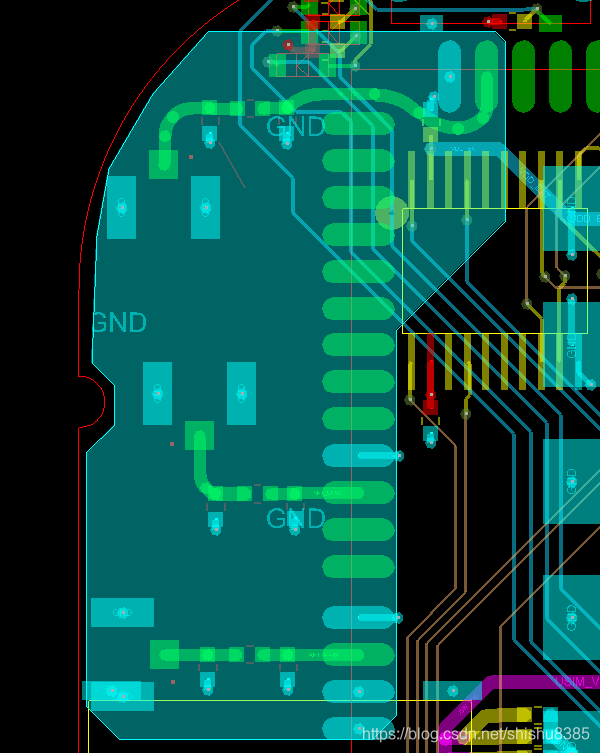

同样的,需要在L2_gnd 将相应位置挖空,这样,才能参考第三层,下面,添加 routekeepout 区域,即禁布区:

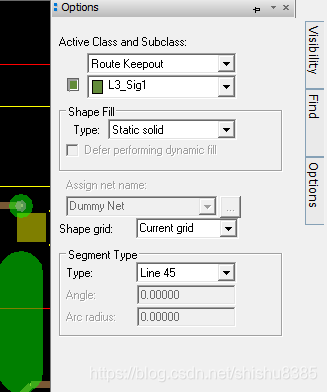

option菜单栏设置如下:

画完后的区域如下:

整体上和L3对比看,上面说错了,是画在L2层

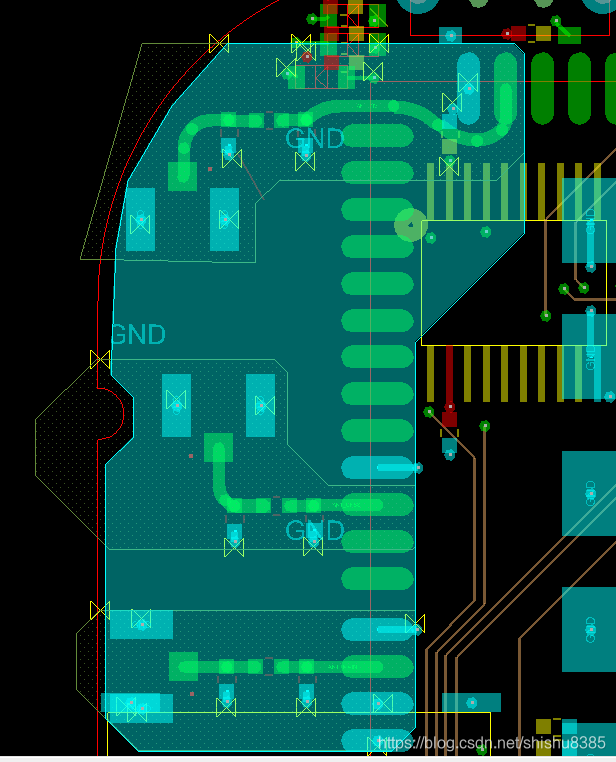

第二层版图:

联合第三层版图,可以看出,做到了 隔层参考

下面讲一下,过孔的复制操作,这种操作一般应用在,射频走线的周围或者孤立的GND和其他GND之间互联,因为上文我们做了隔层参考,这样,既有射频线,也有第三层孤立的GND,因此打GND孔,可以让射频线有低阻抗回流,以及让第三层孤立的GND和其他层GND有更好的连接。

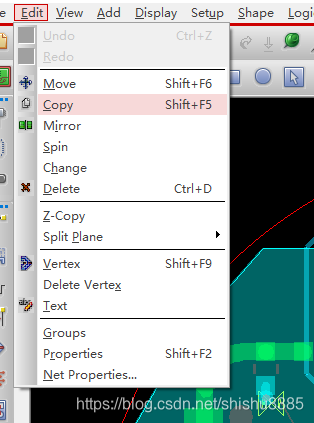

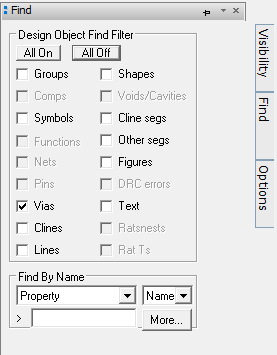

选择 edit – copy后,在 右边 find 中选择 via

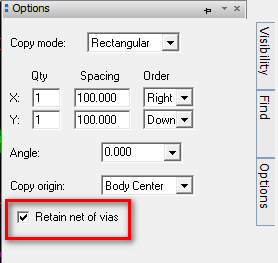

然后,继续在右边菜单 option 中,把 retain net of vias勾上,表示要复制这个过孔的原来的属性,这些都操作完了以后,然后鼠标左键,在pcb上单击一个已经存在的GND VIA过孔,这时候,鼠标左键就成功复制了一个过孔,然后用左键依次放在所需要的地方即可。

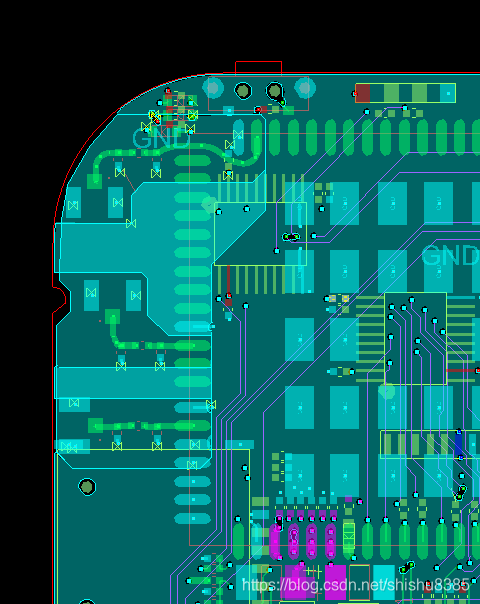

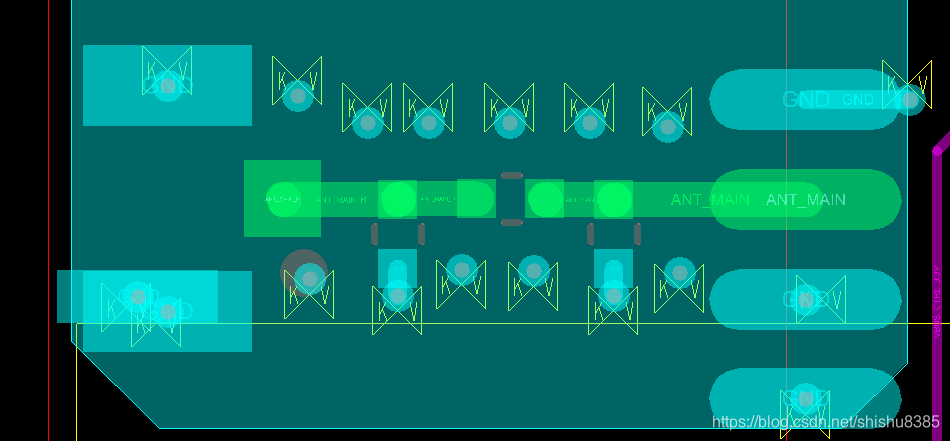

完成后效果如图:drc可以忽略。

完毕。

我的微信公众号: xiaoshi_IC,小石谈IC,近期已完成了PCB系列,后续后续会逐步完成 IC版图,FPGA设计,信号完整性,IC设计,通信原理系列,做开源的微电子,电子公众分享,坚持做有价值的分享,欢迎持久关注。该公众号内容同步分享 csdn,B站,知乎,youtube等,用户搜索相关的文章标题,即可很方便找到,同步更新。

7037

7037

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?