本章节对scan进行一个比较简要的介绍。

1. DFT测试的概念

1.1 为什么要做测试?

当芯片的设计完成之后,进行Tape out给到foundry,就需要进行芯片的制造了。虽然工艺制造已经如此先进和精确,但是芯片的良率依然无法提升到100%,这就意味着芯片制造过程中总会出现一些缺陷。这些缺陷会导致比如金属线的短路,比如金属线的短路等等都可能导致芯片的功能失效。因此在芯片制造完成之后,并不是直接进行产品使用,二十需要进行测试,从而筛选掉一些废片。这其实就是DFT的作用了。在design阶段,就把相关的逻辑做到设计中,当芯片制造完成之后,直接用DFT相关的逻辑进行测试从而判断工艺制造过程中是否产生了问题。

1.2 怎么样进行的测试?

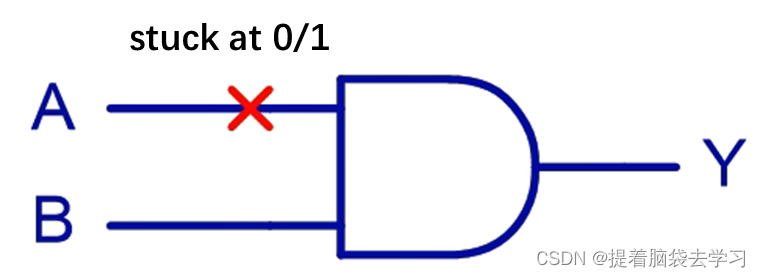

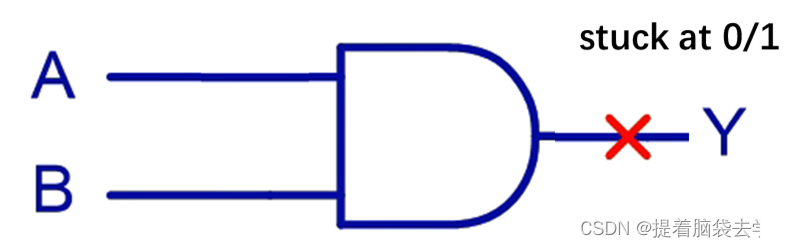

上面提到的,缺陷可能会造成短路、断路问题,这种问题体现在功能电路上就是比如某个cell的输入或者输出端口固定成了0或者1,又或者某两条电路之间直连了等等。如下图所示电路为DFT逻辑电路,用于确认工艺制造过程中的缺陷的确认。我们可以有目的的在端口处设置相应的0/1这样的数字,然后通过CLK在Y处进行测试。这就是所谓的测试向量(pattern)。因为test是有预先的测试向量输入的,然后再进行结果输出的对比,所以说只是对工艺制造过程中造成的电路的问题的测试,而对实际的功能设计不会进行测试。

1.3测试分多少阶段

WAT:其实在芯片制造过程中会进行一个WAT (wafer access test)测试,这个就是工艺厂商自己进行的一个芯片良率的测试,对制造过程中的某些电压、电流项进行测试,从而及时对工艺流程进行一个监测和改进。这个方案一般都是由工艺厂商自行进行测试的。

CP:芯片刚刚制造完成之后,会进行一个chip probing 测试,通过制定一些test probe来对刚制造完成的芯片进行测试。改测试一方面就是DFT的测试,用于检测在制造过程中是否产生了缺陷。另一方面也会进行一些performance的测试。

FT:当CP测试完成之后,对于通过DFT测试的芯片会进行封装,在封装完成之后会进行一个FT(final test)的测试。该测试其实就是最后一步的测试,用于检测封装过程中造成的问题。对于FT测试也无问题的骗子,就可以开始进行产品调试了。

2. Faults Model

上面有提到,通过输入,测试输出来判断芯片制造后是否有缺陷。那如何去评估缺陷类型,如何去评估缺陷,这个是时候就需要fault model提供一个机制用于缺陷的测试。测试向量中,会对design的输入灌入一系列的激励,然后在design的输出观察期待的结果。在芯片制造之前会进行仿真的测试。在芯片制造完成之后在进行激励的灌入,然后和期望的观察值进行对比,如果有偏差就说明出现了缺陷。

2.1 Stuck-at Fault (固定型故障模型)

stuck at是最common的fault module ,对于比较小的,频率比较低的芯片设计,比如比较小的简单的pmic设计,用stuck at的fault model就可以进行cover。这中fault 模型,在所有的DFT测试中是必不可缺的。

如上图所示,表示的是一个AND门的一个输入A端口,被stuck为了0/1.加入stuck at为了0,那么无论B为0还是1,Y的输出都是0,这样其实就可以判断Y端口的输出可能不受A端口的影响,A端口可能就是stuck住了。同理,如果Y被stuck为了0/1,那么A/B无论什么输入,Y的值可能也是固定不变的。所以通过Y处的值的测试,可以判断出来这个AND门的三个端口有一处是有问题的。通过debug就可以进一步确认问题。这就是简单的stuck at 模型的介绍。

2.2 At-speed Fault model

2.2.1 transition

即在电路真实工作过程中数据流穿过实际的门出现问题。入下图所示,A端口到Y端口低到高的trans或者B端口到Y端口的trans的问题,都可能导致这个门失效。那这个trans有问题,和工艺制造有什么问题呢?比如制作过程中可能没有出现短路短路的情况,但是可能掺杂工艺的影响导致载流子掺杂浓度不够高,那么trans可能就很慢,就会导致最终的Y值和期待的不一样。在工业级别的芯片设计中,这个trans faults基本都是需要DFT中测试的。

一般在设计中是通过插入OCC 电路,然后通过occ产生Launch & Capture脉冲,用这个来测试实际工作频率时的slow-to-rise node & slow-to-fall node,从而判断是否有trans的问题。这个和stuck at的最大区别其实就是测试频率的不同。stuck at可能就是在26M的低频下进行的测测试,但是trans是在真是的工作频率下,比如100M下进行测试。

这也是为什么在低频的设计中可能只需要stuck,因为trans在26M一下测试,其实和stuck一样的效果了。

2.2.2 path delay

最大延时路径测试。相比较于transition fault测试,增加了新的at speed 测试内容,从而corver更多的测试内容。比如一些critical path ,在正常的trans测试过程中,可能只是对我们dft穿好的chain进行的一些测试,对dft穿chain之后的逻辑path进行的测试,对于我们func功能下的一些critical path可能corver不了,但是这些path又相当重要,因此会又一个path delay的at speed测试,相更关注critical timing path,生成相应的delay test pattern。这个一般在STA后或者TO后,给DFT提供相应的timing 报告,DFT同事根据报告生成path delay pattern。

2.3 Bridge Fault

桥连故障模型如下所示,可能某两条net之间因为工艺的原因导致之间存在侨联,这种侨联显然会对功能产生影响。但是因为stuck at和trans并不能把所有的问题完完全全给corver,也只是随机产生的pattern。每一个fault都会通过不同的控制和观测对fault进行多次的观测。而atpg对于stuck和trans是含有随机性的。因此这种桥连问题,会随着测试观测此说的增加而增加被测到的机会。不过呢,这种问题对于芯片要求非常高的情况下才会使用到。

2.4 IDDQ Fault

静态电流fault模型。如下图所示,当A为0,B为0、1时候对应Y为1、0.这才是正常的情况,但是如果因为N1管子的问题漏电问题,导致B为0的时候,N1的管子反而打开了,那么Y值就是0。这种就是IDDQ fault。通过测试不工作时候的漏电流情况,来检测fault的情况。但是这种fault对于现在很先进的工艺来说比较难搞,因为随着工艺先进,lekage也越来越大了,就不好判断了。这种是通过状态表测试静态电流的方式来判断,很花费时间,能够corver80%-90%的fault。

2.5 UDFM(User-Defined Fault models)

从名字上可以看出来,是用户定义的错误模型。对于一些特殊测试项目,可能trans、stuck不能自动 corver,用户通过自己定义测试模型,来增加测试的corver程度。这种也很少遇到,不展开讨论。

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?