POCV (parametric on chip variation)##

本小节介绍pocv相关内容

1. Overview

Process variation可以简单分成die-to-die和on chip variation(ocv),die-to-die的可以通过signoff过程中不同的check view去cover,on chip variation需要通过signoff过程中设置不同的derate值去模拟悲观化相关cell。

OCV:通过在timing path上设置统一的early/late derate做hold和setup的check,这样的设置方式很简单,但同时很粗暴,会导致大部分cell的delay过于悲观,而小部分的可能又过于乐观。

AOCV:不再是在path上设置统一的值,而是通过path depth获取随机variation,distance获取on-die variation的方式进行设置。这种设置相对于ocv更加精确。但是对于gba mode来说,path depth造成的variation的获取还是过于悲观,用pba又会耗费大量的run time。且variation的获取不受trans和load的影响。

POCV:随着随机variation相对于chip variation的占比增大,pocv的出现,能够更好的meet实际的工艺需求。相对于aocv ,大大减小的pba和gba之间的悲观性的差距。能大大减小eco的effort。Pocv对于cell的variation不再是path depth相关的,而是基于统计学搞出来的。每一个cell,都会通过仿真得到相关的高斯分布,那么每一个cell都会拥有相应的mean值和sensit值,在update

timing时候,不再是统计depth计算,大大节省时间。另外POCV也支持aocv中关于chip variation的模型,可以通过distance来进行derate设定。

2. Pocv analysis

Pocv关于cell的random variation到底怎么搞到的?这边简单叙述一下:

如下图上部分,一个cell最大最小值可能限定在一个范围内,那芯片工艺制造之后,它的cell delay落到最大最小值内的概率为1。那通过一系列的spice仿真,发现cell的delay的概率分布非常靠近一个高斯分布,如下图下部分所示。

这是一个概率密度分布函数,对于高斯分布,当我们的delay取值为u+3σ时候对应的概率值为0.9973,因此我们对于cell delay分布类似于高斯分布的variation,一般都设置3σ的方式进行cover。这也是我们POCV的cell delay计算方式:

Delay= Delaymean+3σ,

其中Delaymean其为delay的均值,由lib中的trans/load决定。σ的来源有两种方式,一种是设置single coefficient,σ等于Delaymean * single coefficient;

另外一种是吃相关的LVF文件,里面也是类似于查找表的形式,σ取决于trans和load。

3. Pocv Flow

Pocv 的flow包含以下主要步骤:读入std库,读入pr后的netlist,读入相关的约束文件。然后读入pocv side file(如果是用的lvf格式的lib,那么就不需要这个了)然后读入spef,如果需要设定distance-based的derate那么需要带上坐标信息从而方便计算距离。数据读入后是能pocv的分析然后update timing就可以查看相关的报告了

set_app_var timing_pocvm_enable_analysis true

set_app_var timing_pocvm_corner_sigma 3

read_ocvm pocv_coefficient_file_name

read_ocvm pocv_distance_based_derating_file_name

3.1 Guard-banding in POCV

Guard-banding这个说白了也是一个类似于derate值的东西,但是它和process是无关的。比如我们针对超低电压,或者考虑了ir drop等问题,想而外在已经存在的derate基础上在设置一些悲观度,就可以用这个。

set_timing_derate –cell_delay -pocvm_guardband -early 0.95

set_timing_derate –cell_delay -pocvm_guardband -late 1.05

其对应的计算在如下图所示,这个变量在mean值和sigma值中都会用到

4. Pocv report

report_ocvm -type pocvm –cell_delay –list_not_annotated –coefficient

report_ocvm -type pocvm [get_cells I]

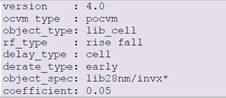

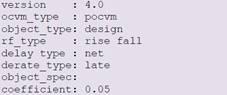

会把用pocv coefficient的cell给表示出来,如果有设置distance derate,也会描述出来,如下图所示没有distance derate

report_timing -derate

这种会在timing 报告中把derate相关的设定个报出来,还会报出mean、sensit、incr、path,其中incr和path不再解释,mean和sensit可以理解为累计的高斯分布函数变量,可以满足incr=mean+/-3*sensit

report_timing -variation

会打出更加详细的pocv相关的高斯变量的报告如下所示,其中Incr对应的mean、sensit、corner对应的为单一cell相应的高斯分布变量,满足corner=mean+/-3sensit,而Path中的相关值为累计高斯分布变量,首先依然满足Value=Mean+/-3sensit,而Path中的Mean等于Path中的前一级Mean加上Incr中的本级别的mean,而Path中的Sensit等于Path中上一级的Sensit的平方值加或减Incr中的sensit的平方值,再开平方。其实某一级别的delay值,在考虑了高斯分布后,就等于本级别Path(Mean,Sensit) + 本级Incr(Mean,Sensit)

report_delay_calculation -from I/I -to I/ZN -derate

可以报告出该cell上到底有设置什么样的derate。如下图所示可以看出来,cell delay derated的计算方式以及sigma的计算方式,而我们上面报告中所示的Incr的Mean值就是cell delay derated的值。而在报告中显示的derate值,也会相应的在如下的计算中体现出来

3902

3902

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?