近些年来随着人工智能和大数据应用的发展,基于大数据的挖掘和处理的计算资源和能力对于容纳庞大的数据处理能力非常重要。对于半导体技术而言,随着工艺制程的演进,晶体管栅极channel沟道逐渐变小,然而电源电压也在逐渐变低,在决定芯片性能下电源网络一个稳定性好的电压是非常重要的。

在高频高速应用中,需要支持更大的带宽,为了支持多核CPU、GPU、NPU的性能需求,就需要对芯片的电源PI性能进行特别设计。如下图是一些HPC应用。

电源完整性而言,在运行某些复杂的场景下产生快速的电流波动而电源无法快速响应将产生电压drop,这个电压drop跟电源网络无源特性有关,往往是寄生电感和电容产生一个固定的谐振频率。因此为了维持芯片一个稳定的电源电压,对于HPC应用,设计稳定的全链路PDN极具挑战的,特别地,在HPC和网络类芯片往往电流需求高达数十安培,在这类芯片中PI的设计方法显得更重要了。

在实际芯片设计过程中,不太可能插入片上MOS电容来优化重载下产生的power nosie,为了克服PI问题,MIM(metal-insulator-metal)电容是一个不错的候选对象,MIM电容由一层薄的isulator和两层metal组成。插入的MIM层需要通过考虑MIM插入效率来决定,因为MIM电容器形状和MIM过孔数量受到设计规则的限制,这些规则与现有的极其密集的电源过孔和金属栅格有关。在某些cases下,可能发生需要移除一些电源孔和调整电源带的间距,这些改动可以影响到statick IR drop、Dynamic voltage drop、electro-migration等指标。因此,芯片中插入MIM电容的方式结构都是需要重点考虑的。

一般来说,电容的使用是一种通用的解决方案,以减轻PDN设计时电源完整性的压力,也是利用去耦电容来降低功率噪声的设计方法防止电流波动引起的电源不稳定。具体来说,当去耦电容器的位置足够接近对应的cells时,就可以减少因为电流波动带来的电源噪声。在封装和板中均采用去耦电容作为系统级解决方案,其中在封装中的实现方式又分为embedded type、land side、die side,以提高电源完整性中、低频范围性能,在板中使用bulk电容以降低更低频的开关噪声。

为了提供快速的高频响应,片上电容可用于目标晶体管、相邻的晶体管和互连的金属寄生体快速提供电荷,响应电流的高频波动。然而,片上decap cell不能无限制的添加,主要的影响时对整个芯片的die size是一个挑战,因此在硅芯片的后端 (BEOL)设计中,作为片上电容和嵌入封装decap之间的提供电荷输送的角色 ,需要一种新的去耦电容的解决方案。

MIM去耦电容结构

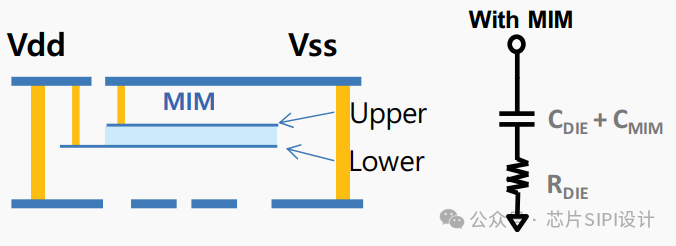

MIM电容的结构是由一层insulator和其上下两层metal组成,如下图示意,电源孔连接着上下两层metal层,设计设计时需要考虑一些spacing rules,这些rules可能会影响到电源孔的数量以及电源孔与MIM孔的spacing。

3万+

3万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?