时钟数据恢复技术

在串行通信系统中,为了保证数据的准确性,我们需要在接收端电路中设计一个时钟数据恢复电路,以便能够将时钟信号恢复到与原始时钟信号完全一致的状态,从而为后续的数字模块提供支持。通过高速传输信道的信号会发生抖动,如何将在各种非理想因素的干扰下的抖动信号进行还原,并且提取出相匹配的时钟信号需要要解决的关键问题。

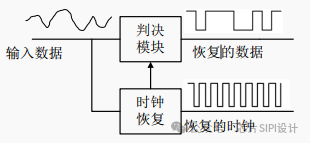

如图所示CDR电路包括时钟恢复(Clock Recovery,CR)电路和数据恢复(Data Recovery,DR)电路两部分,而数据恢复又可以细分为时钟数据相位调整(Phase Alignment,PA)电路和数据采样判决电路。时钟数据恢复电路的性能可以通过输出的时钟信号以及数据信号的抖动性能。眼图也可以很直观的看出信号的好坏,此外相位噪声、信号抖动和数据误码率也是衡量时钟恢复电路的关键指标。

基于PLL的CDR环路

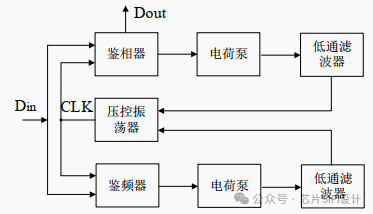

PLL结构的CDR由锁相环组成鉴相器会对输入数据与输入时钟信号的相位差进行检测,电荷泵会将电压信号转换成电流信号然后交给低通滤波器处理,在滤除高频分量后会生成控制电压来对VCO的输出频率和相位进行调节,由此还原出和数据匹配的时钟信号。PLL型CDR的稳定性更强、锁定频率更宽泛、而且具有较小的抖动。依据是否需要外部参考,将其分成带时钟参考和不带时钟参考两种类型。

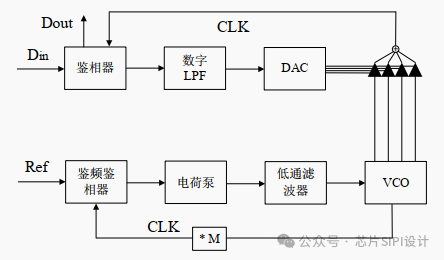

通过PLL从输入数据中恢复出时钟信号,在恢复并行数据的同时也实现了时钟的恢复,节省了系统的本地参考时钟,但这种技术需要高精度的时钟信号。下图展示了一种没有参考信号的CDR架构,它的两个环路相对独立,拥有较高的安全性,而且设置上也更为灵活,可以有效地减少锁频环的带宽,从而更快地锁住环路;同时,也可以有效地增大锁相环的宽度,以提升系统的精度。两个环路的协同工作,可以大大提高闭锁的速度,同时也能确保系统的精度。

其中,频率检测循环采用鉴频器(Frequency Detector,FD)进行频率锁定,而相位检测环路则采用鉴相器(Phase Detector,PD)进行相位锁定。此外,FD系统还可以将输入数据Din与压控振荡器(Voltage Controlled Oscillator,VCO)输出的时钟信号相位进行对比,从而节省了外部参考信号的引入。当CDR开启或锁相环锁定时,FD会被触发,通过电荷泵和低通滤波器(Low Pass Filter,LPF)升成控制电压,将VCO振荡频率调节到与进入数据速率相匹配的频段。如果频率差超出了相位检测回路的检测范围,PD输出将会对VCO进行控制,来进行更加精细的调节。

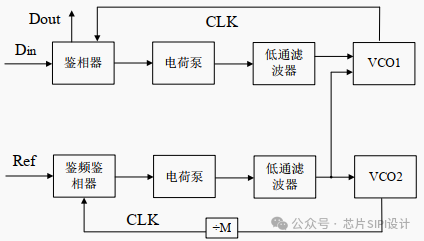

在FD将频率控制转移到PD的进程中,频率检测环和相位检测环可能会发生相互干扰,从而导致无法准确锁定相位,甚至在VCO控制信号上产生纹波。此外,假如输入数据由随机连续的同一电平组成,或是接收信号的上升沿和下降沿在传输过程中收到外界或内部噪声的干涉,FD可能会突发失效,从而影响系统的运行。这样的问题是由于频率检测环路的环路带宽通常要比相位检测环路小得多。为了配置好锁频环和锁相环的带宽,可以对电路进行改进,在每个环路中添加独立的的电荷泵和独立的低通滤波器。锁频环和锁相环可以有效地调节VCO,但是由于它们需要安装两个低通滤波器和两个电荷泵,这会导致芯片的整体尺寸变大。下图是具有外部参考时钟输入的基于PLL的CDR,它使用了类似锁相环和锁频环的方案。通过配备鉴频鉴相器(Phase Frequency Detector,PFD),频率检测环路可以将VCO2的输出时钟的相位锁定到外部引入的参考时钟Ref输出相位,并且通过分频器将时钟分割成更低的频段,从而使得VCO2的震荡频率更近似或相当于进入信息的速度,从而实现对频谱的有效控制。VCO1通过频率检测环路获得了一个粗略的控制信号,然后PD的相位检测环路将其输出的时钟相位精确地与输入数据匹配,从而提供更加精确的控制信号。而且相位检测环路的增益必须相对于频率检测环路的增益较低。

双环CDR体系结构存在两个需要考虑的问题:首先,任何一方的不匹配都可能导致振荡频率的变化,即使两个VCO共享相同的粗调输入。其次,在异步工作模式下,由于数据传输速率的限制,接收机的本地时钟频率可能会出现偏移,从而导致双环VCO2体系结构中的频率偏移问题。频率拉扯现象可能会导致VCO1与接收到的数据速率之间存在差距,这也是一个普遍存在的问题,因为它会导致版图设计中需要大量的空间,尤其是在使用基于LCVCO的锁相环时。在PLLCDR中,采用独立的VCO2时钟可以有效地提高环路的稳定性和带宽,而且,通过提供粗调信号,可以显著缩短频率检测和相位检测之间的切换时间。

基于DLL的CDR环路

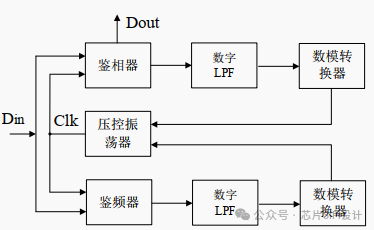

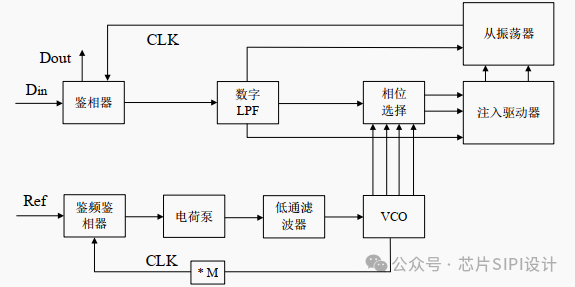

用数字逻辑取代电荷泵和LPF的CDR体系结构可以最小化所需的布局面积,并在一定程度上简化闭环稳定性分析。如下图所示,以数字LPF的形式实现电荷泵和LPF,但在频率和相位跟踪环中都加入了数模转换器(Digital Analog Converter,DAC)。这个CDR架构类似于双环PLL型CDR的架构。使用数字LPF的另一个显著优势是电荷泵和LPF在编程上可以更加方便。这种CDR设计有两个重要的问题。首先,数字LPF和DAC可能会导致较长的环路延迟,从而影响相位和频率检测的性能,尤其是在SSC操作模式下,这会使CDR的振荡容限受到影响。再次,由于DAC的清晰度有限,在同一频数步长之间可能会出现额外的抖动。这两个DAC可以通过设计具有数字开关的VCO来微调VCO频率来消除抖动。全数字CDR产生的抖动主要来自于数字控制振荡器,可以通过改进DCO来降低抖动。然而,长循环延迟和有限分辨率的问题仍然存在。

基于相位插值的CDR环路

下图中所示的基于相位插值器(Phase Interpolator,PI)的CDR架构的拓扑结构和操作机制与基于DLL的CDR设计相似。然而,在该结构中,电荷泵和LPF被一个数字LPF和一个数模转换器代替,DAC通过调节电压来控制时钟相位,这种方式比传统的锁相环和PI拓扑更加稳定,更快地采集数据,而且不会出现抖动峰值。

在PI的CDR工程设计中,当环路延时不明显超过PI的相位更新周期性时,抖动峰值就会出现。这是因为当相移控制信号到达PI时,相位已经发生了快速变化,导致方向发生了反转。而在PLL和DLL的工程设计中,它们的主要区别在于,PLL的工程设计允许发射器和接收器之间存在一定的频率偏移,从而使得CDR的性能得到了提升,从而大大提高了系统的可信度和稳定性。在多种数据速率范围内,基于相位插值的CDR的产品设计应当充分考虑到DAC分辨率、PI相移线性以及环路延时等因素,以确保其抖动性能达到最佳水平。

采用相位插值的CDR系统有着明显的优点,其中一项特点就是它的相位选择系统,这使其可以平稳地工作,而且还可以在短暂的时限内锁定。另外,它也拥有很广的运行频率范围。但是,由于VCO所产生的时钟相位都是离散的,它可能会产生很大的周期性震荡。所以,在保证频率相同的情况下,尽量多的产生不同相位的时钟,是很富有挑战性的。

基于注入锁定的CDR环路

下图中所示为注入锁定(Injection Lock,IL)拓扑结构是相位插值器的一种改进版本,比基于PLL的更为稳定,采集时间更短,而且没有抖动峰值,这些优点使得它成为一种比较理想的解决方案。PLL以环路带宽的速率清除振荡器中累积的噪声,而注入锁定振荡器对应的速率可以与参考源频率一致,这意味着注入锁定振荡器的等效环路滤波带宽为fref/2,远大于使用相同参考源的PLL。在这里中的相位选相器可以通过DAC和PI的操作来完成在这里的功能,而震荡器则可以通过锁定频率和相位来完成这一功能。

震荡器还可以作为一个低通滤波器,有效地抑制相位选择产生的占空比失真。对比于基于相位插值器的CDR设计,这种方法可以更为平稳地恢复时钟相位。在满足特定的注入锁定要求的情况下,两组时刻需要维持180度的相位关系,以保证它们能够被有效地注入到差分振荡器。在注入驱动激活阶段,对于保证振荡器中的时刻相位分离,可调电流增益需要减小,这样可以有效地提高占空比平衡恢复时刻的精度,并且可以有效地抑制相位跟踪抖动的产生。相较传统的采用相位插值的CDR系统设计,这种新型的产品设计更为优越。尽管这些改进可以扩大振荡器的闭锁范围,但仍需要仔细产品设计和布局注入驱动器和从振荡器,以保证它们能够有效地避免任何来自外部的干扰。

基于过采样的CDR环路

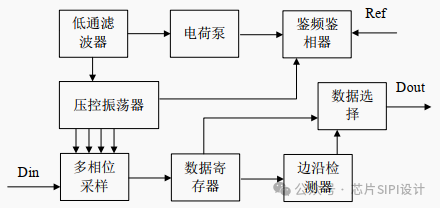

过采样技术使信号传输功率不发生变化,让信号的接收范围值小于信号输入范围值,由此能够促进信噪比的提升。采用过采样架构的CDR设计可以实现无时延的数字修复,而不是依赖于相位跟踪的方式,它可以在多个点对每个接收的数据位进行采集,从而实现更快的恢复速度。下图所示的CDR设计,正是为了满足这一需求而设计的。

为了有效地修复接受的信息,数字修复系统必须具有3个样品,其中含有数据寄存器、边沿检测器和数据选择器。数据寄存器可以暂时存储多相取样器采集的信息,而边沿检测器则可以确认哪些信息将被保存,以便进行进一步的数字修复。位边界探测器可以帮助数据选择器确认最佳的数据位边缘取样,以便将其保存下来,以便进行修复。

采用过采样CDR设计,可以大大缩短采集时间,同时也能够保持数据的安全性,此外,前馈操作机制还可以带来极高的数据带宽。由于过采样CDR技术可以有效地抑制高频抖动,并且可以在高速源-异步系统中实现频率偏移,因此它比传统的反馈相位跟踪和抖动传输技术更加适用于突发模式和连续型的数据传输。然而,它也存在一些缺点,比如必须高频数据转换,以及对采样数据存储需求较高的FIFO。

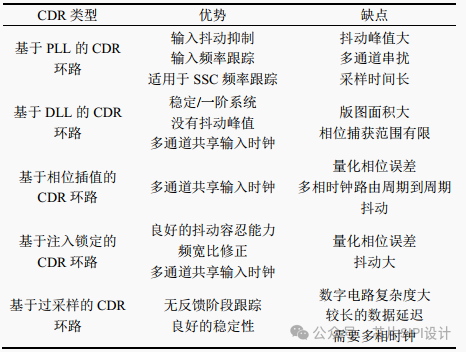

综合以上的分析,我们可以在表中看到不同的CDR存在不同的优势和缺点。具体的方案应该根据整体系统的特性对CDR方案进行选择。

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?