当今电子设计的趋势是推出尺寸、重量、功耗和成本(SWAP-C)优化的移动产品。因此,所有新设备(如智能手机或平板电脑)都采用非常小的外形尺寸、高速、高密度的印刷电路板(PCB)。PCB设计的复杂性源于新一代集成电路(IC)的开发和使用。这些组件具有更高的数据速率通信链路,意味着高频工作,低功耗要求导致低电压高敏感电源网络。最后,它们的高集成度导致芯片和PCB层面的电流密度增加。虽然几年前电源传输网络(PDN)的设计并不是主要关注点,但在SWAP-C设计背景下,它现在已成为一项极具挑战性的任务。信号之间的空间狭窄、由于尺寸减小而导致叠层中层数增加以及低功耗导致的电压电平降低,使得系统对电磁干扰(EMI)或信号与电源完整性(SPI)问题非常敏感。此外,成本优化的产品不允许过度设计。

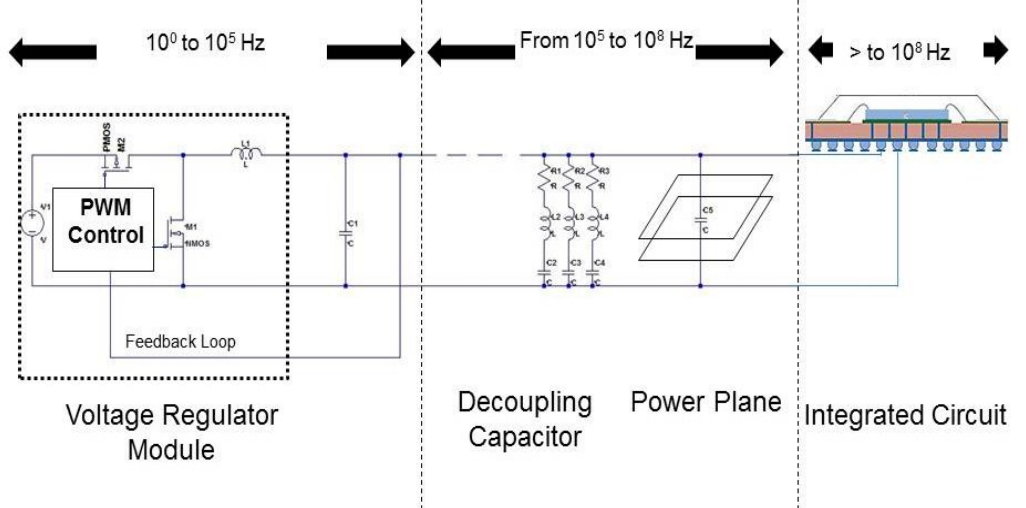

PDN的作用是在不同工作阶段为组件提供足够的电流电荷。必须在狭窄的电压电平容差范围内管理高电流变化。这些变化与从直流到最快电流瞬变的整个频率范围内的电源传输网络(PDN)阻抗有关。如图1所示,PDN包括电压调节模块,该模块主要是DC-DC转换器或低压差稳压器(LDO),是从直流到数百千赫兹的主要电流源。电源平面和连接的固有寄生电感往往会使PDN的阻抗随频率成比例增加。因此,使用去耦电容来保持阻抗低于目标阻抗。它们的效果从数百千赫兹到数百兆赫兹有效。最后,电源平面是PCB设计师可以用来满足目标阻抗要求的最后一个元素。

图1 电源PDN网络全链路示意图

为了保持竞争力并缩短PCB的设计周期,必须对PDN进行准确建模并进行有效的仿真,以便在制造和测试之前避免EMI和SPI问题。组件的I/O网络的电流波形由组件的IBIS模型给出。目标阻抗可以通过FFT计算获得。然而,描述微处理器核心电流波形的模型很少。集成电路包括其自身的封装内去耦。缺乏关于封装和芯片行为的信息是一个严重的限制,因为板上去耦电容的寄生电感与封装内电容之间的谐振可能导致阻抗峰值,进而违反目标阻抗。这就是为什么能够表征组件阻抗为PDN设计带来有价值信息的原因。

一、集成电路的特性表征

(一)测量设置

待评估的组件是Kintex7系列的FPGA XC7K160T。该组件被安装在专用于电源完整性测量的测试载体上。IC的PDN特性表征是通过按照[7]中的建议,使用安捷伦E5071C矢量网络分析仪(VNA)以并联方式测量核心电源网络VCCINT的S12参数来实现的。使用两个自制探针,这些探针由一侧切开的SMA电缆制成,在其上分别将小电线焊接到中心芯和金属屏蔽层用于电流返回。使用这两个探针进行SOLT校准,以消除它们对测量结果的影响。然后将这两个探针直接焊接到BGA组件的焊球上。中心芯焊接到VCCINT网络的N15和R15引脚,而金属屏蔽层焊接到阵列上最近的GND引脚N14和R14。焊接探针的详细视图可以在图2中看到。

图2 芯片焊球上测试探针点的细节视图

(二)获得的结果

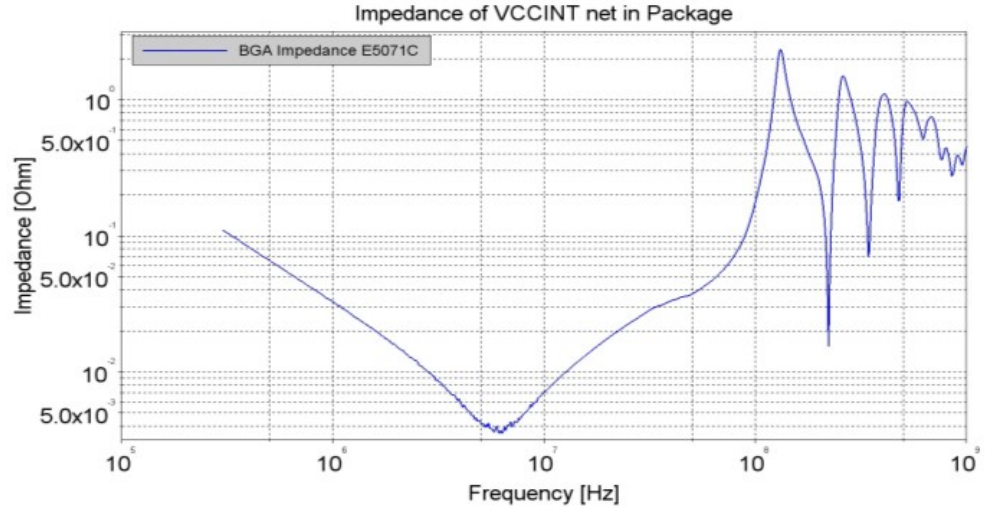

从300 kHz到1 GHz测量S12参数,然后使用Scilab脚本将其转换为Z参数。转换后的阻抗如图3所示。测量表明,在300 kHz到约6 MHz之间,阻抗主要是容性的,对应于组件的电容(芯片电容、晶体管的寄生电容)之和。在其最小值之后,阻抗主要变为感性的。通过去耦电容,阻抗曲线似乎在80 MHz之前保持在约50 mOhm的低水平。此后阻抗急剧增加。

图3 通过S12测量计算得出的电源总阻抗

(三)分析

上面测试中获得的结果并不代表BGA焊接到PCB上后的确切阻抗。实际上,在实际应用中,当VCCINT网络通过16个引脚连接到平面时,仅在2对引脚上测量了VCCINT网络的阻抗。由于更多引脚的连接是并联放置的,因此允许降低封装的电阻和电感寄生效应。由于BGA组件和PCB之间关联的测量将考虑连接到所研究网络的所有引脚,因此执行了特殊的安装,以使整个系统的测量类似于仅对组件的测量。仅将VCCINT和GND网络的2个引脚焊接到PCB上,而保留连接到其他网络的额外焊球,以便将组件正确焊接到PCB上。

二、整个PDN的模型和仿真

(一)电压调节模块

电压调节模块可以在时域中通过制造商通常提供的精确SPICE模型来建模,以模拟组件的非线性行为,或者在频域中建模,在这种情况下,VRM的行为对应于其频域相关的输出阻抗。在这种情况下,VRM的模型是四元件线性模型。

(二)电源平面和去耦电容

电源平面的复杂形状通过2.5D混合电磁求解器中的S参数仿真来建模。此外,可以在求解器中将电容模型附加到平面上,以查看它们的效果。电容可以通过等效RLC串联电路或通过输入制造商提供的S参数模型来建模。从仿真获得的S参数文件然后使用脚本转换为Z参数文件。

(三)芯片和封装

从PCB设计师的角度来看,该组件是一个黑箱,因为存在用于封装和芯片仿真的不同模型。对于I/O网络,芯片和封装的阻抗在IBIS模型的寄生部分中给出。相同的模型可用于时域仿真,因为它包含电流和电压波形。关于组件核心,仅存在很少的模型。源自同名标准的ICEM模型将集成电路描述为无源PDN和由电流源构成的有源部分。然而,该模型更专注于在CEM环境中模拟发射和传导噪声,并且很少可用。但同样,该模型并不常见。这就是为什么在这种PDN设计方法中使用从测量获得的组件行为的原因。

(四)PDN全局仿真

1. 频域

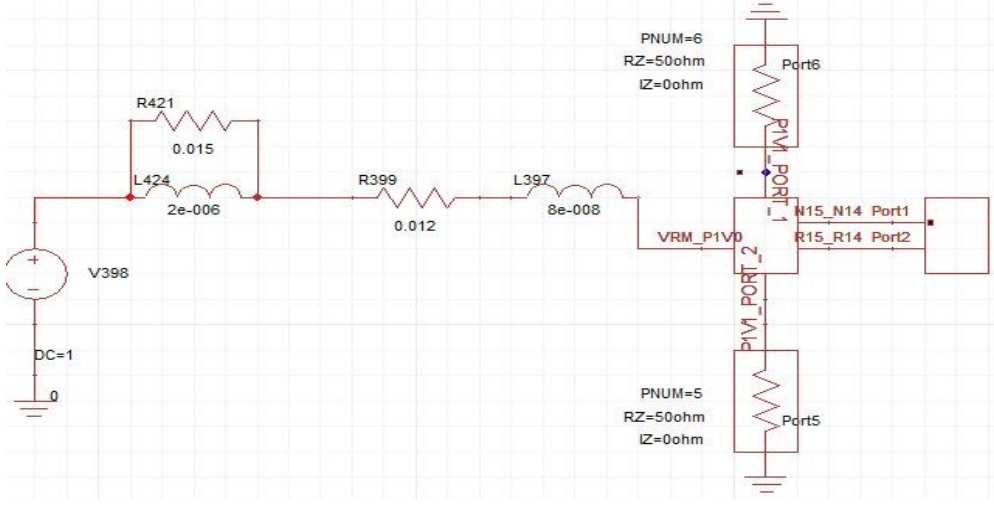

完整PDN的仿真可以通过在电子设计自动化(EDA)软件中将所有模型组装为S参数模块来获得。图4显示了整个PDN的 schematic 仿真视图。这四个无源元件代表VRM,第一个模块代表PCB和去耦电容,最后一个模块是直接在组件上测量的S参数。分析结果转换为Z参数如图9所示。

图4 PDN仿真原理图

2. 时域

为了在时域中运行仿真,必须使用VRM的SPICE模型。由于S参数是频域的,因此必须将S参数转换为SPICE子电路。最后,与时域分析中引入电流概念作为目标阻抗不同,在时域中必须通过动态电流源对电流进行建模。

三、测试correlation

设计了一个用于电源完整性测量的测试载体。它是一个14层、1.6mm厚的PCB,带有两层微过孔。主要组件是第二部分中研究的Kintex 7 XC7K160T。测试载体的概述如图5所示。为了查看仿真方法的准确性,第三部分中描述的所有模型都将与测量相关联。

图5 测试的板子

(一)模型

1. VRM

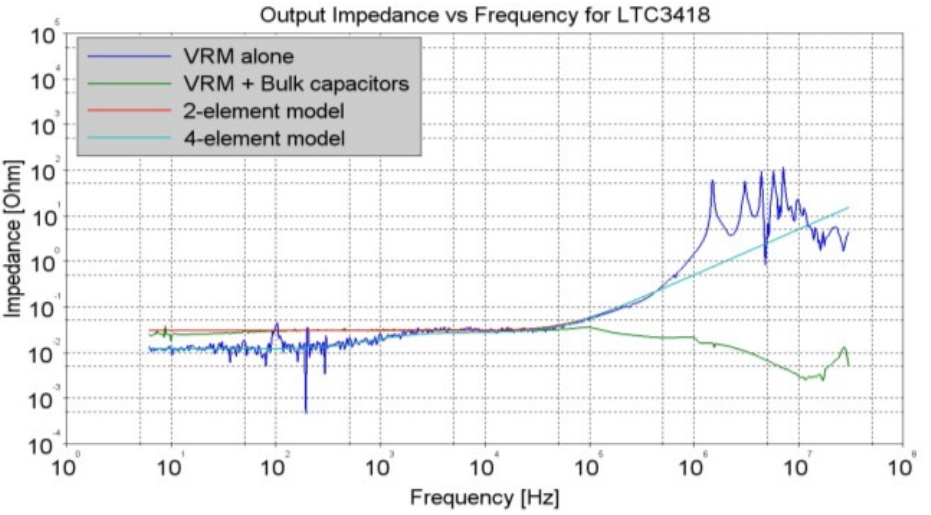

VRM的输出阻抗是通过实现Linear Technology的DC-DC转换器LTC3418的专用PCB来测量的。在不同的静态负载条件下测量输出阻抗。在图6中可以观察到,直到50 KHz,测量与二元件或四元件模型之间有很好的相关性。值得一提的是,模型不随负载条件而变化。

图6 DC-DC转换器LTC3612 测量与模型的Correlation

(二)平面和电容

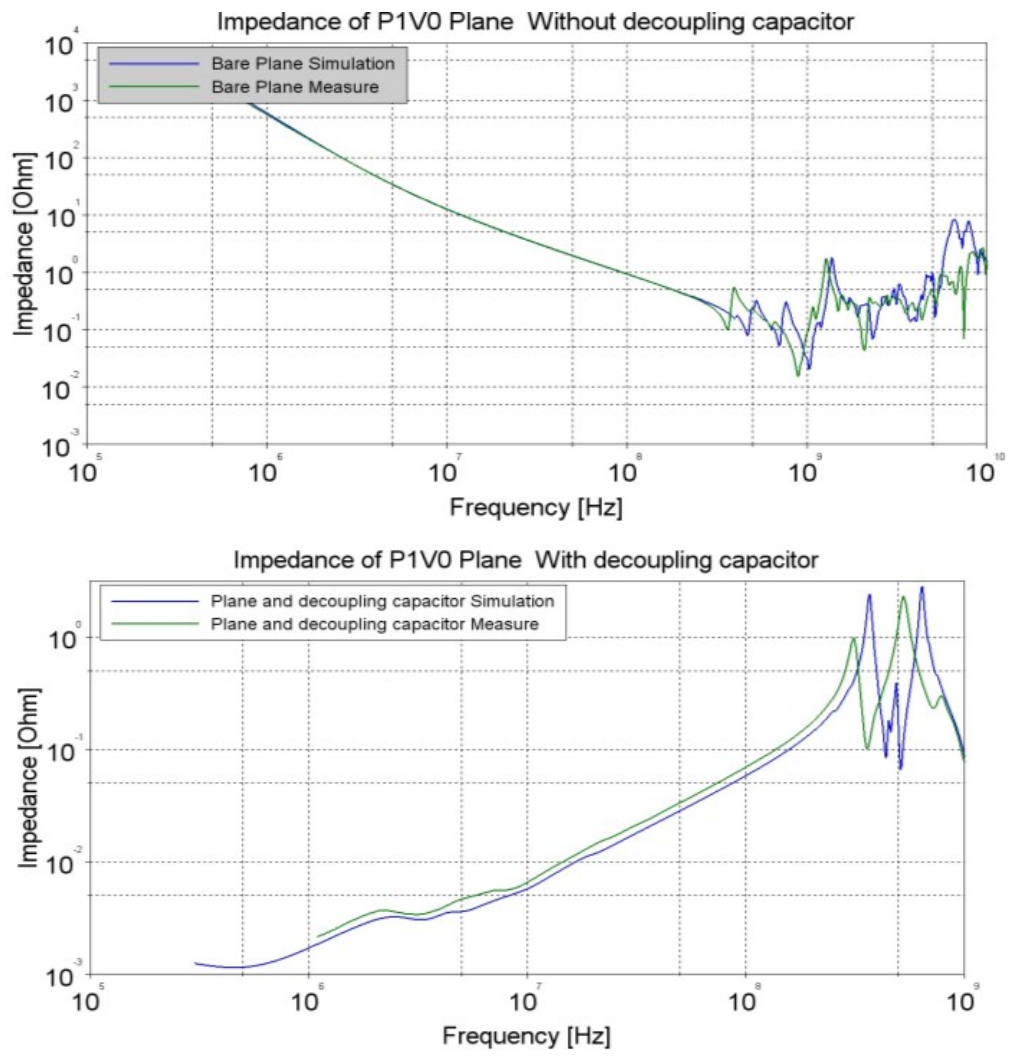

在裸PCB和配备去耦电容的PCB上测量平面和去耦电容的行为。通过连接到VCCINT网络的2个SMA连接器进行VNA测量。首先使用带有电子校准模块的SOLT技术对VNA进行校准。测量在300 KHz至1 GHz之间进行。通过将其与测量结果进行比较,图7a和7b证明了仿真工具的准确性。

图7 仿真和实测Correlation:裸板(图7a)、带去耦电容板(图7b)

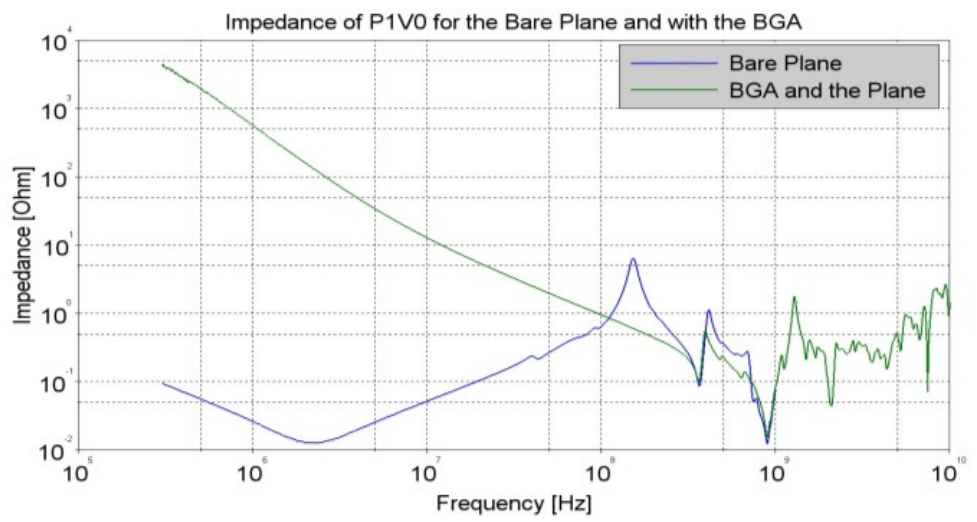

(三)芯片和封装在PDN设计中的影响

为了检查将IC阻抗的测量结果输入到仿真器中的方法的准确性,重复上述段落中描述的设置,但将组件焊接到PCB上且没有去耦电容。如图8所示,组件的影响不可忽略。这就是为什么在PDN设计中包含IC的封装和封装内去耦是一个明显优势的原因。

图8 裸平面与焊接在PCB上的BGA组件的对比

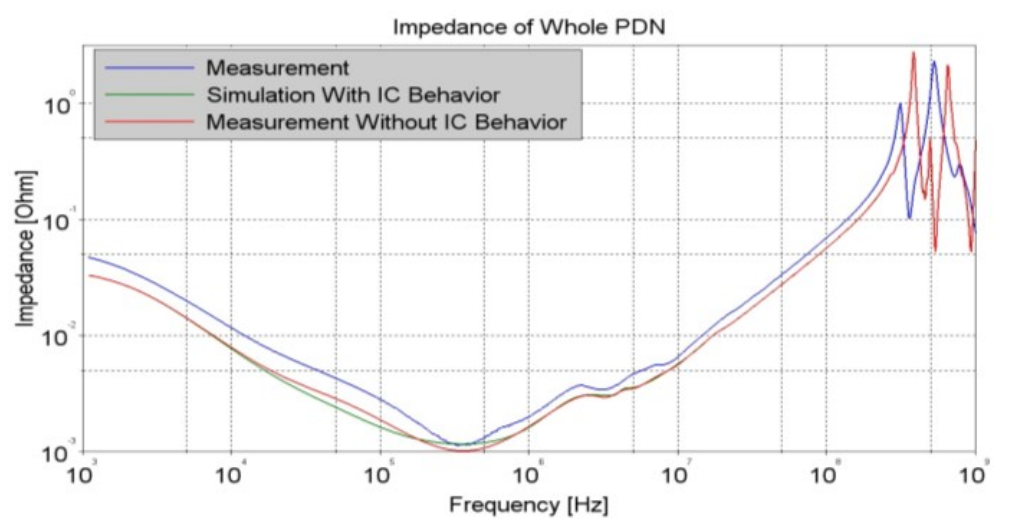

最后,通过将包括IC行为的方法与测试载体的整个PDN的测量结果进行比较来验证该方法,当然也将其与缺少IC信息的经典仿真进行比较。比较结果呈现在图9中。首先可以评论的是,这两种仿真都代表了整个PDN的行为。然而,可以看出,包括IC寄生效应(特别是其电容)的仿真比忽略它的方法给出了更好的结果。

图9 整个PDN的阻抗

四、结论

上文对电源进行了全链路PDN设计的仿真分析,并通过与测量结果的对比进行了验证。这些结果阐明了在PCB电源网络设计期间没有可用模型时,纳入通过测量获得的芯片和封装PDN行为的影响。该方法的难点在于找到合适的测量配置,以便可以对BGA组件和PCB之间的相互作用进行建模和仿真。

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?