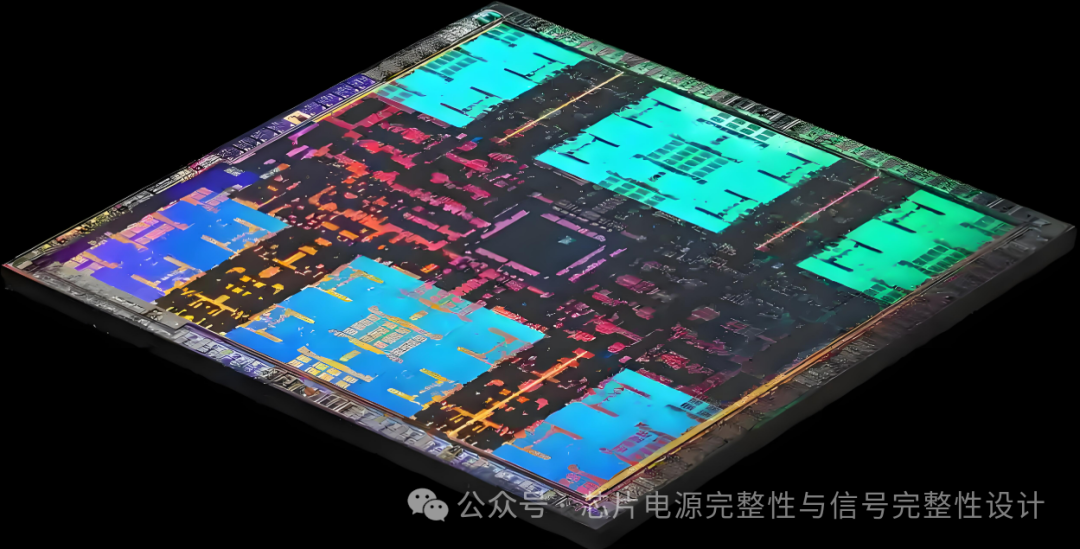

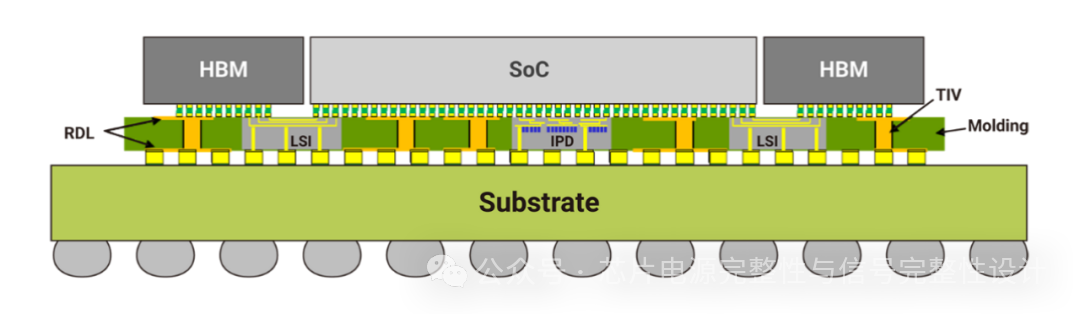

Chiplet是一种将多个小芯片(die)通过先进封装技术集成在一起的架构,比如Intel的EMIB或者台积电的CoWoS。这种设计可以提高良率、降低成本,并允许异构集成。不过,这也带来了电源和信号完整性方面的挑战。

首先,电源完整性(PI)。在传统的单芯片设计中,电源分布网络(PDN)设计已经比较复杂了,但Chiplet中多个小芯片集成在一个封装里,可能使用不同的工艺节点,每个小芯片的功耗和电压需求可能不同。此外,供电路径可能更长,寄生参数更多,导致电压降(IR Drop)和电源噪声问题更严重。这时候需要考虑封装基板的电源分布、去耦电容的布局、各Chiplet之间的电源传输以及同步开关噪声(SSN)等问题。

然后是信号完整性(SI)。Chiplet之间通过高密度互连,如硅中介层或再分布层(RDL)连接,信号速率可能很高,比如56Gbps或更高。这会带来串扰、反射、损耗等问题。同时,不同Chiplet之间的接口标准可能不同,需要保持信号时序的一致性和正确的阻抗匹配。此外&

然后是信号完整性(SI)。Chiplet之间通过高密度互连,如硅中介层或再分布层(RDL)连接,信号速率可能很高,比如56Gbps或更高。这会带来串扰、反射、损耗等问题。同时,不同Chiplet之间的接口标准可能不同,需要保持信号时序的一致性和正确的阻抗匹配。此外&

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

605

605

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?