逻辑单元库的建立:

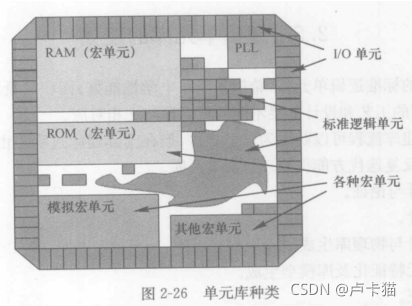

一个完整的单元库是由不同的功能电路所组成,在芯片应用中可分为三类:

- 标准单元:反相器、与门、寄存器、选择器、全加器。组合逻辑电路和时序逻辑电路。互补,反向,非反向,其他。锁存器、寄存器。

- 模块宏单元:ROM、RAM

- 输入输出单元

库文件:

在逻辑综合产生门级网表和物理设计做布局布线的过程中需要两个重要的库文件,就是物理库(lef)和时序库(lib)

1.物理库LEF文件

LEF(Library Exchange Format)是版图级的抽象文件,主要用于布局和布线。目前普遍使用的是由Candence开发的LEF文件格式,以lef作为库文件后缀,采用ASCII格式描述,易于阅读和维护。文件很大,为方便管理和维护,一般分为技术LEF文件和单元LEF文件。

- 技术LEF主要定义的是布局布线的设计规则和晶圆厂的工艺信息。

- 单元LEF文件主要用于定义标准单元、模块单元、I/O单元和各种特殊单元的物理信息。

2.时序库liberty文件

时序库是描述单元时序信息的重要文件。它定义了每个单元不同输入情况下各输入端口到输出端口信号的传播延时,工具通过仿真不同工艺角条件下电路的工作状态得到相应的时序数据,再将数据转换成工具可以事变的库交换文件用于芯片的时序分析。

liberity是目前业界广泛使用的时序库文件格式,由Synopsys公司开发定义,以lib作为扩展名。

- 时序库的PVT(工艺、电压、温度)条件应用条件,不管采用那种格式,需要定义最基本的时间、电压和电流等基本物理单位。

- 线负载模型,器件延时也称传播延时,表示信号通过一个逻辑门时所经历的时间,反应了门对输入信号变化响应的快慢。是与它输入端口信号的转换时间和输出端口负载相关。

- 时序库主要由单元信息组成,每个单元与LEF文件中的单元一一对应。包括:1.不同时序模型条件下延迟时间表、功耗数值表。2.单元的面积、静态功耗、端口、输入端口包括负载电容。3.端口的逻辑关系。4.噪声语法

SDC文件

设计约束文件SDC(Synopsys design constraints)文件基于TCL格式。SDC对电路的时序、功耗、面积等进行约束,从而使芯片满足设计要求的规范。

tech file

工艺技术文件(technology file) 是晶圆代工厂提供给设计者用于后端版图设计的技术文件,同时它也是用于与EDA工具交互工艺信息的常用文件。一般包含图形定义及显示信息、互连线工艺信息和通孔工艺信息等。互连线工艺信息包含的内容非常多,如金属最高加工层数、方向、最小线宽、最小线间距、电容电阻大小、天线效应大小、金属最大电流等。通孔信息包括各层通孔的种类、通孔电阻电容大小、连接关系等。

init design 为什么要先导入tech.lef,之后才是lef?

因为tech lef中有各种site row的定义。如果这个定义没有先读入,标准单元,ip的lef中有声明cell是要放在哪种site上的声明就会报error,所以要先定义再引用。

| 时序 | 工艺 | 网表 |

|---|---|---|

| SDC文件 | lef文件 | verilog |

| lib文件 | tech file | |

| rlc文件 |

本文详细介绍了集成电路设计中的逻辑单元库,包括标准单元、模块宏单元和输入输出单元,以及物理库LEF和时序库Liberty文件的作用。LEF文件描述布局布线规则和单元物理信息,Liberty文件则包含单元的时序信息,用于时序分析。设计约束文件SDC和工艺技术文件techfile也是设计过程中的关键。时序、工艺和网表是设计中的重要因素,而SDC文件则对这些方面进行约束以满足设计规范。

本文详细介绍了集成电路设计中的逻辑单元库,包括标准单元、模块宏单元和输入输出单元,以及物理库LEF和时序库Liberty文件的作用。LEF文件描述布局布线规则和单元物理信息,Liberty文件则包含单元的时序信息,用于时序分析。设计约束文件SDC和工艺技术文件techfile也是设计过程中的关键。时序、工艺和网表是设计中的重要因素,而SDC文件则对这些方面进行约束以满足设计规范。

1560

1560

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?