| `timescale 10ns/1ns

module verilogtest_sim(); reg clk; reg [1:0]a, b; reg sel; reg reset; reg [1:0]out;

initial begin clk = 0; forever #1 clk = ~clk; end

reg op_and, op_or;

initial begin a = 2'b11; b = 2'b01; op_and = 0; op_or = 0; sel = 1; reset = 1; #4 reset = 0; #2 reset = 1; #5 reset = 0; #2 reset = 1; #8 $stop; end

always @(posedge clk) begin if(!reset) out <= 2'b0; else out <= 2'bz; end

always @(posedge clk) begin if(!reset) begin op_and <= 0; op_or <= 0; end else begin if(sel) begin op_and <= 1; op_or <= 0; end else begin op_and <= 0; op_or <= 1; end end end

always @(posedge clk) begin if(op_and) out <= a & b; else out <= 2'bz; end

always @(posedge clk) begin if(op_or) out <= a | b; else out <= 2'bz; end

endmodule |

另一例子:

| module exe(dir, a, b, out); input a, b; input [1:0] dir; output out; reg out;

always @(dir or a) begin if(dir == 2'b01) out <= a; else out <= 1'bz;

end

always @(dir or b) begin if(dir == 2'b10) out <= b; else out <= 1'bz; end

endmodule

| module exe(dir, a, b, out); input a, b; input [1:0] dir; output out; reg out;

always @(dir or a or b) begin if(dir == 2'b01) out <= a; else if(dir == 2'b10) out <= b; else out <= 1'bz;

end

endmodule |

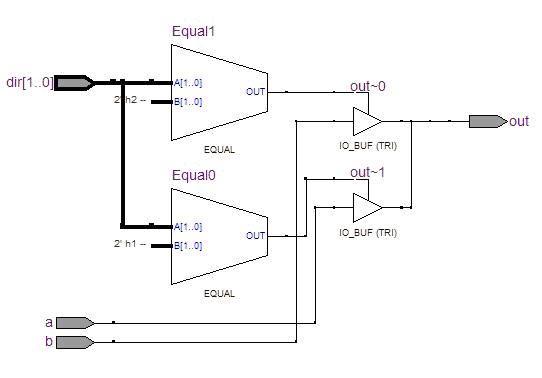

左边的RTL:

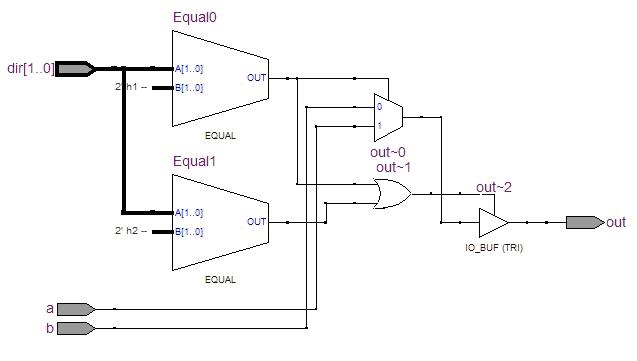

右边的RTL:

结论:可以在不同always中对同一信号赋值,但要小心,不推荐这么做。

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?