4.4 常用的组合逻辑电路模块

4.4.1 编码器

在数字系统中,为了区分一系列不同的事务,将其中的每个事物用一个二值代码表示,这就是编码的含义。在二值逻辑电路中,信号都是以高、低电平的形式给出的。因此,编码器(Encoder)的逻辑功能就是将输入的每一个高、低电平信号编成一个对应的二进制代码。

一、普通编码器

目前经常使用的编码器有普通编码器和优先编码器两类。在普通编码器中,任何时刻只允许输入一个编码信号,否则输出将发生混乱。

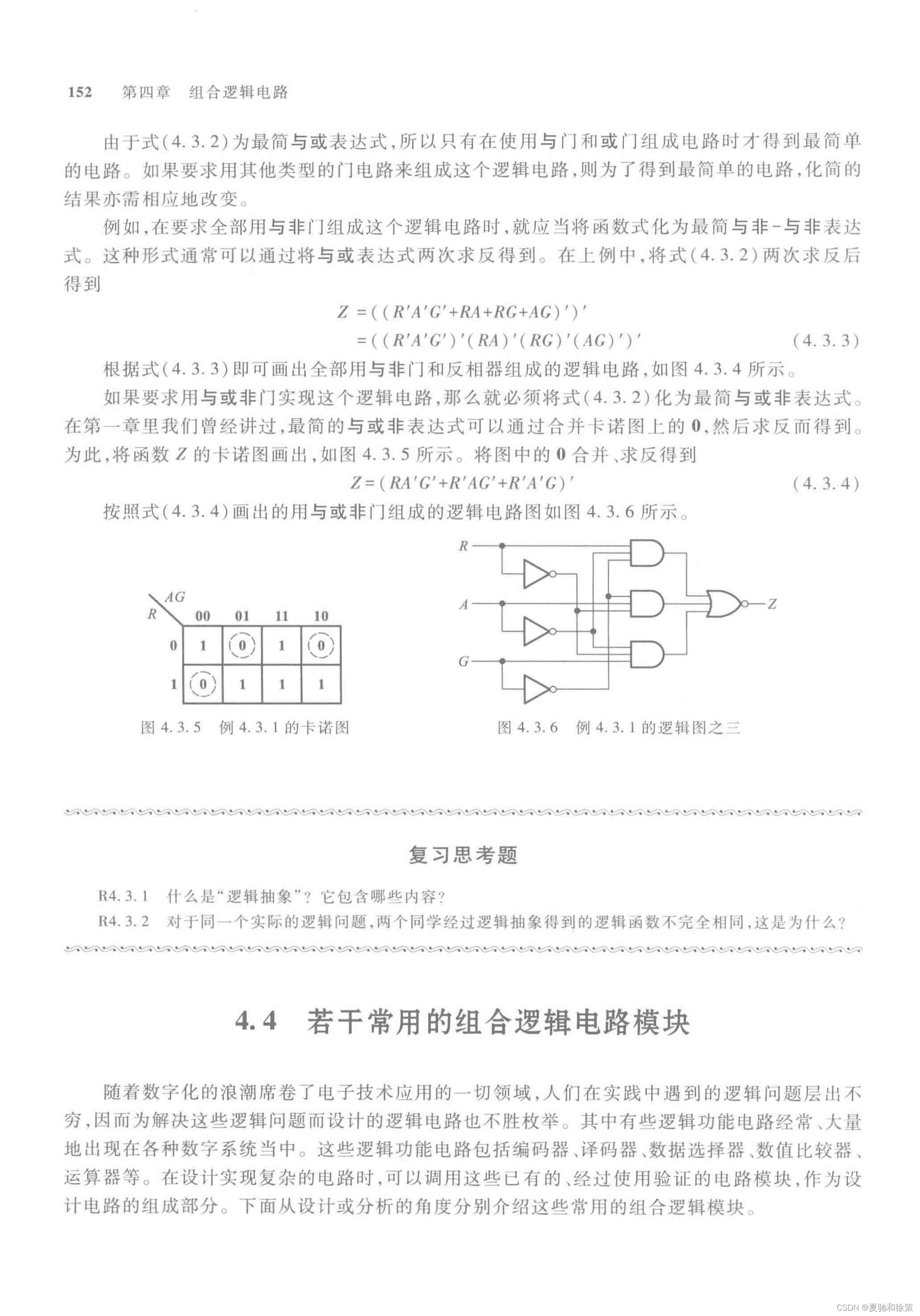

现以3位二进制普通编码器为例,分析一下普通编码器的工作原理。图4.4.1是3位二进制编码器的框图,它的输入是 𝐼0∼𝐼7I0∼I7,八个高电平信号,输出是3位二进制代码 𝑌2,𝑌1,𝑌0Y2,Y1,Y0。因此,又将它称为8线-3线编码器。输出与输入的对应关系由表4.4.1给出。

表4.4.1 3位二进制编码器的真值表

| 输入 | 输出 |

|---|---|

| 𝐼0I0 | 000 |

| 𝐼1I1 | 001 |

| 𝐼2I2 | 010 |

| 𝐼3I3 | 011 |

| 𝐼4I4 | 100 |

| 𝐼5I5 | 101 |

| 𝐼6I6 | 110 |

| 𝐼7I7 | 111 |

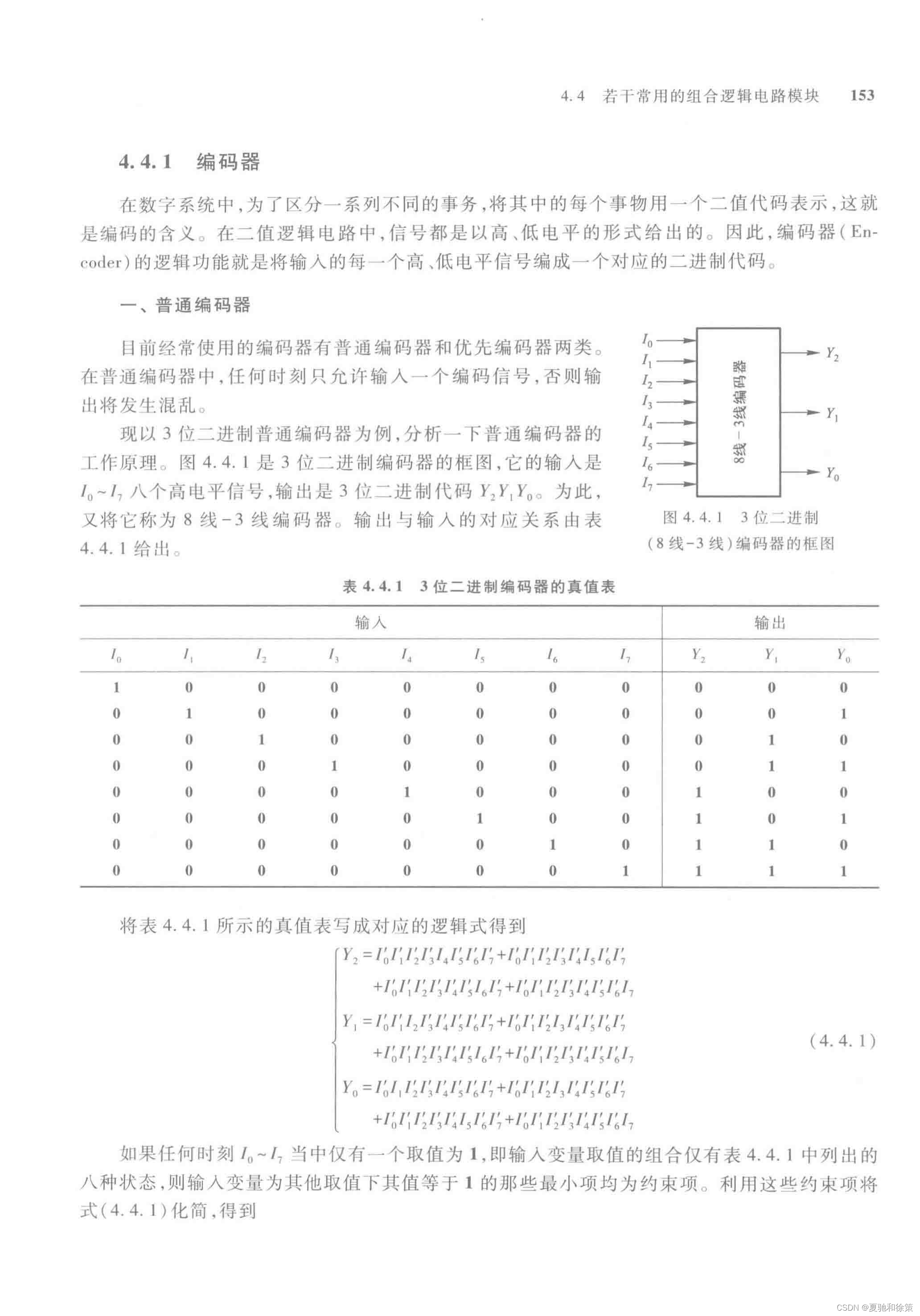

将表4.4.1所示的真值表写成对应的逻辑式得到: 𝑌2=𝐼4+𝐼5+𝐼6+𝐼7Y2=I4+I5+I6+I7 𝑌1=𝐼2+𝐼3+𝐼6+𝐼7Y1=I2+I3+I6+I7 𝑌0=𝐼1+𝐼3+𝐼5+𝐼7Y0=I1+I3+I5+I7

图4.4.2就是根据以上逻辑式得出的编码器电路。这个电路是由三个或门组成的。

二、优先编码器

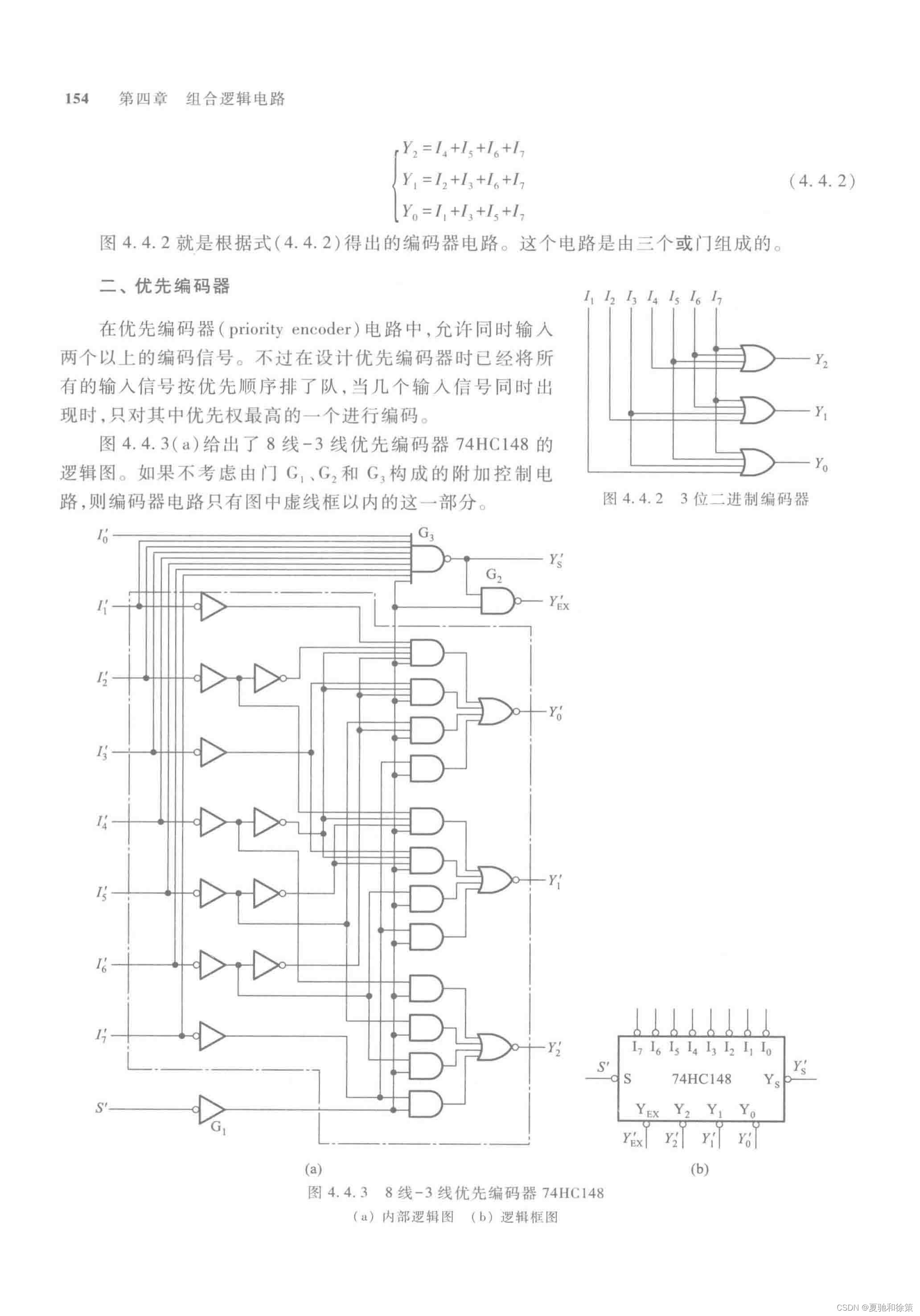

在优先编码器(priority encoder)电路中,允许同时输入两个以上的编码信号。不过在设计优先编码器时已经将所有的输入信号按优先顺序排了队,当几个输入信号同时出现时,只对其中优先权最高的一个进行编码。

图4.4.3(a)给出了8线-3线优先编码器74HC148的逻辑图。如果不考虑由门 𝐺1,𝐺2G1,G2 和 𝐺3G3 构成的附加控制电路,则编码器电路只有图中虚线框以内的这一部分。

由图4.4.3(a)写出输出逻辑式,即得到: 𝑌2=𝐼4+𝐼5+𝐼6+𝐼7Y2=I4+I5+I6+I7 𝑌1=𝐼2+𝐼3+𝐼6+𝐼7Y1=I2+I3+I6+I7 𝑌0=𝐼1+𝐼3+𝐼5+𝐼7Y0=I1+I3+I5+I7

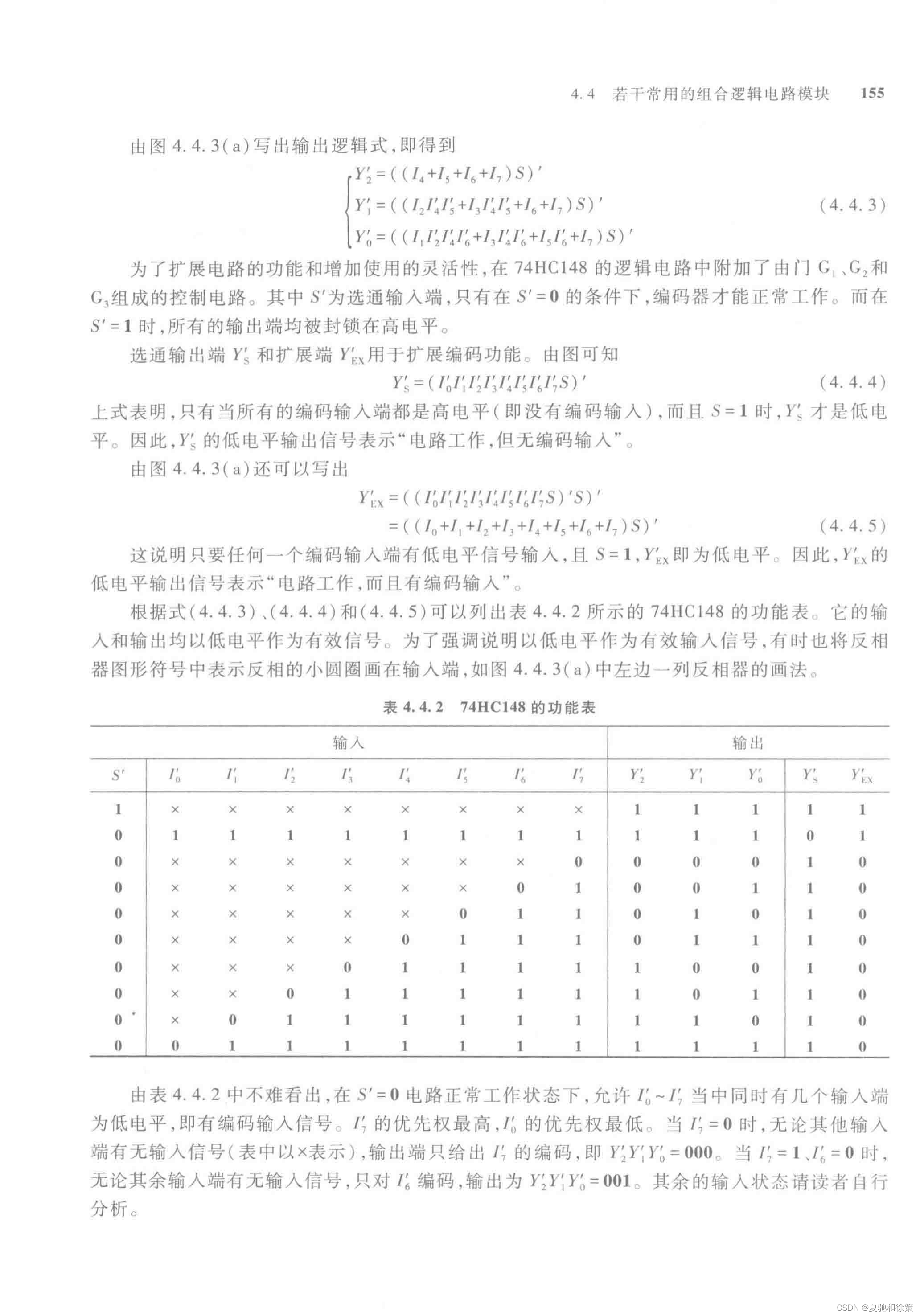

为了扩展电路的功能和增加使用的灵活性,在74HC148的逻辑电路中附加了由门 𝐺1,𝐺2G1,G2 和 𝐺3G3 组成的控制电路。其中 𝑆′S′ 为选通输入端,只有在 𝑆′=0S′=0 的条件下,编码器才能正常工作。而在 𝑆′=1S′=1 时,所有的输出端均被封锁在高电平。选通输出端 𝑌𝑠Ys 和扩展端 𝑌𝐸𝑋YEX 用于扩展编码功能。

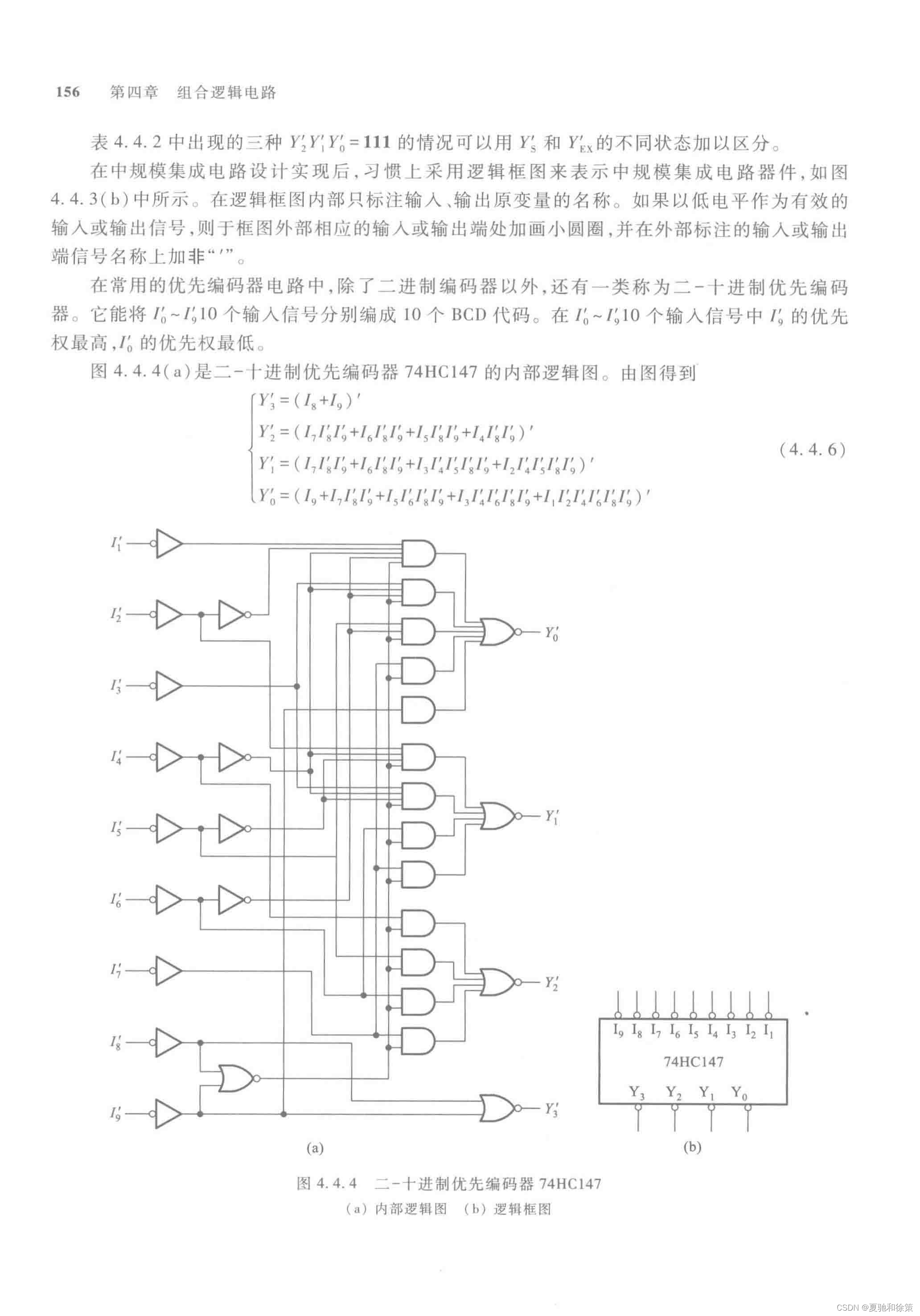

在常用的优先编码器电路中,除了二进制编码器以外,还有一类称为二-十进制优先编码器。它能将 𝐼0∼𝐼9I0∼I9 10个输入信号分别编成10个BCD代码。在 𝐼0∼𝐼9I0∼I9 输入信号中,𝐼9I9 的优先权最高,𝐼0I0 的优先权最低。

图4.4.4(a)是二-十进制优先编码器74HC147的内部逻辑图。

由图得到: 𝑌3=𝐼8+𝐼9Y3=I8+I9 𝑌2=𝐼4+𝐼5+𝐼6+𝐼7+𝐼8+𝐼9Y2=I4+I5+I6+I7+I8+I9 𝑌1=𝐼2+𝐼3+𝐼6+𝐼7+𝐼10+𝐼11+𝐼12+𝐼13+𝐼14+𝐼15Y1=I2+I3+I6+I7+I10+I11+I12+I13+I14+I15 𝑌0=𝐼1+𝐼3+𝐼5+𝐼7+𝐼9+𝐼11+𝐼13+𝐼15Y0=I1+I3+I5+I7+I9+I11+I13+I15

编码器的输出是反码形式的BCD码。优先权以 𝐼9I9 为最高,𝐼0I0 为最低。当 𝐼0∼𝐼9I0∼I9 均为无效输入(均为1)时,隐含表示了 𝐼9I9 为有效输入,编码输出 𝑌3𝑌2𝑌1𝑌0=1111Y3Y2Y1Y0=1111。

表4.4.3 二-十进制编码器74HC147的功能表

| 输入 | 输出 |

|---|---|

| 𝐼0I0 | 0000 |

| 𝐼1I1 | 0001 |

| 𝐼2I2 | 0010 |

| 𝐼3I3 | 0011 |

| 𝐼4I4 | 0100 |

| 𝐼5I5 | 0101 |

| 𝐼6I6 | 0110 |

| 𝐼7I7 | 0111 |

| 𝐼8I8 | 1000 |

| 𝐼9I9 | 1001 |

这节内容详细介绍了编码器和优先编码器的工作原理及其实现方式,结合了具体的电路图和逻辑表达式,帮助读者更好地理解这些常用的组合逻辑模块。

4.4 常用的组合逻辑电路模块

4.4.2 译码器

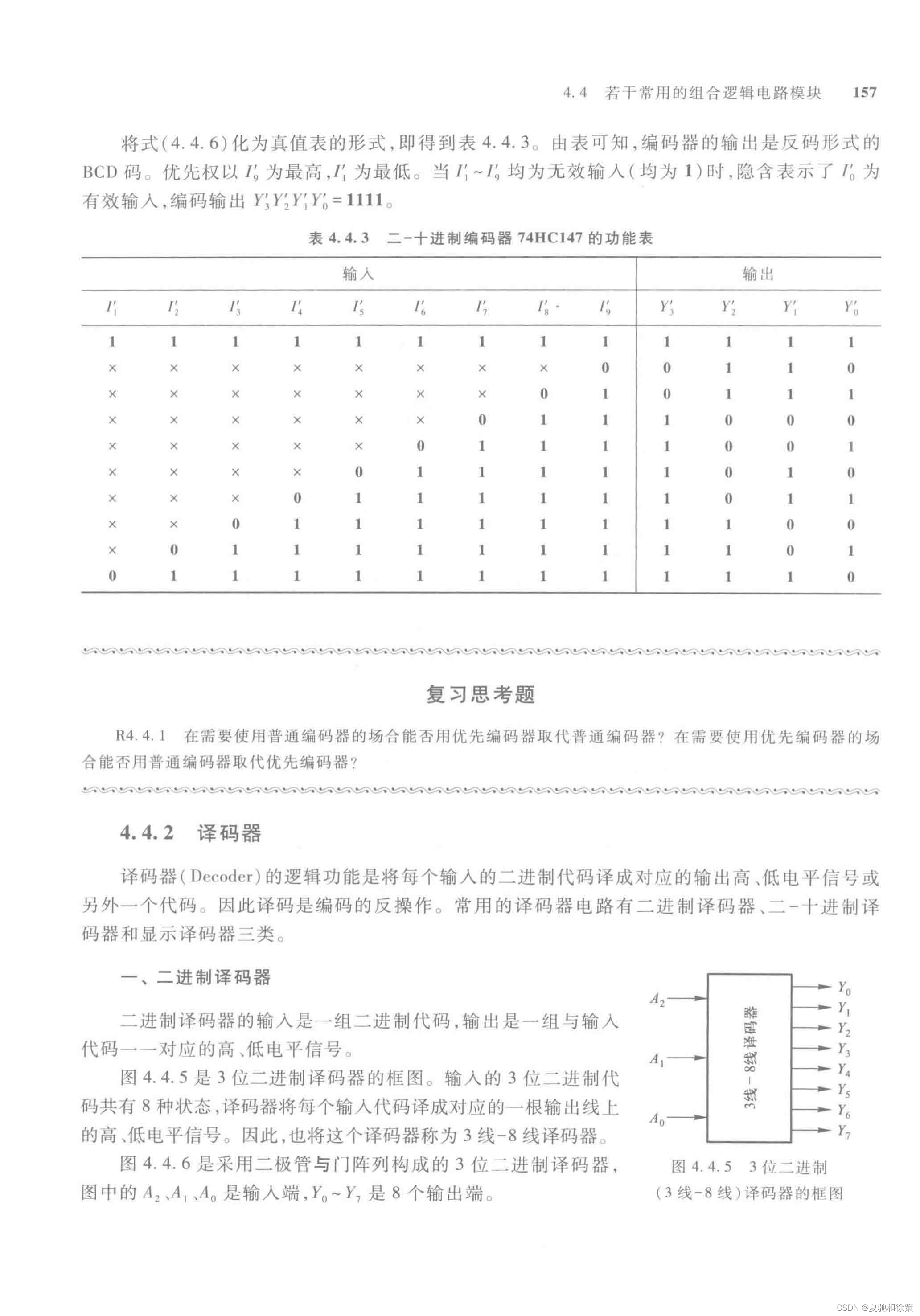

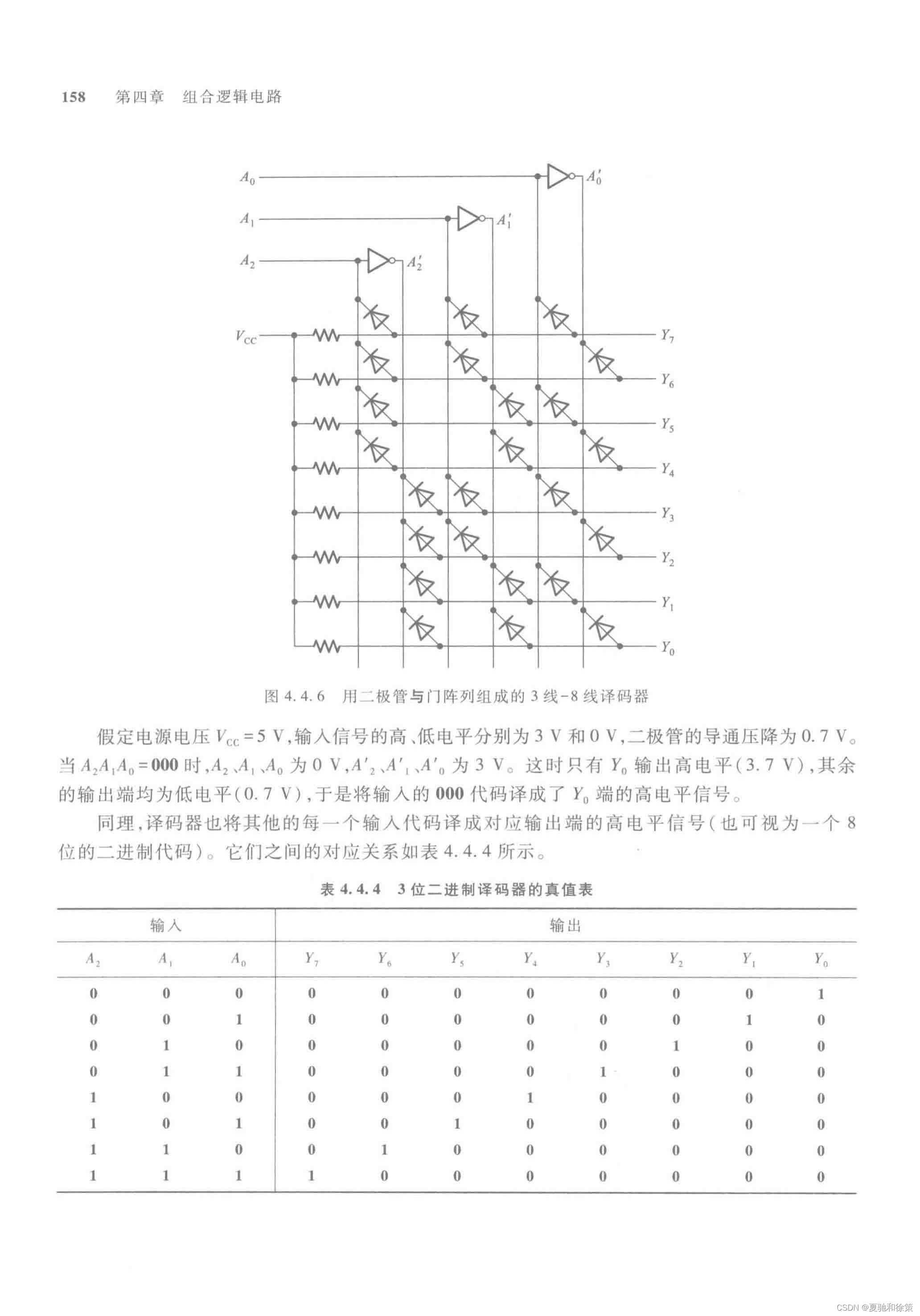

译码器(Decoder)的逻辑功能是将每个输入的二进制代码译成对应的输出高、低电平信号或另外一个代码。因此,译码是编码的反操作。常用的译码器电路有二进制译码器、二-十进制译码器和显示译码器三类。

一、二进制译码器

二进制译码器的输入是一组二进制代码,输出是一组与输入代码对应的高、低电平信号。图4.4.5是3位二进制译码器的框图。输入的3位二进制代码共有8种状态,译码器将每个输入代码译成对应的一根输出线上的高、低电平信号。因此,也将这个译码器称为3线-8线译码器。图4.4.6是采用二极管与门阵列构成的3位二进制译码器,图中的 𝐴2,𝐴1,𝐴0A2,A1,A0 是输入端, 𝑌0∼𝑌7Y0∼Y7 是8个输出端。

假定电源电压 𝑉𝐶𝐶=5𝑉VCC=5V,输入信号的高、低电平分别为3V和0V,二极管的导通压降为0.7V。当 𝐴2,𝐴1,𝐴0=000A2,A1,A0=000 时, 𝐴2′,𝐴1′,𝐴0′A2′,A1′,A0′ 为0 V,𝐴2′,𝐴1′,𝐴0′A2′,A1′,A0′ 为3V。这时只有 𝑌0Y0 输出高电平(3.7 V),其余的输出端均为低电平(0.7 V),于是将输入的000代码译成了 𝑌0Y0 端的高电平信号。同理,译码器也将其他的每一个输入代码译成对应输出端的高电平信号(也可视为一个8位的二进制代码)。它们之间的对应关系如表4.4.4所示。

表4.4.4 3位二进制译码器的真值表

| 输入 | 输出 |

|---|---|

| 𝐴2,𝐴1,𝐴0A2,A1,A0 | 𝑌7,𝑌6,𝑌5,𝑌4,𝑌3,𝑌2,𝑌1,𝑌0Y7,Y6,Y5,Y4,Y3,Y2,Y1,Y0 |

| 000 | 00000001 |

| 001 | 00000010 |

| 010 | 00000100 |

| 011 | 00001000 |

| 100 | 00010000 |

| 101 | 00100000 |

| 110 | 01000000 |

| 111 | 10000000 |

用二极管与门阵列构成的译码器虽然比较简单,但也存在两个严重的缺点。其一是电路的输入电阻较低而输出电阻较高,其二是输出的高、低电平信号发生偏移(偏离输入信号的高、低电平)。因此,通常只在一些大规模集成电路内部采用这种结构,而在一些中规模集成电路译码器中多半采用三极管集成门电路结构。

二、二-十进制译码器

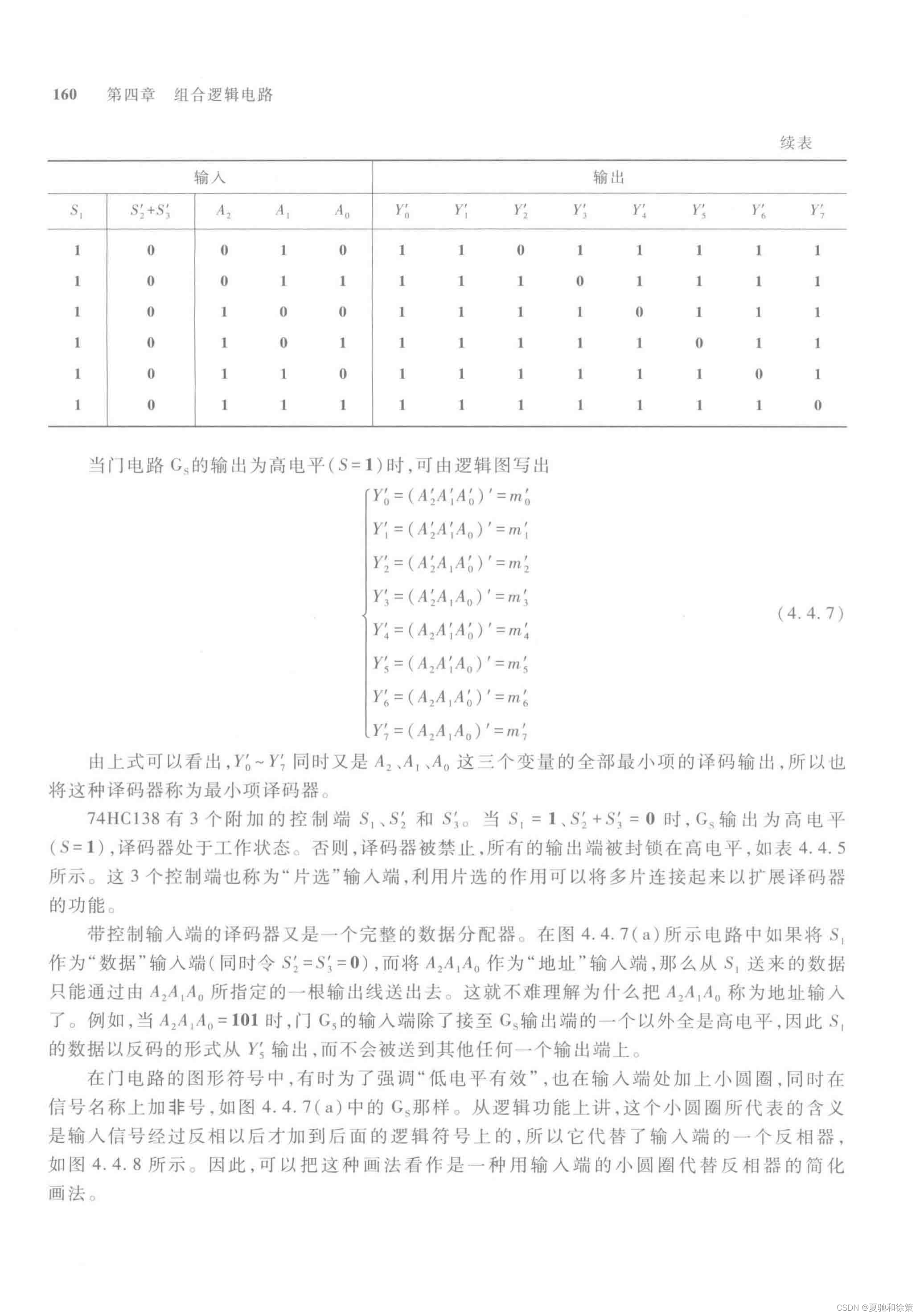

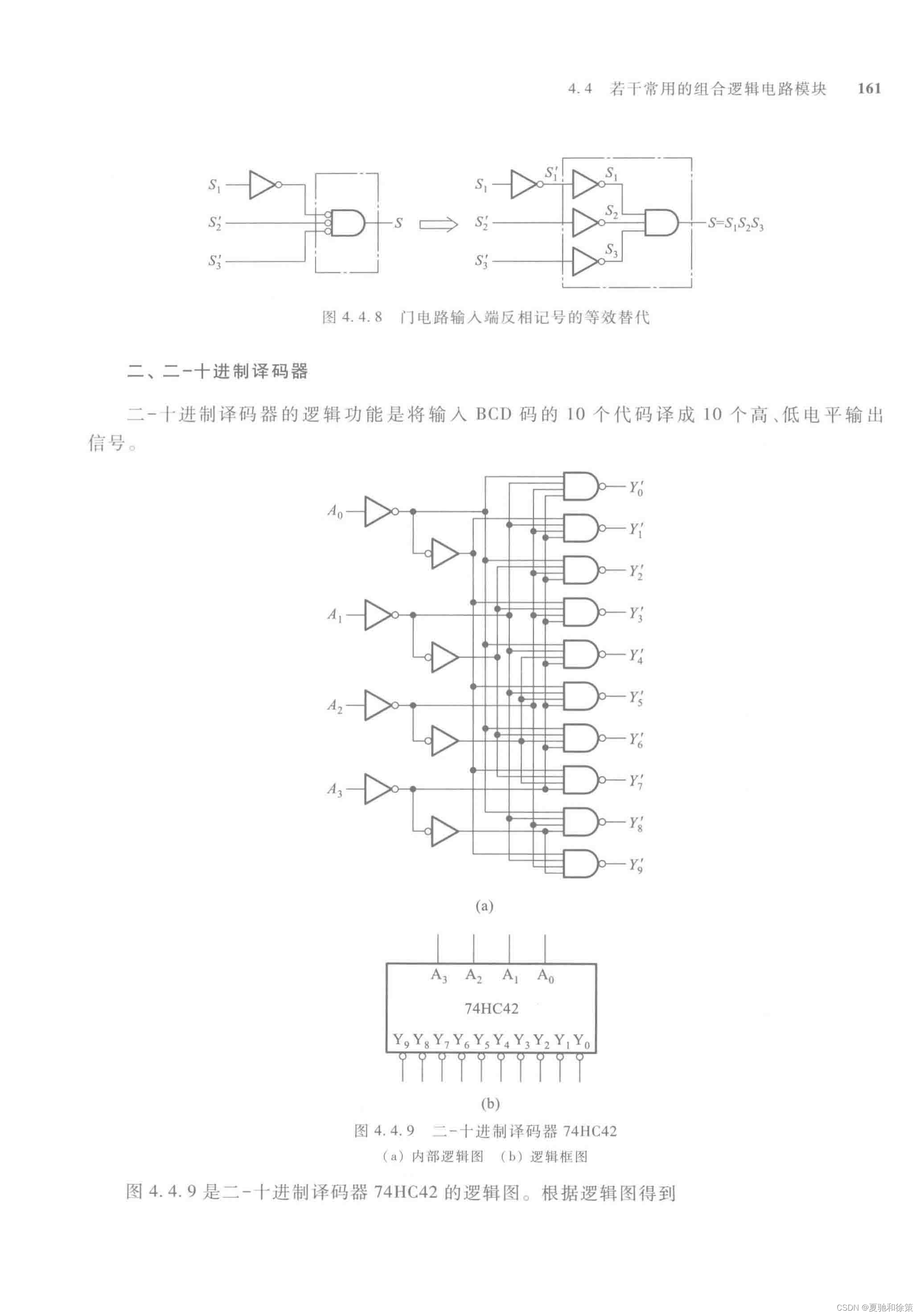

二-十进制译码器的逻辑功能是将输入BCD码的10个代码译成10个高、低电平输出信号。图4.4.9是二-十进制译码器74HC42的逻辑图。根据逻辑图得到:

𝑌9=𝐴3′𝐴2′𝐴1′𝐴0Y9=A3′A2′A1′A0 𝑌8=𝐴3′𝐴2′𝐴1′𝐴0′Y8=A3′A2′A1′A0′ 𝑌7=𝐴3′𝐴2′𝐴1𝐴0′Y7=A3′A2′A1A0′ 𝑌6=𝐴3′𝐴2′𝐴1𝐴0Y6=A3′A2′A1A0 𝑌5=𝐴3′𝐴2𝐴1′𝐴0′Y5=A3′A2A1′A0′ 𝑌4=𝐴3′𝐴2𝐴1′𝐴0Y4=A3′A2A1′A0 𝑌3=𝐴3′𝐴2𝐴1𝐴0′Y3=A3′A2A1A0′ 𝑌2=𝐴3′𝐴2𝐴1𝐴0Y2=A3′A2A1A0 𝑌1=𝐴3𝐴2′𝐴1′𝐴0′Y1=A3A2′A1′A0′ 𝑌0=𝐴3𝐴2′𝐴1′𝐴0Y0=A3A2′A1′A0

表4.4.6 二-十进制译码器74HC42的真值表

| 序号 | 输入 𝐴3A3 | 输入 𝐴2A2 | 输入 𝐴1A1 | 输入 𝐴0A0 | 输出 𝑌9Y9 | 输出 𝑌8Y8 | 输出 𝑌7Y7 | 输出 𝑌6Y6 | 输出 𝑌5Y5 | 输出 𝑌4Y4 | 输出 𝑌3Y3 | 输出 𝑌2Y2 | 输出 𝑌1Y1 | 输出 𝑌0Y0 |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 |

| 1 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 |

| 2 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 |

| 3 | 0 | 0 | 1 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 |

| 4 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 |

| 5 | 0 | 1 | 0 | 1 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 |

| 6 | 0 | 1 | 1 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 |

| 7 | 0 | 1 | 1 | 1 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| 8 | 1 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| 9 | 1 | 0 | 0 | 1 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

对于BCD代码以外的伪码(即1010-1111这6个代码), 𝑌0∼𝑌9Y0∼Y9 均无低电平信号产生,译码器拒绝“翻译”,所以这个电路结构具有拒绝伪码的功能。

三、显示译码器

- 七段字符显示器

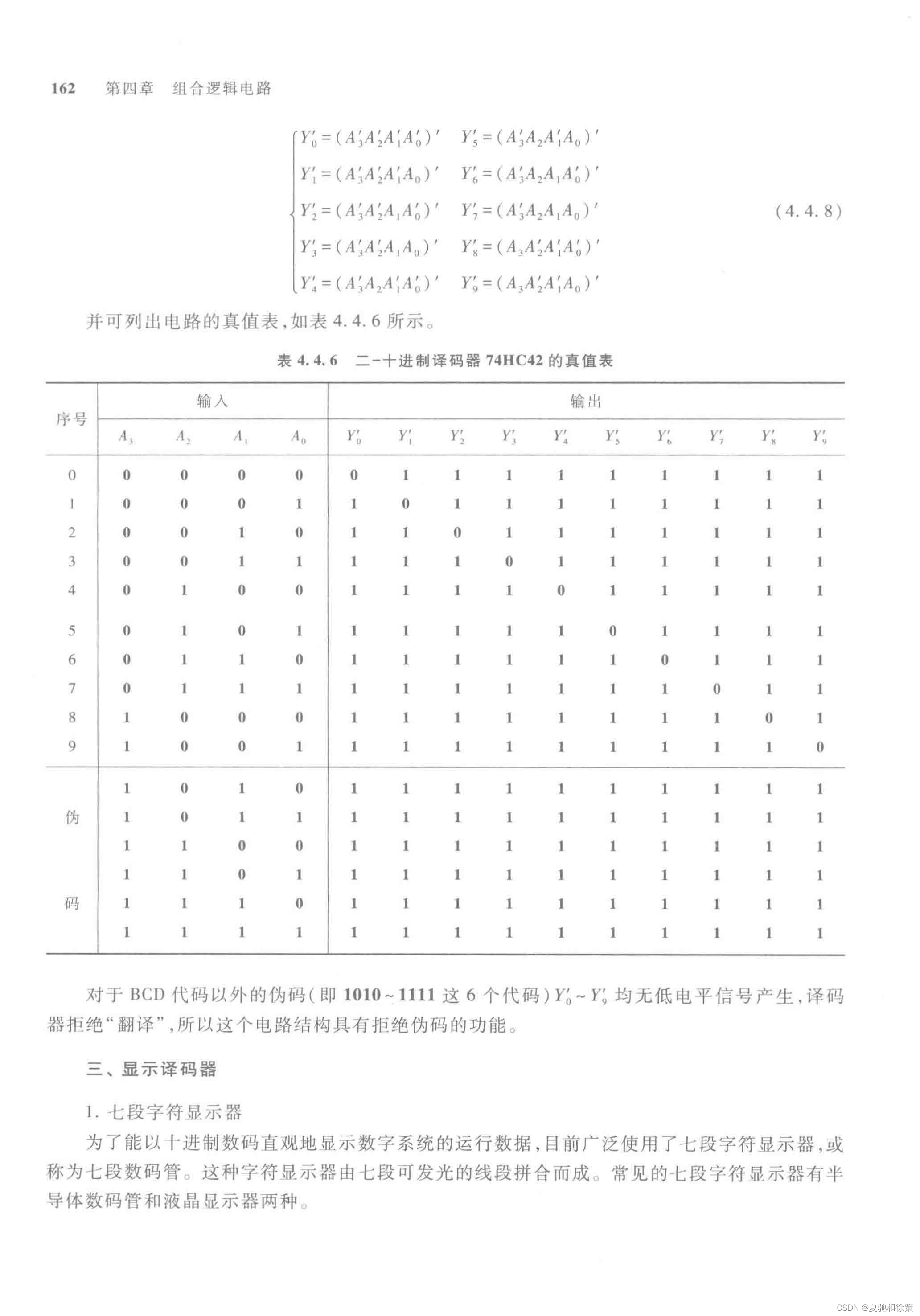

为了能以十进制数码直观地显示数字系统的运行数据,目前广泛使用了七段字符显示器,或称为七段数码管。这种字符显示器由七段可发光的线段拼合而成。常见的七段字符显示器有半导体数码管和液晶显示器两种。

图4.4.10是半导体数码管BS201A的外形图和等效电路。这种数码管的每个线段都是一个发光二极管(Light Emitting Diode,简称LED),因而也将它称为LED数码管或LED七段显示器。

发光二极管使用的材料与普通的硅二极管和锗二极管不同,有磷砷化镓、磷化镓、砷化镓等几种,而且半导体中的杂质浓度很高。当外加正向电压时,大量的电子和空穴在扩散过程中复合,其中一部分电子从导带跃迁到价带,把多余的能量以光的形式释放出来,便发出一定波长的可见光。

磷砷化镓发光二极管发出光线的波长与磷和砷的比例有关,含磷的比例越大波长越短,同时发光效率也随之降低。目前生产的磷砷化镓发光二极管(如BS201,BS211等)发出光线的波长在6500Å左右,呈橙红色。

在BS201等一些数码管中还在右下角处增设了一个小数点,形成了所谓八段数码管,如图4.4.10(a)所示。此外,由图4.4.10(b)的等效电路可见,BS201A的八段发光二极管的阴极是做在一起的,属于共阴极类型。为了增加使用的灵活性,同一规格的数码管一般都有共阴极和共阳极两种类型可供选用。

半导体数码管不仅具有工作电压低、体积小,寿命长、可靠性高等优点,而且响应时间短(一般不超过0.1 μs),亮度也比较高。它的缺点是工作电流较大,每一段的工作电流在10 mA左右。

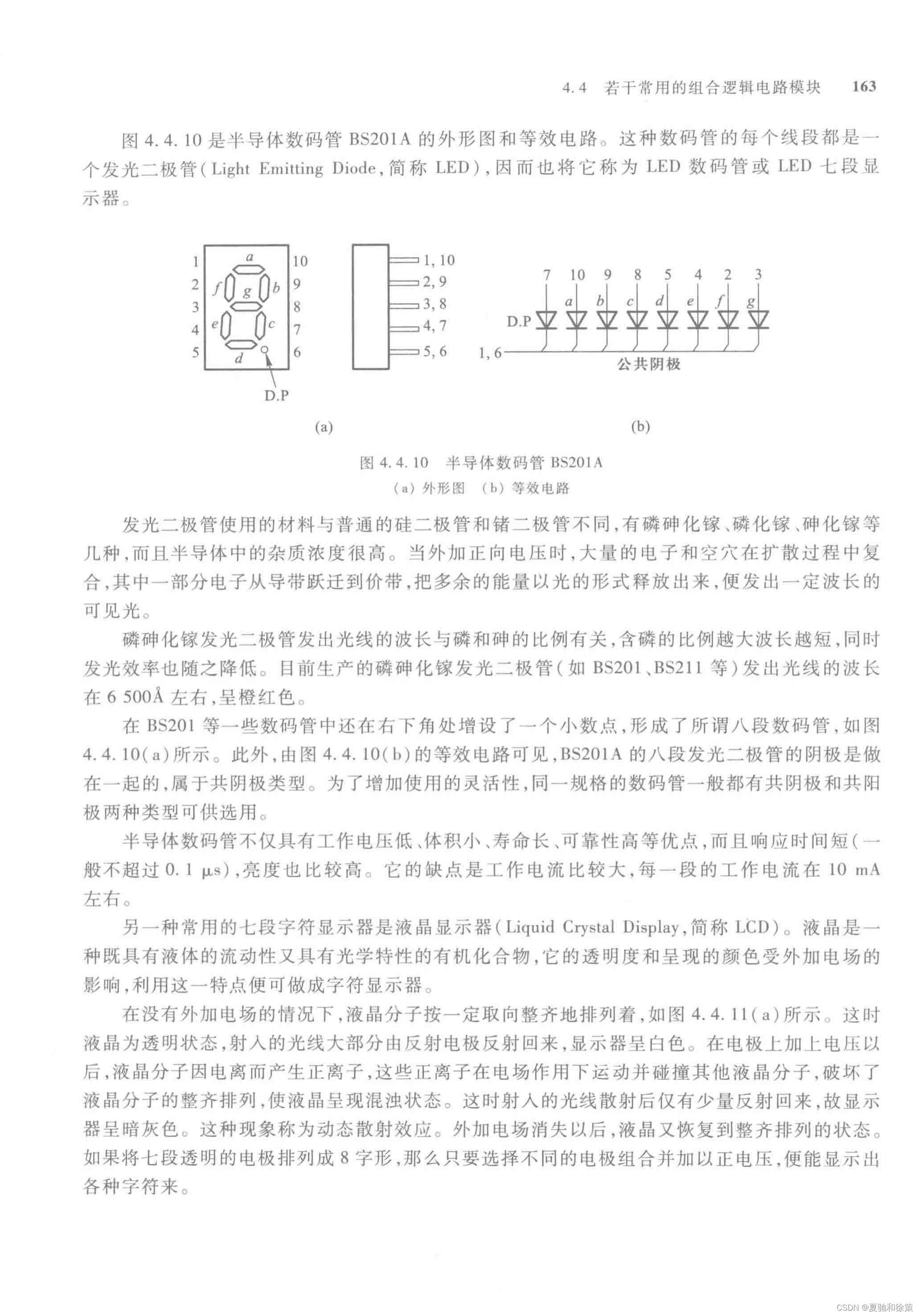

另一种常用的七段字符显示器是液晶显示器(Liquid Crystal Display,简称LCD)。液晶是一种既具有液体的流动性又具有光学特性的有机化合物,它的透明度和呈现的颜色受外加电场的影响,利用这一特点便可做成字符显示器。

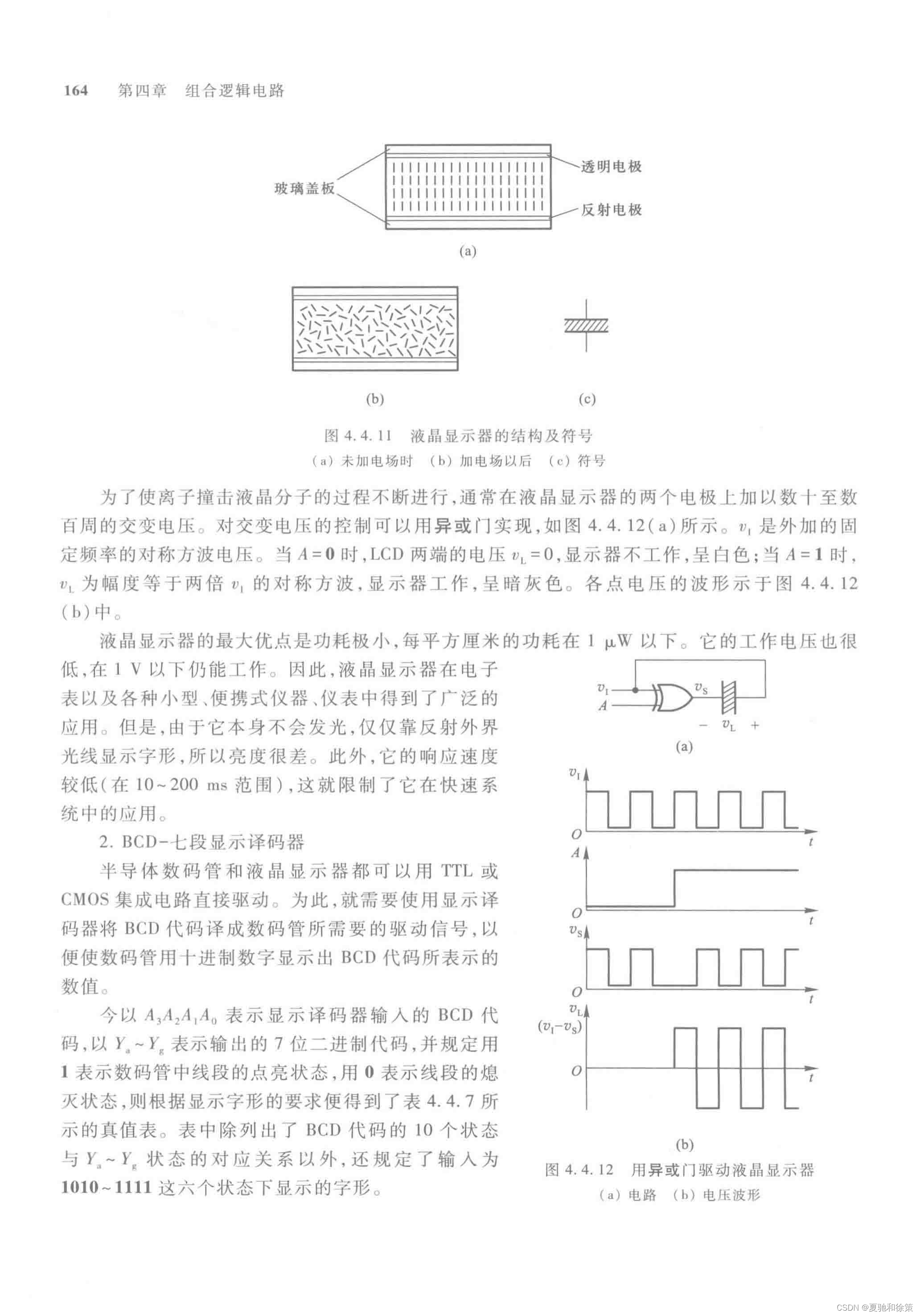

在没有外加电场的情况下,液晶分子按一定取向整齐地排列着,如图4.4.11(a)所示。这时液晶为透明状态,射入的光线大部分由反射电极反射回来,显示器呈白色。在电极上加上电压以后,液晶分子因电离而产生正离子,这些正离子在电场作用下运动并碰撞其他液晶分子,破坏了液晶分子的整齐排列,使液晶呈现混浊状态。这时射入的光线散射后仅有少量反射回来,显示器呈暗灰色。这种现象称为动态散射效应。外加电场消失以后,液晶又恢复到整齐排列的状态。如果将七段透明的电极排列成8字形,那么只要选择不同的电极组合并加以正电压,便能显示出各种字符来。

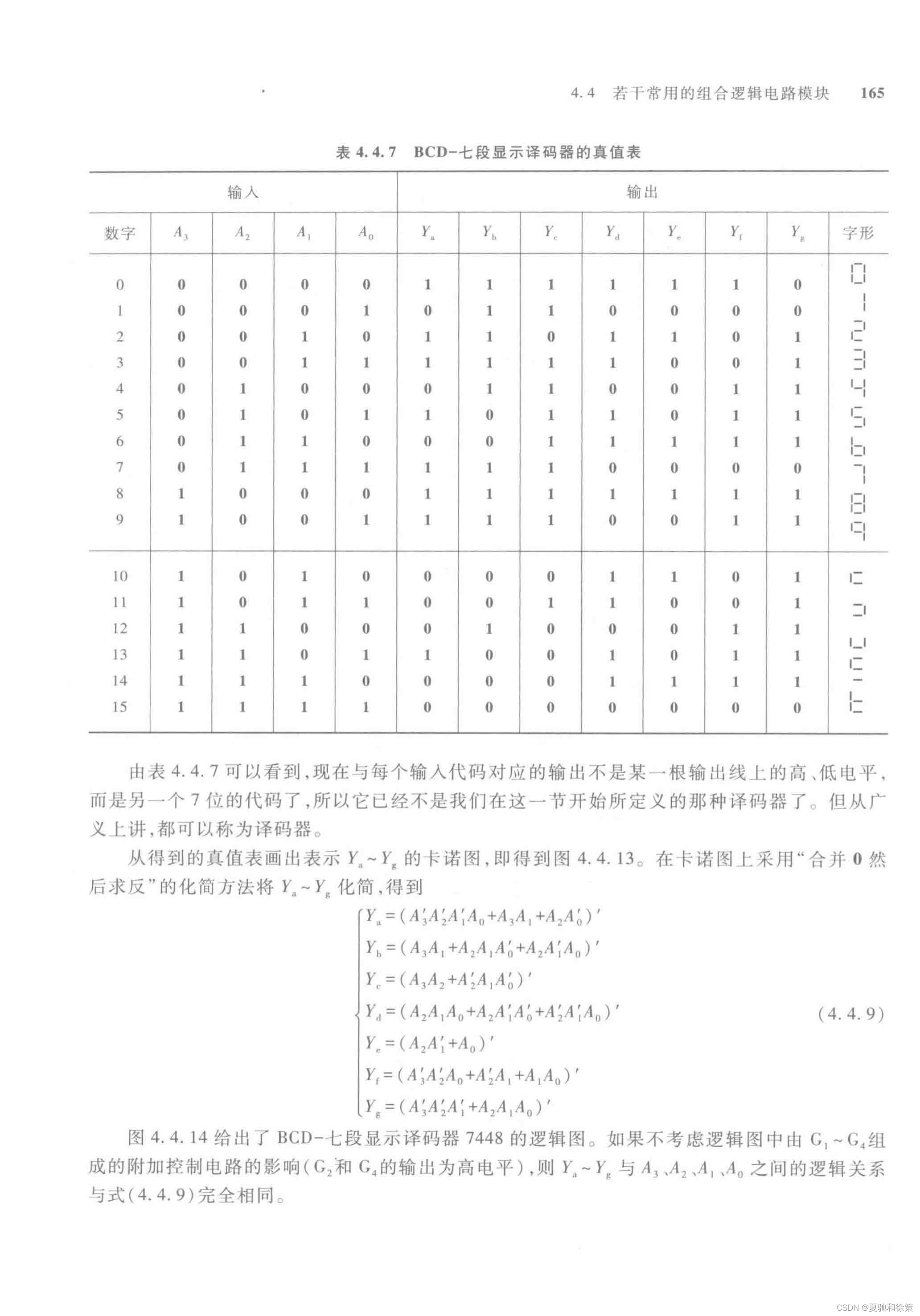

为了使离子撞击液晶分子的过程不断进行,通常在液晶显示器的两个电极上加以数十至数百周的交变电压。对交变电压的控制可以用异或门实现,如图4.4.12(a)所示。 𝑣𝑙vl 是外加的固定频率的对称方波电压。当 𝐴=0A=0 时,LCD两端的电压 𝑣𝑙=0vl=0,显示器不工作,呈白色;当 𝐴=1A=1 时,𝑣𝑙vl 为幅度等于两倍 𝑣𝑙vl 的对称方波,显示器工作,呈暗灰色。各点电压的波形如图4.4.12(b)所示。

液晶显示器的最大优点是功耗极小,每平方厘米的功耗在1 μW以下。它的工作电压也很低,在1 V以下仍能工作。因此,液晶显示器在电子表以及各种小型、便携式仪器、仪表中得到了广泛的应用。但是,由于它本身不会发光,仅仅靠反射外界光线显示字形,所以亮度很差。此外,它的响应速度较低(在10-200 ms范围),这就限制了它在快速系统中的应用。

- BCD-七段显示译码器

半导体数码管和液晶显示器都可以用TTL或CMOS集成电路直接驱动。为此,就需要使用显示译码器将BCD代码译成数码管所需要的驱动信号,以便使数码管用十进制数字显示出BCD代码所表示的数值。

今以 𝐴3,𝐴2,𝐴1,𝐴0A3,A2,A1,A0 表示显示译码器输入的BCD代码,以 𝑌0∼𝑌7Y0∼Y7 表示输出的7位二进制代码,并规定用1表示数码管中线段的点亮状态,用0表示线段的熄灭状态,则根据显示字形的要求便得到了表4.4.7所示的真值表。表中除列出了BCD代码的10个状态与 𝑌0∼𝑌7Y0∼Y7 状态的对应关系以外,还规定了输入为1010~1111这六个状态下显示的字形。

表4.4.7 BCD-七段显示译码器的真值表

| 输入 | 输出 | 数字 |

|---|---|---|

| 𝐴3,𝐴2,𝐴1,𝐴0A3,A2,A1,A0 | 𝑌0,𝑌1,𝑌2,𝑌3,𝑌4,𝑌5,𝑌6,𝑌7Y0,Y1,Y2,Y3,Y4,Y5,Y6,Y7 | |

| 0000 | 1111110 | 0 |

| 0001 | 0110000 | 1 |

| 0010 | 1101101 | 2 |

| 0011 | 1111001 | 3 |

| 0100 | 0110011 | 4 |

| 0101 | 1011011 | 5 |

| 0110 | 1011111 | 6 |

| 0111 | 1110000 | 7 |

| 1000 | 1111111 | 8 |

| 1001 | 1111011 | 9 |

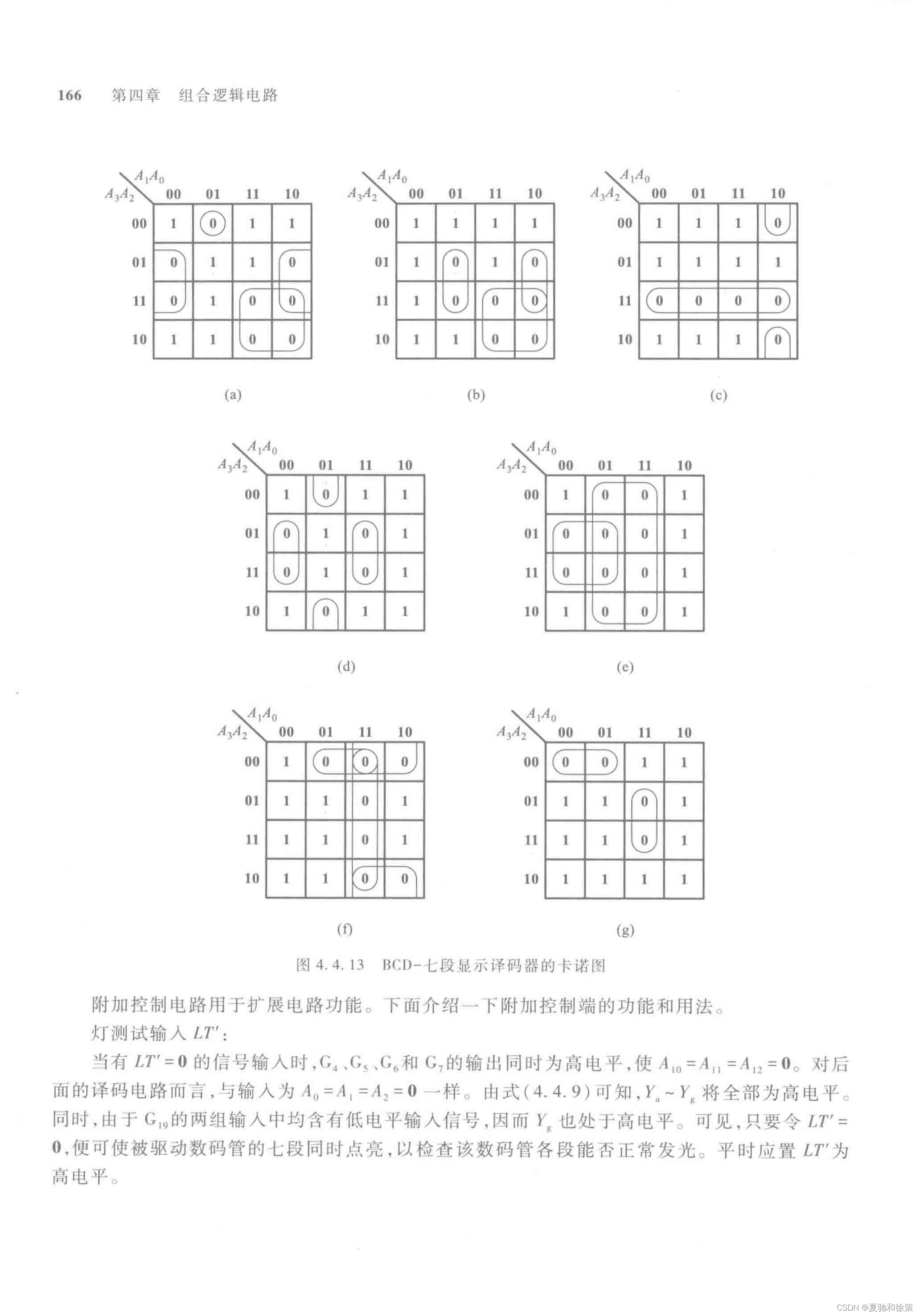

从得到的真值表画出表示 𝑌0∼𝑌7Y0∼Y7 的卡诺图,即得到图4.4.13。在卡诺图上采用“合并0然后求反”的化简方法将 𝑌0∼𝑌7Y0∼Y7 化简,得到:

𝑌0=𝐴3+𝐴1𝐴0+𝐴2𝐴1Y0=A3+A1A0+A2A1 𝑌1=𝐴2+𝐴3𝐴0+𝐴1𝐴0Y1=A2+A3A0+A1A0 𝑌2=𝐴2𝐴1+𝐴3𝐴1+𝐴1𝐴0Y2=A2A1+A3A1+A1A0

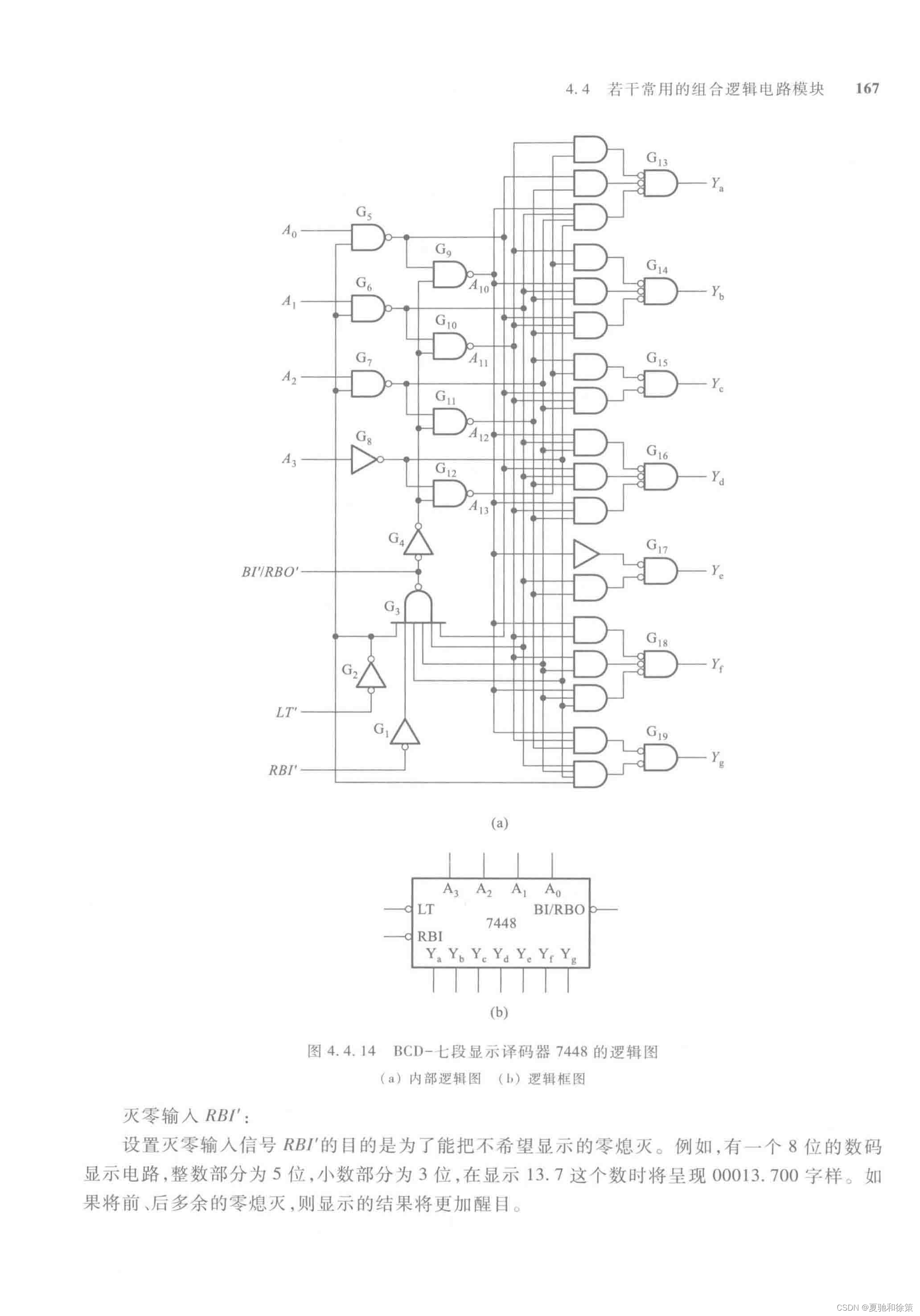

图4.4.14给出了BCD-七段显示译码器7448的逻辑图。如果不考虑逻辑图中由 𝐺1∼𝐺4G1∼G4 组成的附加控制电路的影响( 𝐺2G2 和 𝐺4G4 的输出为高电平),则 𝑌0∼𝑌7Y0∼Y7 与 𝐴3,𝐴2,𝐴1,𝐴0A3,A2,A1,A0 之间的逻辑关系与式(4.4.9)完全相同。

附加控制电路功能

- 灯测试输入 𝐿𝑇LT

当有 𝐿𝑇′=0LT′=0 的信号输入时,𝐺2,𝐺3,𝐺4G2,G3,G4 和 𝐺1G1 的输出同时为高电平,使 𝐴3=𝐴2=𝐴1=𝐴0=0A3=A2=A1=A0=0。对后面的译码电路而言,与输入为 𝐴3=𝐴2=𝐴1=𝐴0=0A3=A2=A1=A0=0 一样。由式(4.4.9)可知,𝑌0∼𝑌7Y0∼Y7 将全部为高电平。同时,由于 𝐺1G1 的两组输入中均含有低电平输入信号,因而 𝑌0Y0 也处于高电平。可见,只要令 𝐿𝑇′=0LT′=0,便可使被驱动数码管的七段同时点亮,以检查该数码管各段能否正常发光。平时应置 𝐿𝑇LT 为高电平。

- 灭零输入 𝑅𝐵𝐼′RBI′

设置灭零输入信号 𝑅𝐵𝐼′RBI′ 的目的是为了能把不希望显示的零熄灭。例如,有一个8位的数码显示电路,整数部分为5位,小数部分为3位,在显示13.7这个数时将呈现00013.700字样。如果将前、后多余的零熄灭,则显示的结果将更加醒目。

图4.4.14可知,当输入 𝐴3=𝐴2=𝐴1=𝐴0=0A3=A2=A1=A0=0 时,本应显示出0。如果需要将这个零熄灭,则可加入 𝑅𝐵𝐼′=0RBI′=0 的输入信号。这时 𝐺3G3 的输出为低电平,并经过 𝐺4G4 输出低电平使 𝐴3=𝐴2=𝐴1=𝐴0=1A3=A2=A1=A0=1。由于 𝐺4∼𝐺7G4∼G7 每个与或非门都有一组输入全为高电平,所以 𝑌0∼𝑌7Y0∼Y7 全为低电平,使本来应该显示的0熄灭。

- 灭灯输入/灭零输出 𝐵𝐼/𝑅𝐵𝑂′BI/RBO′

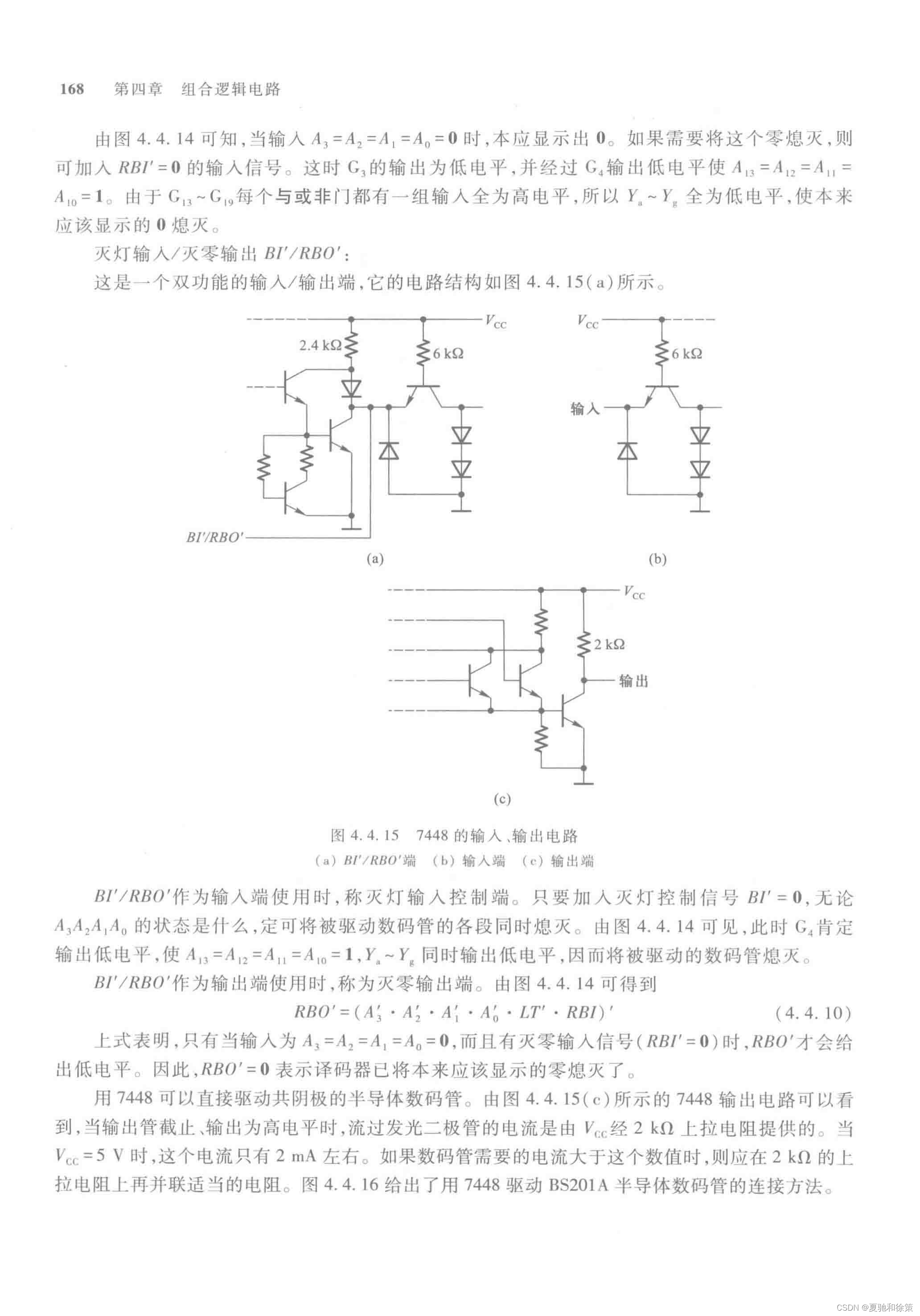

这是一个双功能的输入/输出端,它的电路结构如图4.4.15(a)所示。

𝐵𝐼/𝑅𝐵𝑂′BI/RBO′ 作为输入端使用时,称灭灯输入控制端。只要加入灭灯控制信号 𝐵𝐼′=0BI′=0,无论 𝐴3,𝐴2,𝐴1,𝐴0A3,A2,A1,A0 的状态是什么,定可将被驱动数码管的各段同时熄灭。由图4.4.14可见,此时 𝐺4G4 肯定输出低电平,使 𝐴3=𝐴2=𝐴1=𝐴0=1A3=A2=A1=A0=1,𝑌0∼𝑌7Y0∼Y7 同时输出低电平,因而将被驱动的数码管熄灭。

𝐵𝐼/𝑅𝐵𝑂′BI/RBO′ 作为输出端使用时,称为灭零输出端。由图4.4.14可得到:

𝑅𝐵𝑂′=(𝐴3′𝐴2′𝐴1′𝐴0′𝐿𝑇′𝑅𝐵𝐼′)RBO′=(A3′A2′A1′A0′LT′RBI′)

上式表明,只有当输入为 𝐴3=𝐴2=𝐴1=𝐴0=0A3=A2=A1=A0=0,而且有灭零输入信号( 𝑅𝐵𝐼′=0RBI′=0)时,𝑅𝐵𝑂′RBO′ 才会给出低电平。因此,𝑅𝐵𝑂′=0RBO′=0 表示译码器已将本来应该显示的零熄灭了。

用7448可以直接驱动共阴极的半导体数码管。由图4.4.15(c)所示的7448输出电路可以看到,当输出管截止、输出为高电平时,流过发光二极管的电流是由 𝑉𝐶𝐶VCC 经2kΩ上拉电阻提供的。当 𝑉𝐶𝐶=5𝑉VCC=5V 时,这个电流只有2mA左右。如果数码管需要的电流大于这个数值时,则应在2 kΩ的上拉电阻上再并联适当的电阻。

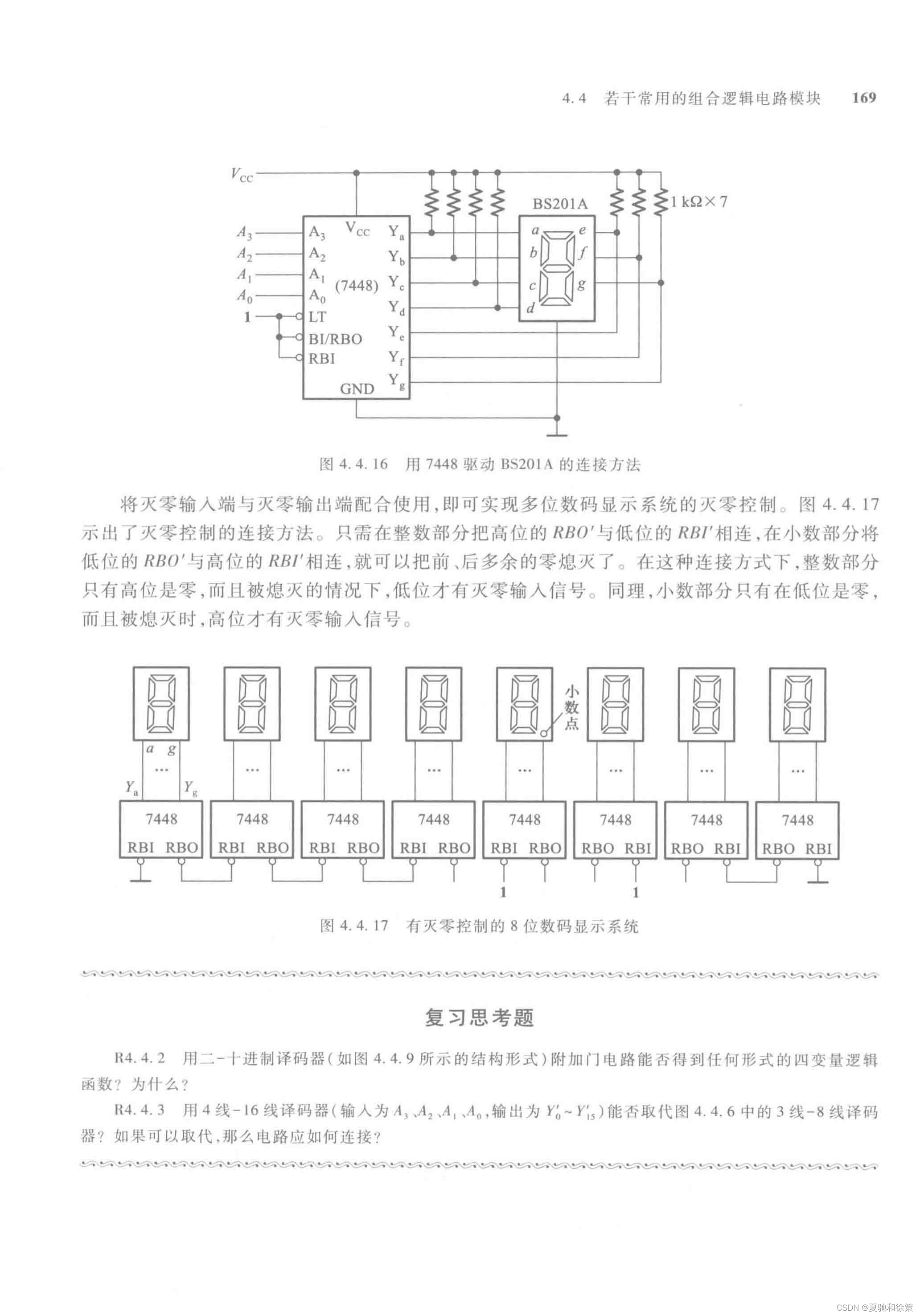

将灭零输入端与灭零输出端配合使用,即可实现多位数码显示系统的灭零控制。图4.4.17示出了灭零控制的连接方法。只需在整数部分把高位的 𝑅𝐵𝑂′RBO′ 与低位的 𝑅𝐵𝐼′RBI′ 相连,在小数部分将低位的 𝑅𝐵𝑂′RBO′ 与高位的 𝑅𝐵𝐼′RBI′ 相连,就可以把前、后多余的零熄灭了。在这种连接方式下,整数部分只有高位是零,而且被熄灭的情况下,低位才有灭零输入信号。同理,小数部分只有在低位是零,而且被熄灭时,高位才有灭零输入信号。

4.4.3 数据选择器

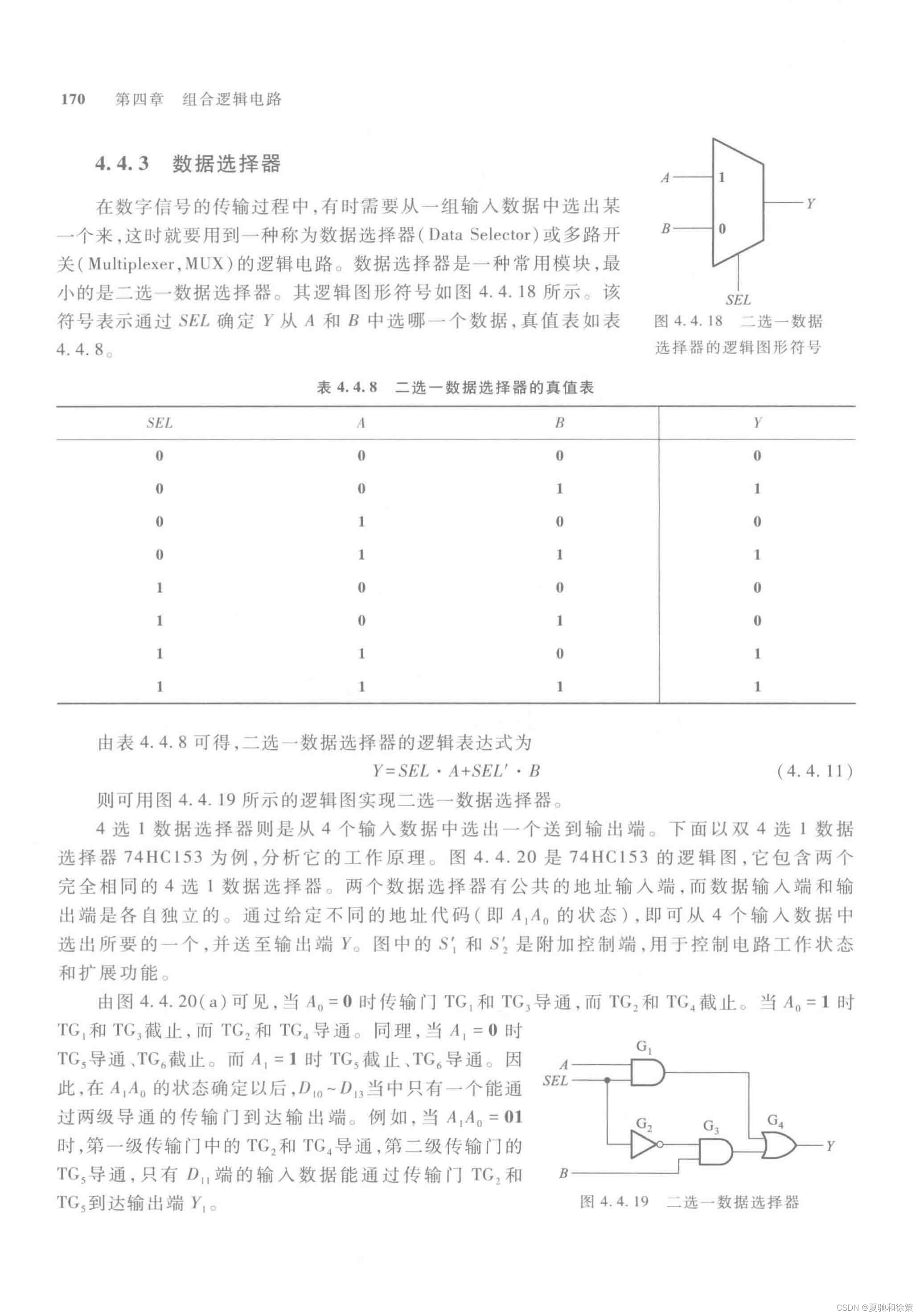

在数字信号的传输过程中,有时需要从一组输入数据中选出某一个来,这时就要用到一种称为数据选择器(Data Selector)或多路开关(Multiplexer, MUX)的逻辑电路。数据选择器是一种常用模块,最小的是二选一数据选择器。

二选一数据选择器

二选一数据选择器的逻辑图形符号如图4.4.18所示。该符号表示通过SEL确定Y从A和B中选哪一个数据,真值表如表4.4.8。

表4.4.8 二选一数据选择器的真值表:

| SEL | A | B | Y |

|---|---|---|---|

| 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 1 |

| 0 | 1 | 0 | 0 |

| 0 | 1 | 1 | 1 |

| 1 | 0 | 0 | 0 |

| 1 | 0 | 1 | 0 |

| 1 | 1 | 0 | 1 |

| 1 | 1 | 1 | 1 |

由表4.4.8可得,二选一数据选择器的逻辑表达式为: 𝑌=𝑆𝐸𝐿⋅𝐴+𝑆𝐸𝐿‾⋅𝐵Y=SEL⋅A+SEL⋅B (4.4.11)

该逻辑表达式可以通过图4.4.19所示的逻辑图实现二选一数据选择器。

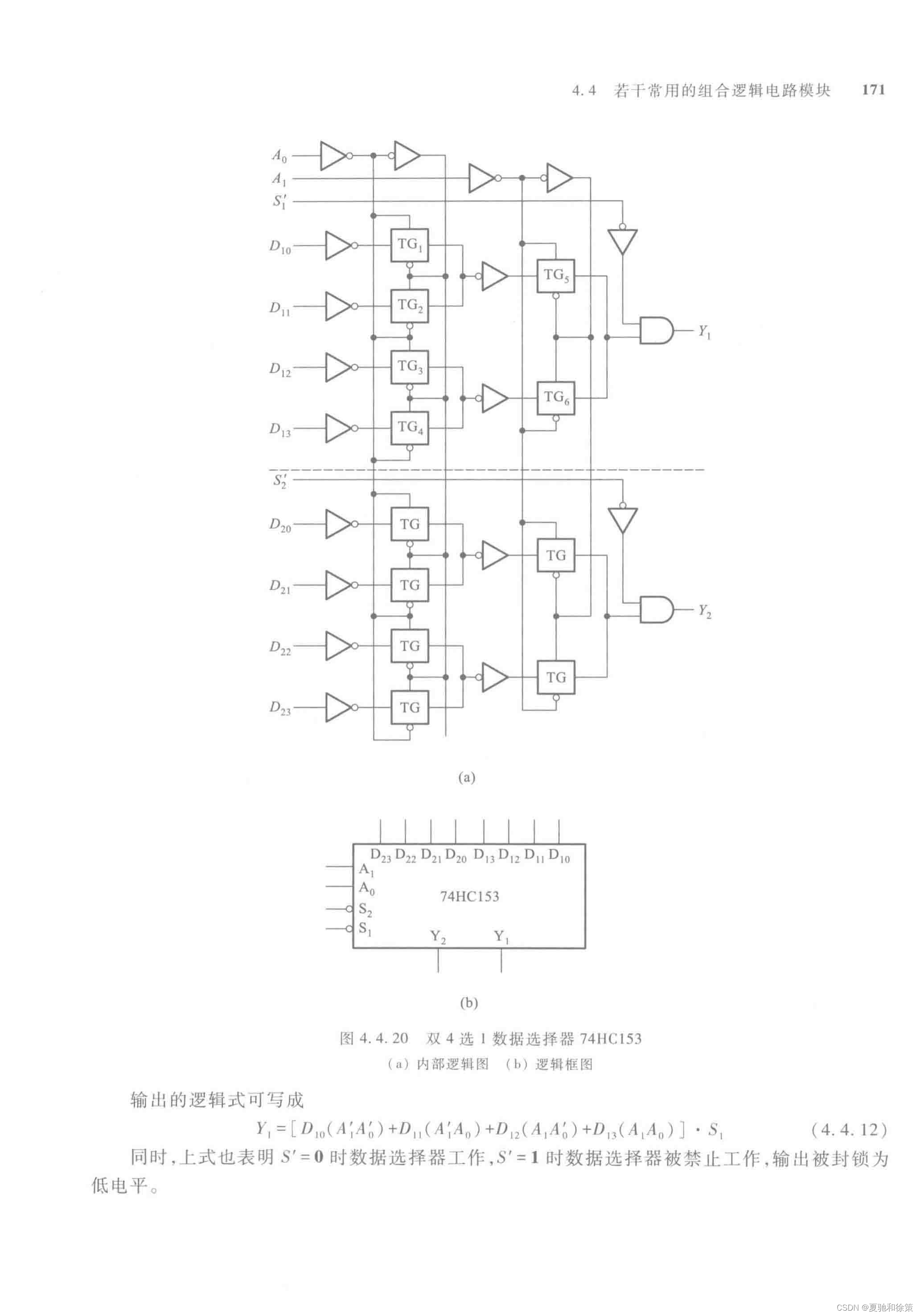

四选一数据选择器

四选一数据选择器则是从4个输入数据中选出一个送到输出端。下面以双四选一数据选择器74HC153为例,分析它的工作原理。图4.4.20是74HC153的逻辑图,它包含两个完全相同的四选一数据选择器。两个数据选择器有公共的地址输入端,而数据输入端和输出端是各自独立的。通过给定不同的地址代码(即 𝐴1A1 和 𝐴0A0 的状态),即可从4个输入数据中选出所要的一个,并送至输出端 𝑌Y。图中的 𝑆1S1 和 𝑆2S2 是附加控制端,用于控制电路工作状态和扩展功能。

由图4.4.20(a)可见,当 𝐴0=0A0=0 时,传输门 𝑇𝐺1TG1 和 𝑇𝐺5TG5 导通,而 𝑇𝐺2TG2 和 𝑇𝐺6TG6 截止。当 𝐴0=1A0=1 时,𝑇𝐺3TG3 和 𝑇𝐺7TG7 导通,而 𝑇𝐺4TG4 和 𝑇𝐺8TG8 截止。同理,当 𝐴1=0A1=0 时,𝑇𝐺9TG9 和 𝑇𝐺10TG10 导通,𝑇𝐺11TG11 和 𝑇𝐺12TG12 截止;而 𝐴1=1A1=1 时,𝑇𝐺13TG13 和 𝑇𝐺14TG14 导通,𝑇𝐺15TG15 和 𝑇𝐺16TG16 截止。因此,在 𝐴1A1 和 𝐴0A0 的状态确定以后,𝐷0∼𝐷3D0∼D3 当中只有一个能通过两级导通的传输门到达输出端。

例如,当 𝐴1=0A1=0 和 𝐴0=1A0=1 时,第一级传输门中的 𝑇𝐺2TG2 和 𝑇𝐺6TG6 导通,第二级传输门的 𝑇𝐺6TG6 导通,只有 𝐷1D1 端的输入数据能通过传输门 𝑇𝐺2TG2 和 𝑇𝐺6TG6 到达输出端 𝑌1Y1。

输出的逻辑式可写成: 𝑌1=[𝐷0⋅(𝐴1‾⋅𝐴0‾)+𝐷1⋅(𝐴1‾⋅𝐴0)+𝐷2⋅(𝐴1⋅𝐴0‾)+𝐷3⋅(𝐴1⋅𝐴0)]⋅𝑆1‾Y1=[D0⋅(A1⋅A0)+D1⋅(A1⋅A0)+D2⋅(A1⋅A0)+D3⋅(A1⋅A0)]⋅S1 (4.4.12)

同时,上式也表明 𝑆1′=0S1′=0 时数据选择器工作,𝑆1′=1S1′=1 时数据选择器被禁止工作,输出被封锁为低电平。

4.4.4 加法器

两个二进制数之间的算术运算无论是加、减、乘、除,目前在数字计算机中都是化做若干步加法运算进行的。因此,加法器是构成算术运算器的基本单元。

一、1位加法器

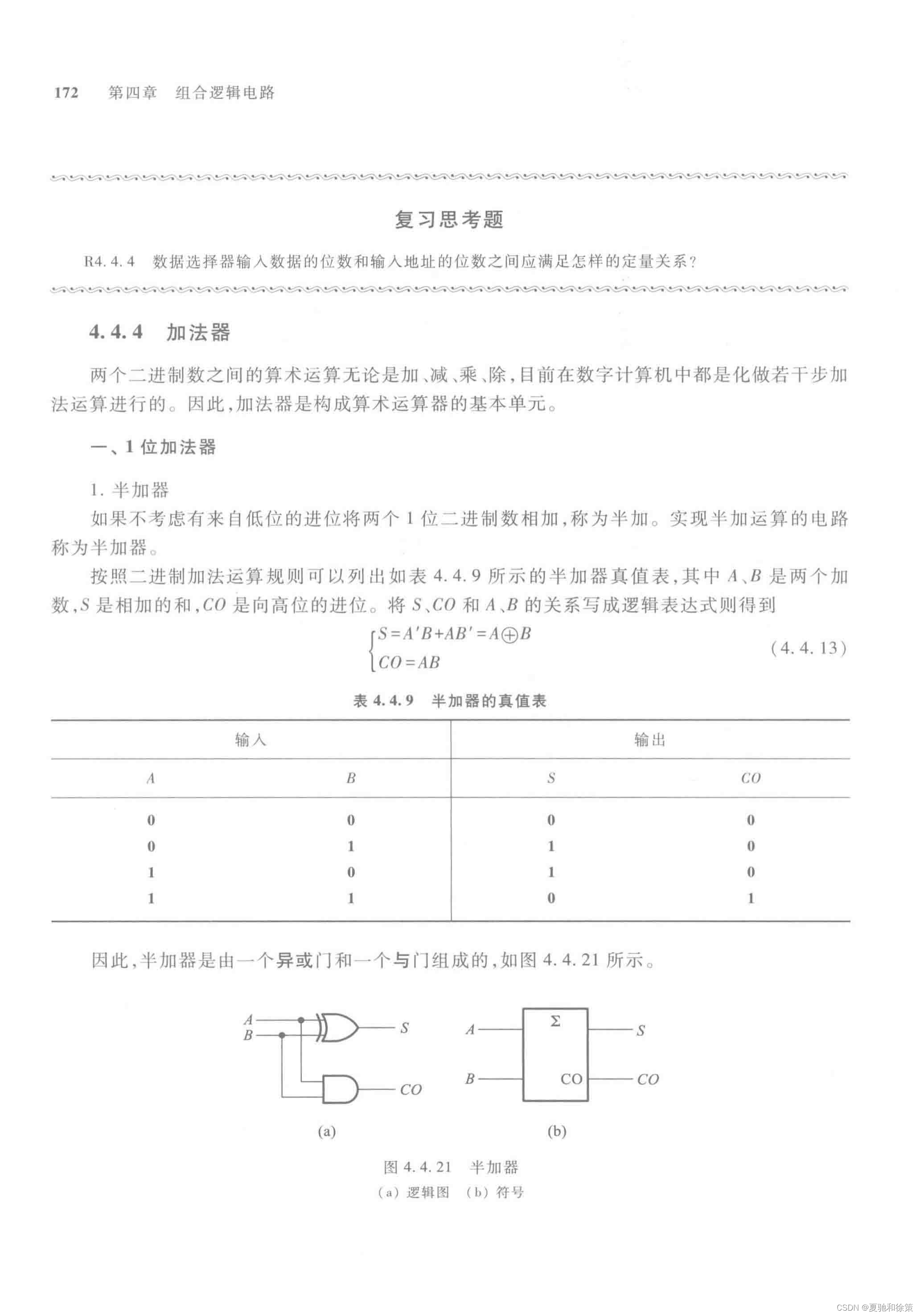

1. 半加器

如果不考虑有来自低位的进位将两个1位二进制数相加,称为半加。实现半加运算的电路称为半加器。

按照二进制加法运算规则可以列出如表4.4.9所示的半加器真值表,其中A、B是两个加数,S是相加的和,C0是向高位的进位。将S、C0和A、B的关系写成逻辑表达式则得到: 𝑆=𝐴⊕𝐵S=A⊕B 𝐶0=𝐴⋅𝐵C0=A⋅B (4.4.13)

表4.4.9 半加器的真值表:

| 输入 | 输出 |

|---|---|

| A | B |

| 0 | 0 |

| 0 | 1 |

| 1 | 0 |

| 1 | 1 |

因此,半加器是由一个异或门和一个与门组成的,如图4.4.21所示。

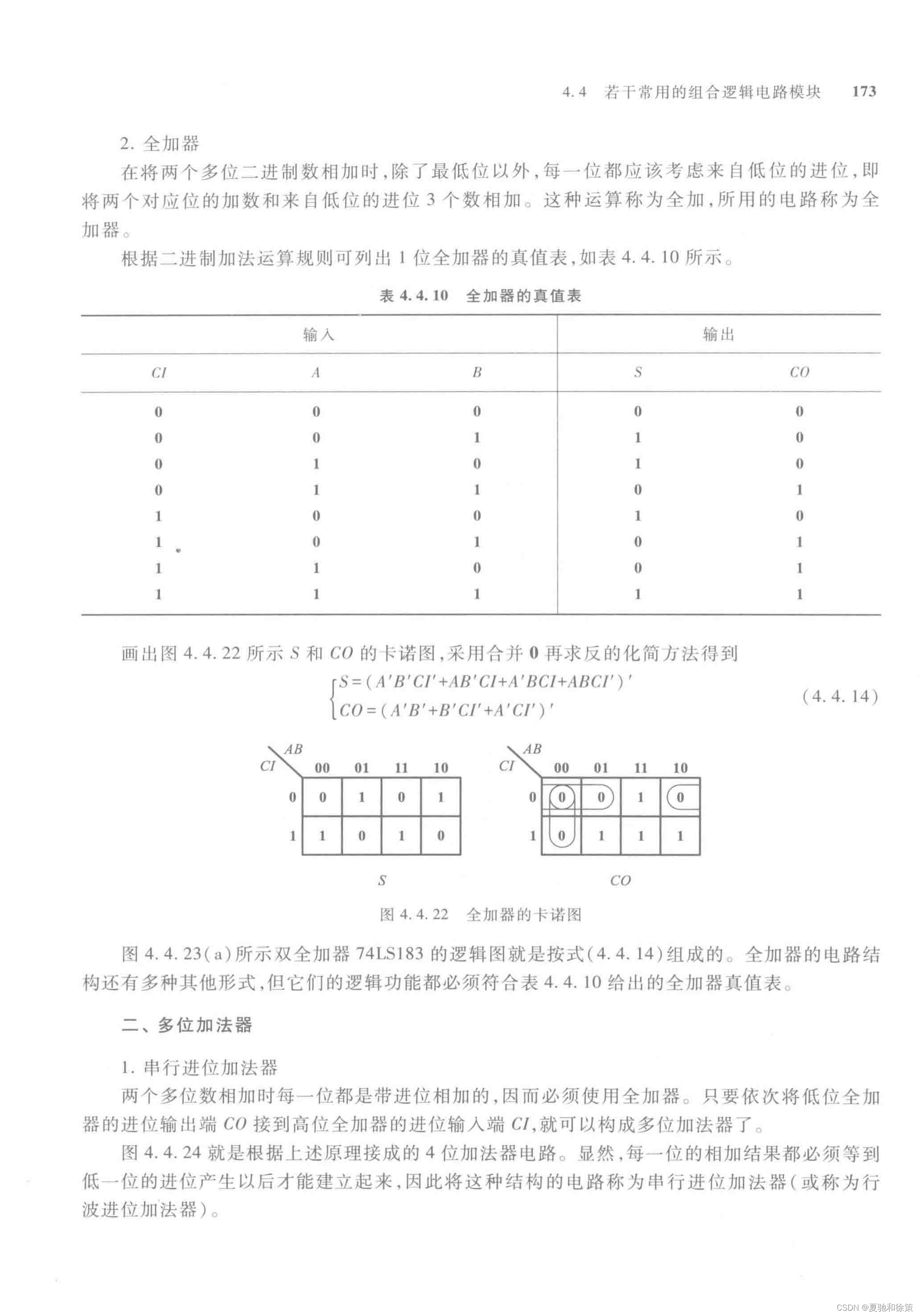

2. 全加器

在将两个多位二进制数相加时,除了最低位以外,每一位都应该考虑来自低位的进位,即将两个对应位的加数和来自低位的进位三个数相加。这种运算称为全加,所用的电路称为全加器。

根据二进制加法运算规则可列出1位全加器的真值表,如表4.4.10所示。

表4.4.10 全加器的真值表:

| A | B | CI | S | CO |

|---|---|---|---|---|

| 0 | 0 | 0 | 0 | 0 |

| 0 | 1 | 0 | 1 | 0 |

| 1 | 0 | 0 | 1 | 0 |

| 1 | 1 | 0 | 0 | 1 |

| 0 | 0 | 1 | 1 | 0 |

| 0 | 1 | 1 | 0 | 1 |

| 1 | 0 | 1 | 0 | 1 |

| 1 | 1 | 1 | 1 | 1 |

画出图4.4.22所示S和C0的卡诺图,采用合并0再求反的化简方法得到: 𝑆=(𝐴⊕𝐵)⊕𝐶𝐼S=(A⊕B)⊕CI 𝐶𝑂=𝐴𝐵+(𝐴⊕𝐵)𝐶𝐼CO=AB+(A⊕B)CI (4.4.14)

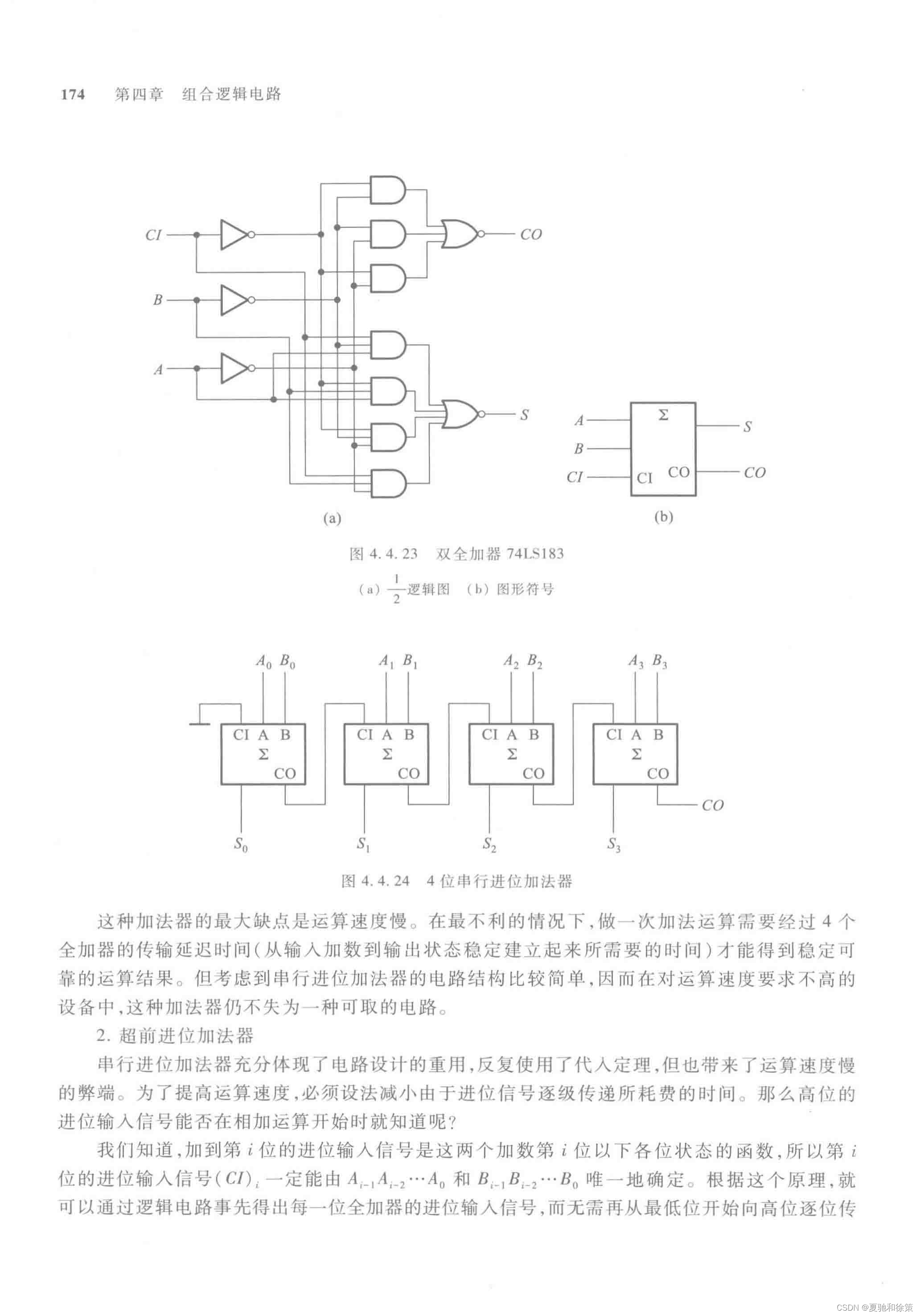

图4.4.23(a)所示双全加器74LS183的逻辑图就是按式(4.4.14)组成的。全加器的电路结构还有多种其他形式,但它们的逻辑功能都必须符合表4.4.10给出的全加器真值表。

二、多位加法器

1. 串行进位加法器

两个多位数相加时每一位都是带进位相加的,因而必须使用全加器。只要依次将低位全加器的进位输出端C0接到高位全加器的进位输入端CI,就可以构成多位加法器了。

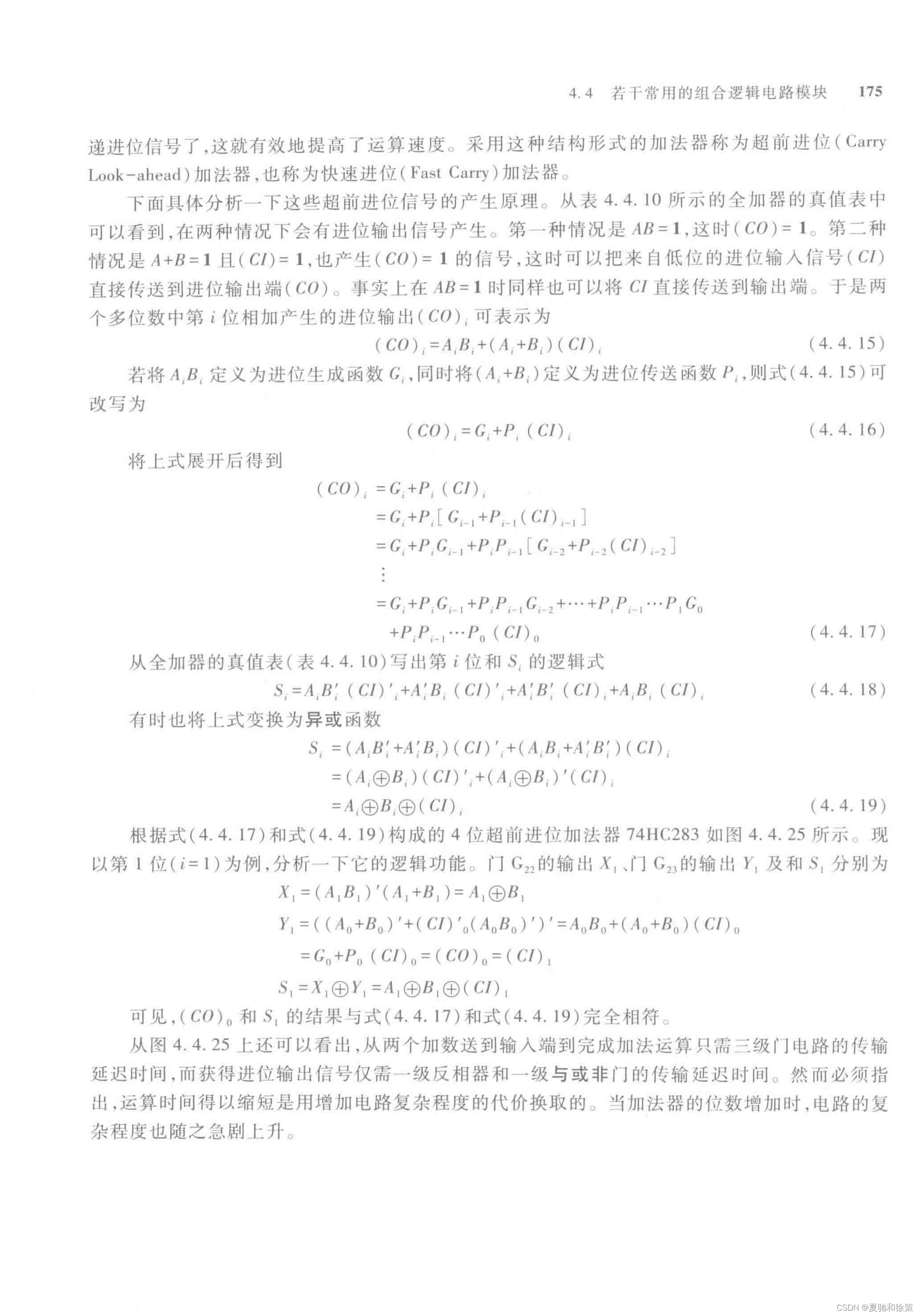

图4.4.24就是根据上述原理接成的4位加法器电路。显然,每一位的相加结果都必须等到低一位的进位产生以后才能建立起来,因此将这种结构的电路称为串行进位加法器(或称为行波进位加法器)。

这种加法器的最大缺点是运算速度慢。在最不利的情况下,做一次加法运算需要经过4个全加器的传输延迟时间(从输入加数到输出状态稳定建立起来所需要的时间)才能得到稳定可靠的运算结果。但考虑到串行进位加法器的电路结构比较简单,因而在对运算速度要求不高的设备中,这种加法器仍不失为一种可取的电路。

2. 超前进位加法器

串行进位加法器充分体现了电路设计的重用,反复使用了代入定理,但也带来了运算速度慢的弊端。为了提高运算速度,必须设法减小由于进位信号逐级传递所耗费的时间。那么高位的进位输入信号能否在相加运算开始时就知道呢?

我们知道,加到第1位的进位输入信号是这两个加数第4位以下各位状态的函数,所以第1位的进位输入信号(C0)一定能由A0-A3和B0-B3唯一地确定。根据这个原理,就可以通过逻辑电路事先得出每一位全加器的进位输入信号,而无需再从最低位开始向高位传递进位信号了,这就有效地提高了运算速度。采用这种结构形式的加法器称为超前进位(Carry Look-ahead)加法器,也称为快速进位(Fast Carry)加法器。

下面具体分析一下这些超前进位信号的产生原理。从表4.4.10所示的全加器的真值表中可以看到,在两种情况下会有进位输出信号产生。第一种情况是AB=1,这时CO=1。第二种情况是A+B=1且CI=1也产生CO=1的信号,这时可以把来自低位的进位输入信号CI直接传送到进位输出端CO。事实上在A+B=1时同样也可以将CI直接传送到输出端。于是两个多位数中第i位相加产生的进位输出CO可表示为: 𝐶𝑂𝑖=𝐴𝑖𝐵𝑖+(𝐴𝑖+𝐵𝑖)𝐶𝐼COi=AiBi+(Ai+Bi)CI (4.4.15)

若将A_i B_i定义为进位生成函数G,同时将(A_i + B_i)定义为进位传送函数P,则式(4.4.15)可改写为: 𝐶𝑂𝑖=𝐺𝑖+𝑃𝑖𝐶𝐼COi=Gi+PiCI (4.4.16)

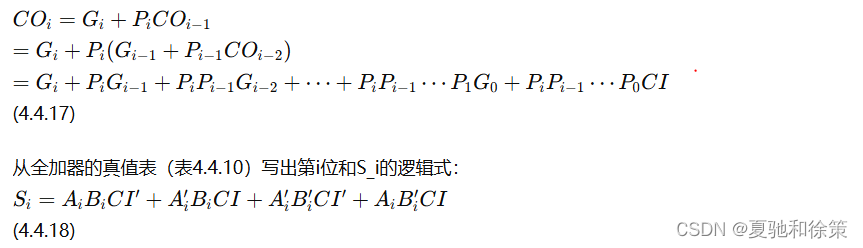

将上式展开后得到:

从全加器的真值表(表4.4.10)写出第i位和S_i的逻辑式: 𝑆𝑖=𝐴𝑖𝐵𝑖𝐶𝐼′+𝐴𝑖′𝐵𝑖𝐶𝐼+𝐴𝑖′𝐵𝑖′𝐶𝐼′+𝐴𝑖𝐵𝑖′𝐶𝐼Si=AiBiCI′+Ai′BiCI+Ai′Bi′CI′+AiBi′CI (4.4.18)

有时也将上式变换为异或函数: 𝑆𝑖=(𝐴𝑖⊕𝐵𝑖)⊕𝐶𝐼Si=(Ai⊕Bi)⊕CI (4.4.19)

根据式(4.4.17)和式(4.4.19)构成的4位超前进位加法器74HC283如图4.4.25所示。

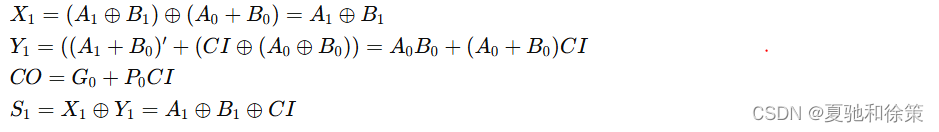

现以第1位(i=1)为例,分析一下它的逻辑功能。门G25的输出X1、门G22的输出Y1及和S1分别为:

可见,CO和S1的结果与式(4.4.17)和式(4.4.19)完全相符。

从图4.4.25上还可以看出,从两个加数送到输入端到完成加法运算只需三级门电路的传输延迟时间,而获得进位输出信号仅需一级反相器和一级与或非门的传输延迟时间。然而必须指出,运算时间得以缩短是用增加电路复杂程度的代价换取的。当加法器的位数增加时,电路的复杂程度也随之急剧上升。

4.4.5 数值比较器

在一些数字系统(例如数字计算机)当中经常要求比较两个数值的大小。为完成这一功能所设计的各种逻辑电路统称为数值比较器。

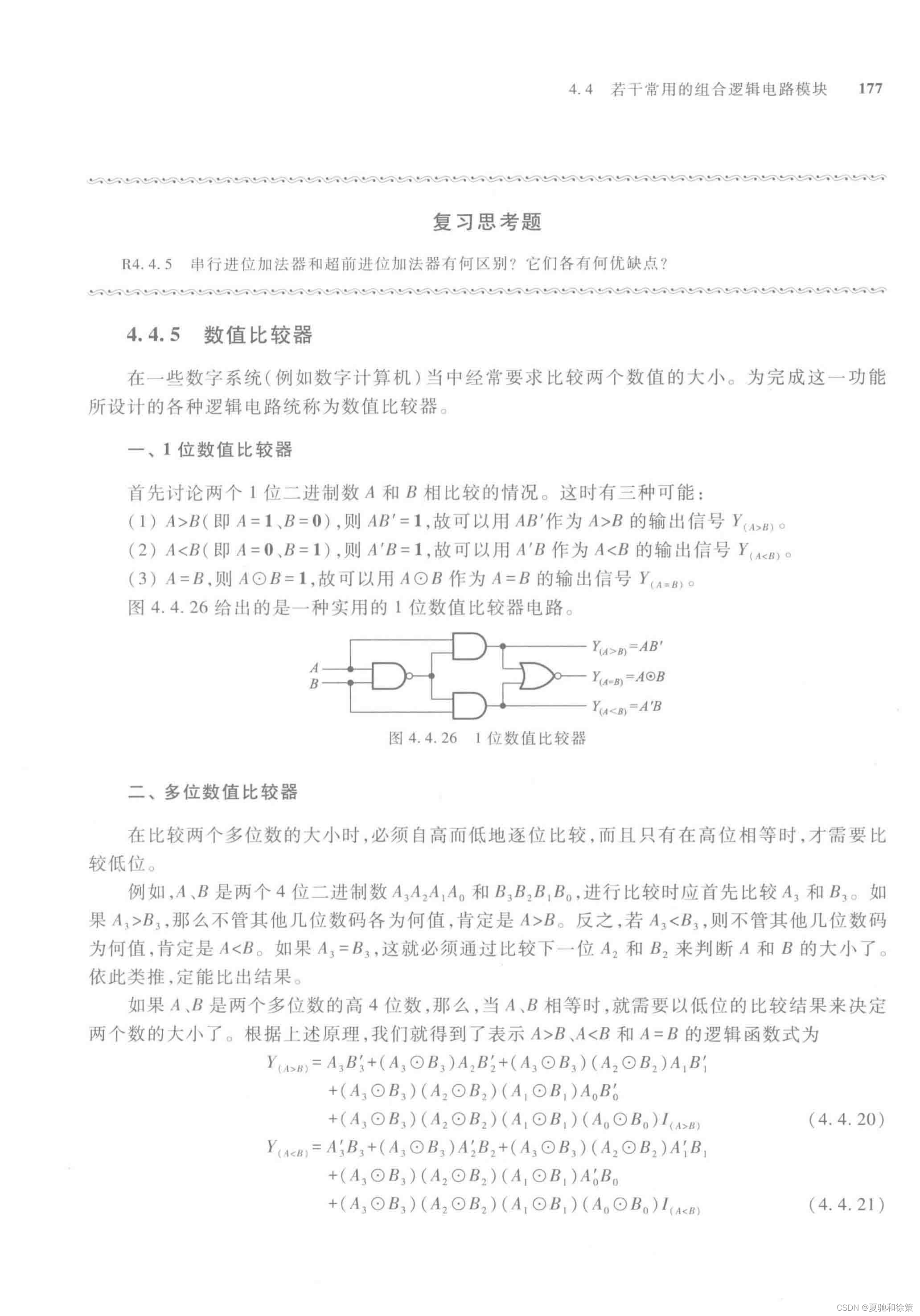

一、1位数值比较器

首先讨论两个1位二进制数A和B相比较的情况。这时有三种可能:

- A > B(即A=1,B=0),则AB'=1,故可以用AB'作为A>B的输出信号 𝑌(𝐴>𝐵)Y(A>B)。

- A < B(即A=0,B=1),则A'B=1,故可以用A'B作为A<B的输出信号 𝑌(𝐴<𝐵)Y(A<B)。

- A = B,则A'B' + AB = 1,故可以用A'B' + AB作为A=B的输出信号 𝑌(𝐴=𝐵)Y(A=B)。

图4.4.26给出的是一种实用的1位数值比较器电路。

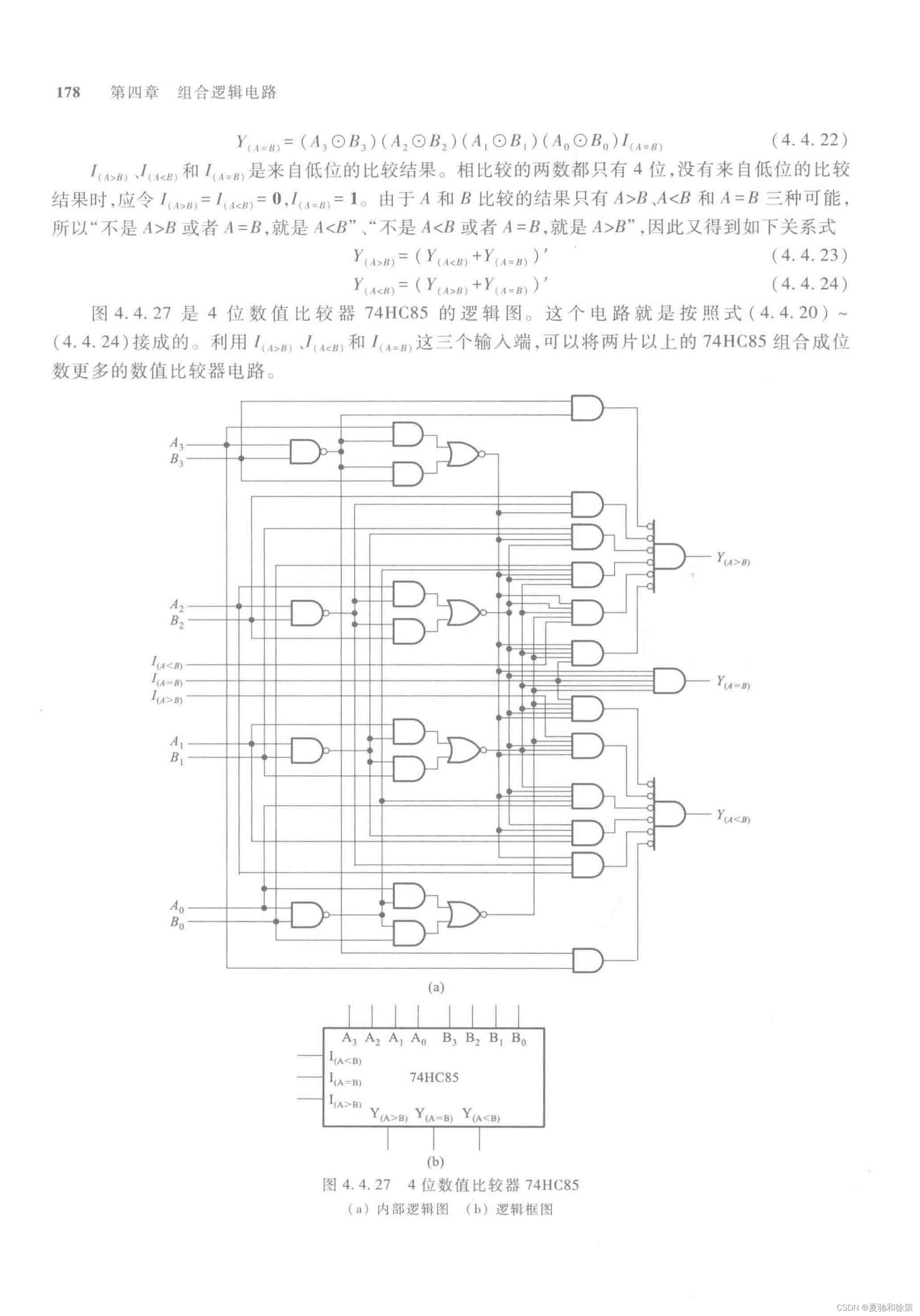

二、多位数值比较器

在比较两个多位数的大小时,必须自高而低地逐位比较,而且只有在高位相等时,才需要比较低位。

例如,A和B是两个4位二进制数A₃A₂A₁A₀和B₃B₂B₁B₀,进行比较时应首先比较A₃和B₃。如果A₃ > B₃,那么不管其他几位数码各为何值,肯定是A > B。反之,若A₃ < B₃,则不管其他几位数码为何值,肯定是A < B。如果A₃ = B₃,这就必须通过比较下一位A₂和B₂来判断A和B的大小了。依此类推,定能比出结果。

如果A和B是两个多位数的高4位数,那么,当A和B相等时,就需要以低位的比较结果来决定两个数的大小。根据上述原理,我们就得到了表示A > B、A < B和A = B的逻辑函数式:

𝑌(𝐴>𝐵)=𝐴3𝐵3′+(𝐴3⊕𝐵3)𝐴2𝐵2′+(𝐴3⊕𝐵3)(𝐴2⊕𝐵2)𝐴1𝐵1′+(𝐴3⊕𝐵3)(𝐴2⊕𝐵2)(𝐴1⊕𝐵1)𝐴0𝐵0′+(𝐴3⊕𝐵3)(𝐴2⊕𝐵2)(𝐴1⊕𝐵1)(𝐴0⊕𝐵0)𝐼(𝐴>𝐵)Y(A>B)=A3B3′+(A3⊕B3)A2B2′+(A3⊕B3)(A2⊕B2)A1B1′+(A3⊕B3)(A2⊕B2)(A1⊕B1)A0B0′+(A3⊕B3)(A2⊕B2)(A1⊕B1)(A0⊕B0)I(A>B)

𝑌(𝐴<𝐵)=𝐴3′𝐵3+(𝐴3⊕𝐵3)𝐴2′𝐵2+(𝐴3⊕𝐵3)(𝐴2⊕𝐵2)𝐴1′𝐵1+(𝐴3⊕𝐵3)(𝐴2⊕𝐵2)(𝐴1⊕𝐵1)𝐴0′𝐵0+(𝐴3⊕𝐵3)(𝐴2⊕𝐵2)(𝐴1⊕𝐵1)(𝐴0⊕𝐵0)𝐼(𝐴<𝐵)Y(A<B)=A3′B3+(A3⊕B3)A2′B2+(A3⊕B3)(A2⊕B2)A1′B1+(A3⊕B3)(A2⊕B2)(A1⊕B1)A0′B0+(A3⊕B3)(A2⊕B2)(A1⊕B1)(A0⊕B0)I(A<B)

𝑌(𝐴=𝐵)=(𝐴3⊕𝐵3)(𝐴2⊕𝐵2)(𝐴1⊕𝐵1)(𝐴0⊕𝐵0)𝐼(𝐴=𝐵)Y(A=B)=(A3⊕B3)(A2⊕B2)(A1⊕B1)(A0⊕B0)I(A=B)

其中,𝐼(𝐴>𝐵)I(A>B)、𝐼(𝐴<𝐵)I(A<B)和𝐼(𝐴=𝐵)I(A=B)是来自低位的比较结果。相比较的两数都只有4位,没有来自低位的比较结果时,应令𝐼(𝐴>𝐵)=𝐼(𝐴<𝐵)=0I(A>B)=I(A<B)=0,𝐼(𝐴=𝐵)=1I(A=B)=1。由于A和B比较的结果只有A > B、A < B和A = B三种可能,所以“不是A > B或者A = B,就是A < B”、“不是A < B或者A = B,就是A > B”,因此又得到如下关系式:

𝑌(𝐴>𝐵)=(𝑌(𝐴>𝐵)+𝑌(𝐴=𝐵))Y(A>B)=(Y(A>B)+Y(A=B))

𝑌(𝐴<𝐵)=(𝑌(𝐴<𝐵)+𝑌(𝐴=𝐵))Y(A<B)=(Y(A<B)+Y(A=B))

图4.4.27是4位数值比较器74HC85的逻辑图。这个电路就是按照上述公式接成的。利用 𝐼(𝐴>𝐵)I(A>B)、𝐼(𝐴<𝐵)I(A<B)和𝐼(𝐴=𝐵)I(A=B)这三个输入端,可以将两片以上的74HC85组合成位数更多的数值比较器电路。

4392

4392

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?