目录

做仿真时需要编写testbench,作为完全没学过verilog的小白,第一次碰到需要手写的verilog是testbench文件。那就正好从testbench入手,逐句学习verilog和testbench的语法。

什么是testbench及其作用:

Verilog 代码设计完成后,还需要进行重要的步骤,即逻辑功能仿真。仿真激励文件称之为 testbench,放在各设计模块的顶层,以便对模块进行系统性的例化调用进行仿真。

毫不夸张的说,对于稍微复杂的 Verilog 设计,如果不进行仿真,即便是经验丰富的老手,99.9999% 以上的设计都不会正常的工作。不能说仿真比设计更加的重要,但是一般来说,仿真花费的时间会比设计花费的时间要多。有时候,考虑到各种应用场景,testbench 的编写也会比 Verilog 设计更加的复杂。

Testbench测试机制:

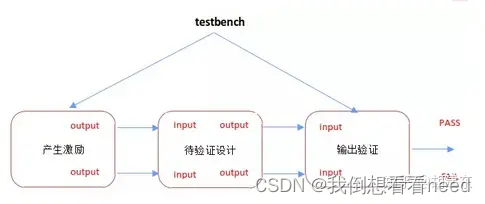

任何一个设计好的模块,都有输入和输出,此模块是否满足要求就是看给定满足要求的输入,是否能够得到满足要求的输出。所以testbench的测试机制就是:用各种verilog或者VHDL语法,产生满足条件的激励信号(也就是对被模块的输入),同时对模块的输出进行捕捉,测试输出是否满足要求。如下图,产生激励输出验证模块两个模块都属于testbench,最好的输出验证模块最终只需要给一个pass和fail的答案出来就可以了。不管是用一个信号表示pass和fail还是用$display()函数打印,最终简单明了的给出过或者不过的信息就好了。请大家写仿真文件的时候尽量做到这点。

完整的testbench结构:

module Test_bench();//创建verilog模块

信号或变量声明定义

逻辑设计中输入信号在这里对应reg型变量

逻辑设计中的输出信号在这里对应wire型

例化测试模块DUT

使用initial或always语句块产生激励

监控和比较输出响应

endmodule1、创建verilog模块:

编写testbench的第一步是创建一个 verilog 模块作为测试的顶层。

与verilog module不同,在这种情况下,要创建的是一个没有输入和输出的模块。因为设计人员希望testbench模块是完全独立的(self contained)。

下面的代码片段展示了一个空模块的语法,这可以被用作testbench。

module ();

//在这里写testbench

endmodule :2、声明变量并例化被测设计:

创建了一个testbench之后,必须例化被测设计,这可以将信号连接到被测设计以激励代码运行。下面的代码片段展示了如何例化一个被测模块。

本文介绍了Verilog中的testbench及其作用,包括测试机制、完整testbench结构、创建模块、声明变量、激励信号生成、任务与函数的使用以及系统任务。重点讲解了如何编写和设计testbench以确保模块功能的正确性。

本文介绍了Verilog中的testbench及其作用,包括测试机制、完整testbench结构、创建模块、声明变量、激励信号生成、任务与函数的使用以及系统任务。重点讲解了如何编写和设计testbench以确保模块功能的正确性。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

1684

1684

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?