中国科学院半导体研究所半导体超晶格国家重点实验室和中国科学院大学的科研团队对基于SPAD的成像技术进行了系统的介绍,包括SPAD器件、单光子成像涉及的关键电路以及二维灰度和时间分辨单光子图像传感器的最新研究进展。相关研究内容以“基于单光子雪崩二极管的成像技术综述”为题发表在《集成电路与嵌入式系统》期刊上。

从最初的光学成像到化学感光与记录成像,从真空 电 子成像到现在 的 固 态 成 像,成像技术经历了数次技术变 革 。 目前广泛应用于数码相机、手机、电脑、汽车等工业产 品的摄像头便是基于半导体工艺平 台生产的固态图像传 感器 。CMOS 图像传感器经历了近几十 年 的 发 展,一 直 向高分辨率、高动态范 围和高灵敏度方向不断突破,然而 CMOS 图像传感器受积分型成像原理及信 息量化方式 的 限制,难以集成更多功能。

基于单光子雪崩二极管(Single Photon Avalanche Diode , SPAD) 的成像技术是近年来兴起的新型视觉成像技术。单 光子图像传感器具有极高的灵敏度和动态范围以及皮秒 级的时间分辨率[1] , 能够同时获取灰度信息和深度信息, 具有三维成像能力 。上述特点使其在高动态成像、人脸识 别、自动驾驶 以及 AR/VR 等领域具有广阔的应用前景。 同时,相关应用也对 SPAD器件性能、像素面阵集成、时间测量方法等关键技术提出了更高的要求。

本文主要围绕基于单光子雪崩二极管的成像技术,从 单光子雪崩二极管器件、单光子成像关键电路、二维灰度 单光子成像以及时 间分辨单光子成像 4 个方面对相关技 术和研究现状做了简要的介绍。

1 单光子雪崩二极管

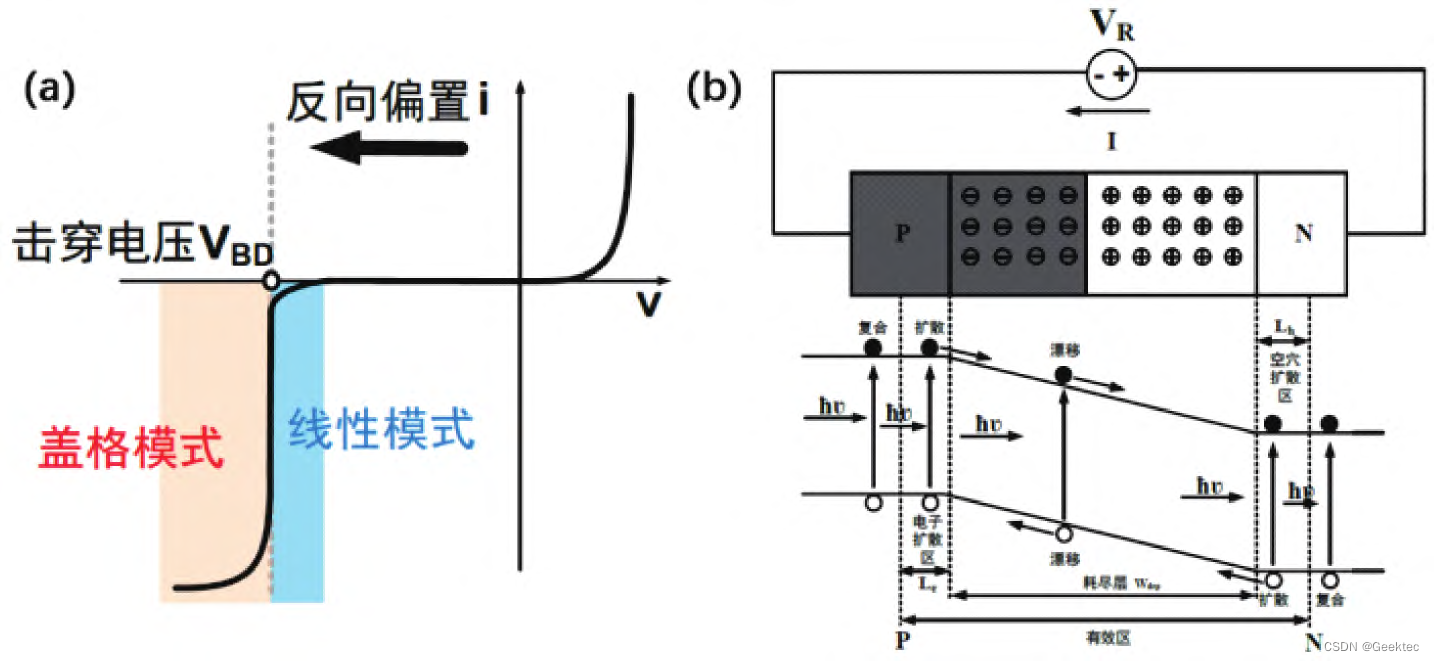

单光子雪崩二极管是单光子成像的关键核心器件,其 本质为一个工作在反 向偏压 下 的 PN 结,且工作电压高于 击穿电压,处于盖格模式,I-V特性曲线如图 1(a) 所示[2] , 反 偏 PN 结能带结构及电子 - 空穴对输运过程如图 1(b) 所 示 。其基本原理为:当耗尽 区(倍增 区)没有 自 由载流子并 且反向偏压达到雪崩击穿要求 的数值 时,SPAD 将处于稳 态,器件耗尽区中会形成很强 的 电场,但是没有自由载流 子发生 电离,待入射光产生 的光生载流子注入至耗尽区, 在雪 崩 倍 增 效 应 下 连 续 碰 撞 电 离 后 产 生 雪 崩 信 号。 SPAD 具有高灵敏度和高增益的特点。

SPAD 主要性能参数包括光子探测效率(Photon De- tection Efficiency , PDE) 、暗 计 数 率 ( Dark Count Rate , DCR) 、串 扰 (Cross Talk) 以 及 时 间 抖 动 ( Time Jitter) 等[2] 。SPAD 灵敏度主要由光子探测效率表征,指入射光 子触发雪崩的概率,由式(1) 表示:

PDE(λ) =QE(λ) × P t × FF (1)

式 中,QE 为 SPAD 量子效率,与 PN 结 的结深、耗尽 区的宽度和入射光子 的 吸 收深度有关,光子波长越长,在 硅材料中的平均穿透深度越深;P t 为雪崩触发概率,二者 相乘为光子探测概率(PDP) ;FF(Fill Factor) 为 SPAD 填 充因子 。填充因子是一个几何参数,在像素阵列中,取决 于单光子雪崩二极管感光 区和像素间距的比值大小 。 为 了提高光子探测效率,需要尽可能地增大填充因子。

暗计数率指的是无光照时由于热噪声或者势阱辅助噪声等引发的雪崩效应,反应了器件的暗 噪声水平[4] 。 串 扰则指 SPAD 阵列 中,器件之间相互干扰的情况,包括光学串扰和电学串。时间抖动是指 SPAD 检测光子 的 时 刻 产 生 输 出 脉 冲 时 刻 的 统 计 时 间 不 确 定 性 。 提 高 SPAD探测效率、降低 暗计数率、减小串扰和时间抖动是 SPAD 结构设计的目标。

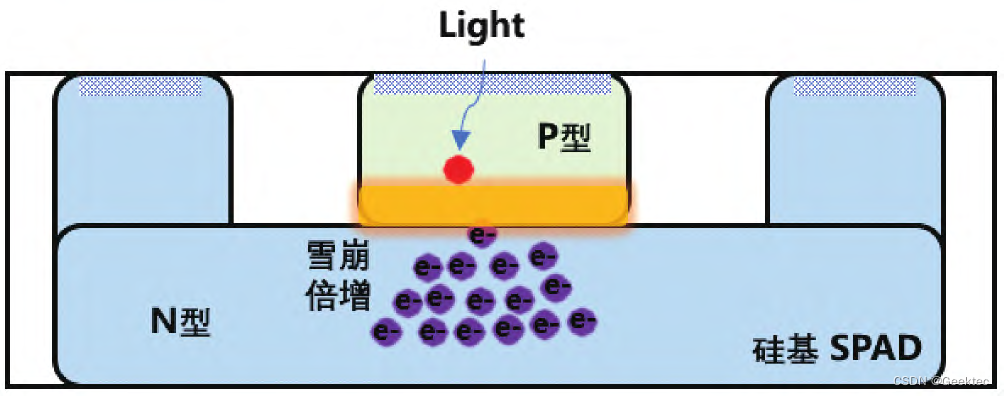

近年来,随着半导体工艺技术的飞速发展,CMOS 兼 容 的硅基 SPAD 器件研 究成果大量涌现 。 其典 型 结构如 图 2 所示,采用半导体制造 的离子注入工艺,形成 PN 结, 充分利用半导体工艺 的规模化 效应,实现低成本、高性 能 的 SPAD 器件。

按照光子入射方向,目前硅基 SPAD 器件主要分为前 照式和背照式两种结构,下面分别对相关研究进行介绍。

1.1 前照式单光子雪崩二极管

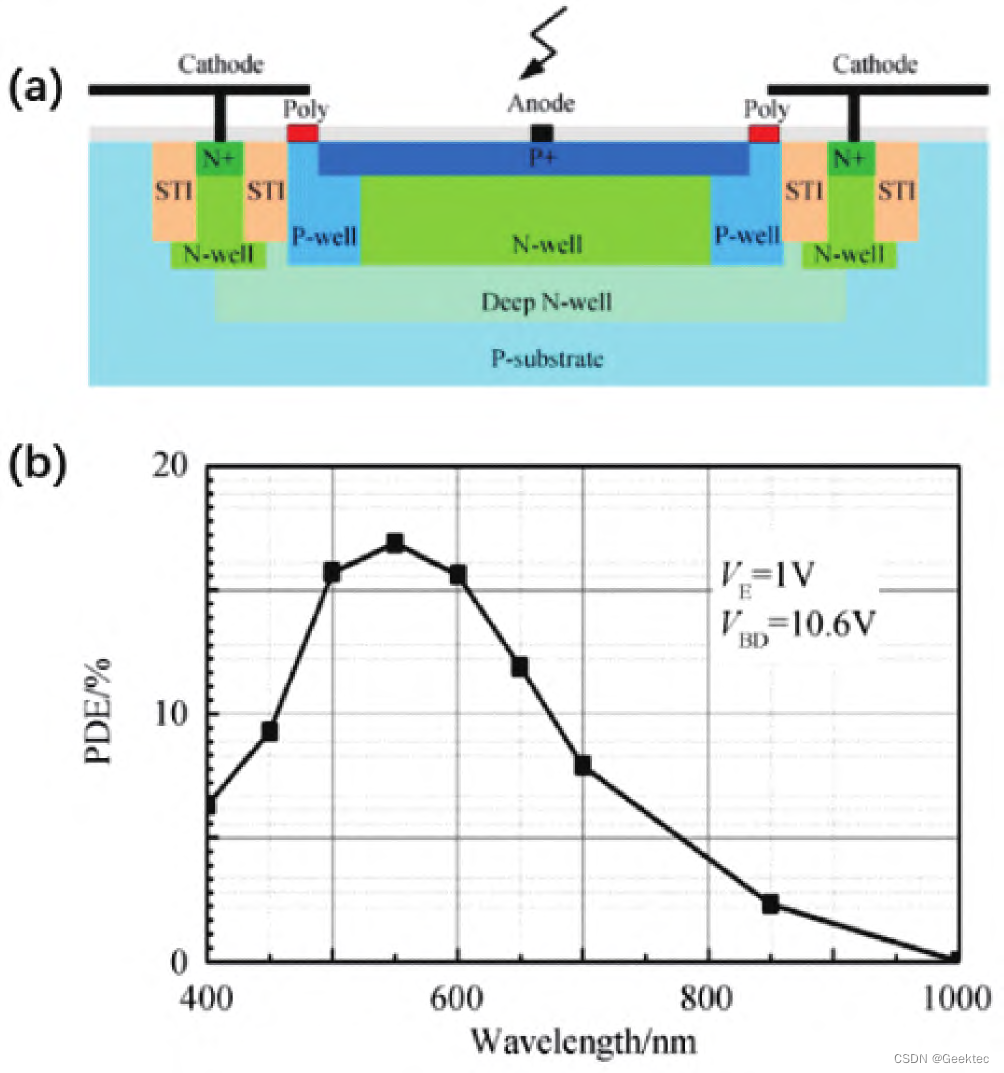

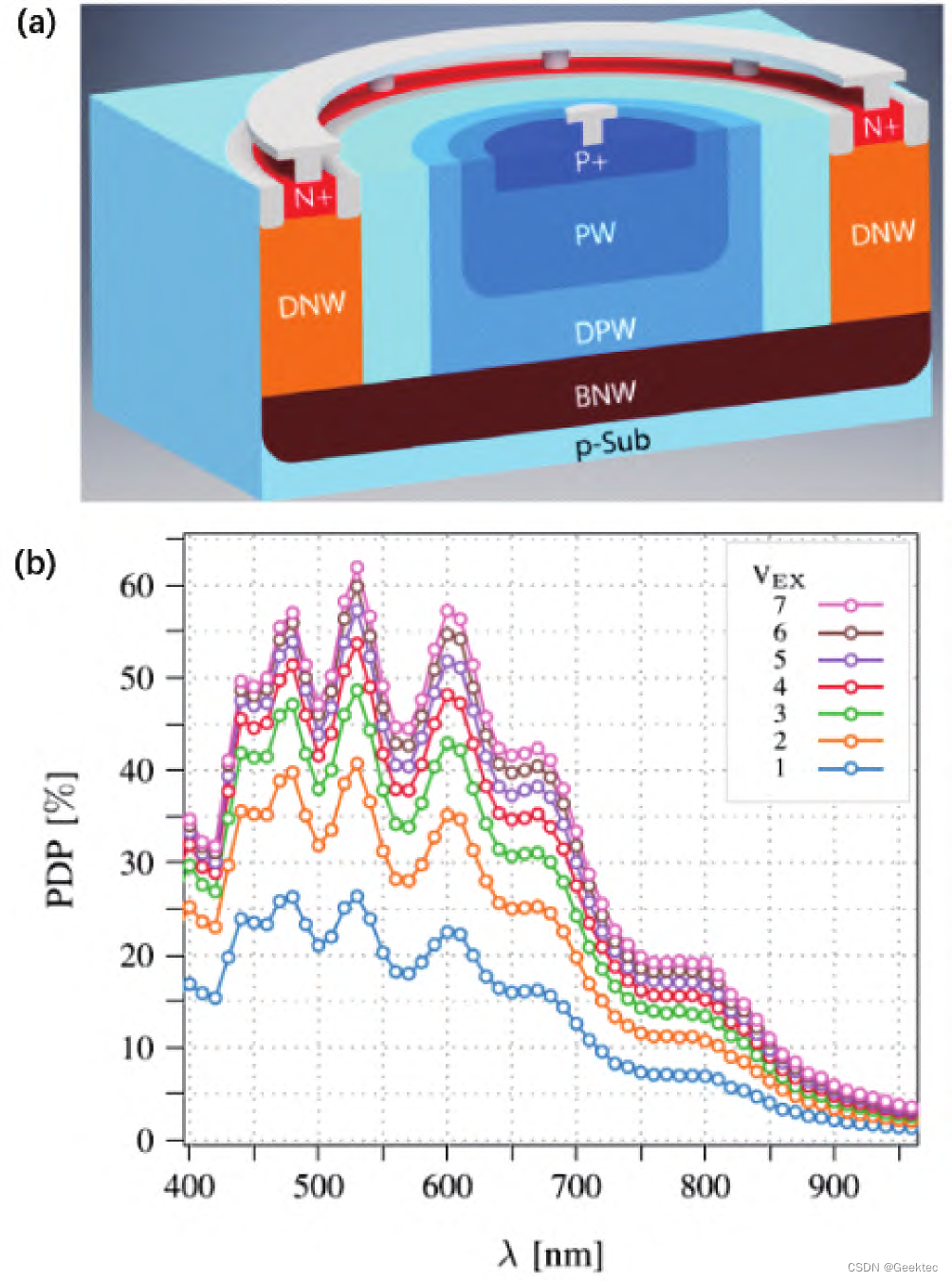

中国科学 院半导体研究所曹静等人基于标准 180nm CMOS工艺设计的一款前照式 SPAD 器件结构,如 图 3(a) 所示[5] 。该 SPAD 利用平 台 固 有 的 P+和 N- Well 离 子 注入层形成雪崩区,采用 P- Well 作为保护环,来 降低边 缘 电场 强 度,防 止 边 缘 击 穿 。 器 件 感 光 区 域 直 径 为 10 μm , 峰值 PDE 为 550nm 波 长 下 18% , PDE 随 波 长 变 化 曲线如 图 3(b) 所示。

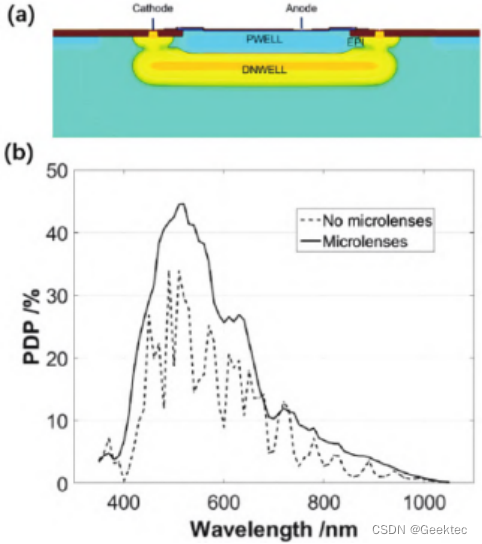

典型 的前照式 SPAD 器件还包括 P- Well/Deep N- Well 型结构,图 4(a) 为 意 法 半 导 体 Pellegrini 等 人 基 于 40nm标 准 CMOS 工 艺 设 计 的 一 款 SPAD 器 件[6] 。P-Well/Deep N-Well型 结 构 相 比 于 P+/N- Well 型,具有更深的感光区,有利于近红外波段探测效率的提升。该 SPAD 首次集成了微透镜工艺,使像素级别等效填充因 子接近 40% , 840nm 波长 PDP 为 5% , 如 图 4(b) 所示, 室温下平均 DCR 为 50 Hz 。英 国爱丁堡大学学者采用类 似结 构,基 于 130nm CMOS 工 艺,设 计 了 共 享 Well 型 4×4SPAD测试结构,像素 间距仅为 3 μm , 验证 了 SPAD 向小尺寸微缩的可行性[7] 。

出于人眼安全以及抗环境光干扰 的考量,SPAD 近红 外探测效率的提升对于三维成像等主动光探测应用具有 重要 的意义 。基于标准 CMOS 工艺设计的前照式 SPAD 器件结构,离子注入层较浅,近红外探测效率难以提高,因 此利用一 些 特 色 CMOS 工 艺 实 现 SPAD 器 件 性 能 的 提 升,也是 一 个值得探索的方向 。 台湾交通大学的 L. D. Huang 等人利用 180nm High-Voltage CMOS 工艺特有 的 HVPW 等离子注入层,设计了具有更深感光 区域 的前 照式 SPAD 结构,如 图 5 所示[8] , 该 SPAD 800nm 波长下 PDP 提升至 7.7% 。

瑞士洛桑联邦理工学院的 Gramuglia 等人基于 55nm Bipolar-CMOS-DMOS(BCD) 工艺,同样利用该平台特有 的离子注入层 设计 了 如 图 6(a) 所 示 的 SPAD 结 构[9] , 峰 值 PDP 在 530nm 波长下达到 62% , 800nm 波长下 PDP 达到 19% , 不同波长下探测概率如图 6(b) 所示。

虽然前照式 SPAD 性能有了较大的提升,但受工艺本身 限制,离子注入深度无法进一步提 高,并且光子需要穿 过较厚的电介质层才 能到达感光 区域,会有一 定损 失,而 在同一层芯片集成 SPAD器件和像素电路,也使像素填充 因子受到限制。

((a)器件结构;(b)不同波长 PDP[8] )

1.2 背照式单光子雪崩二极管

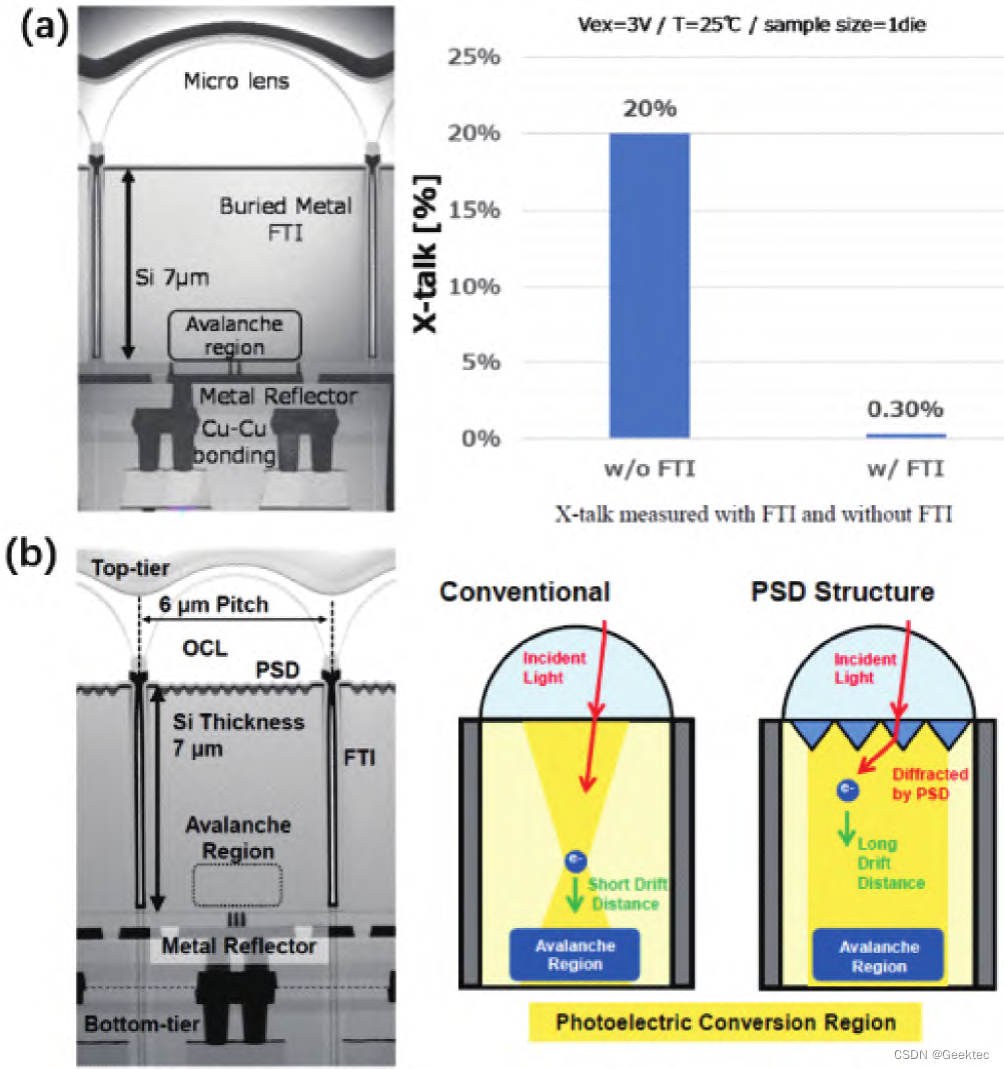

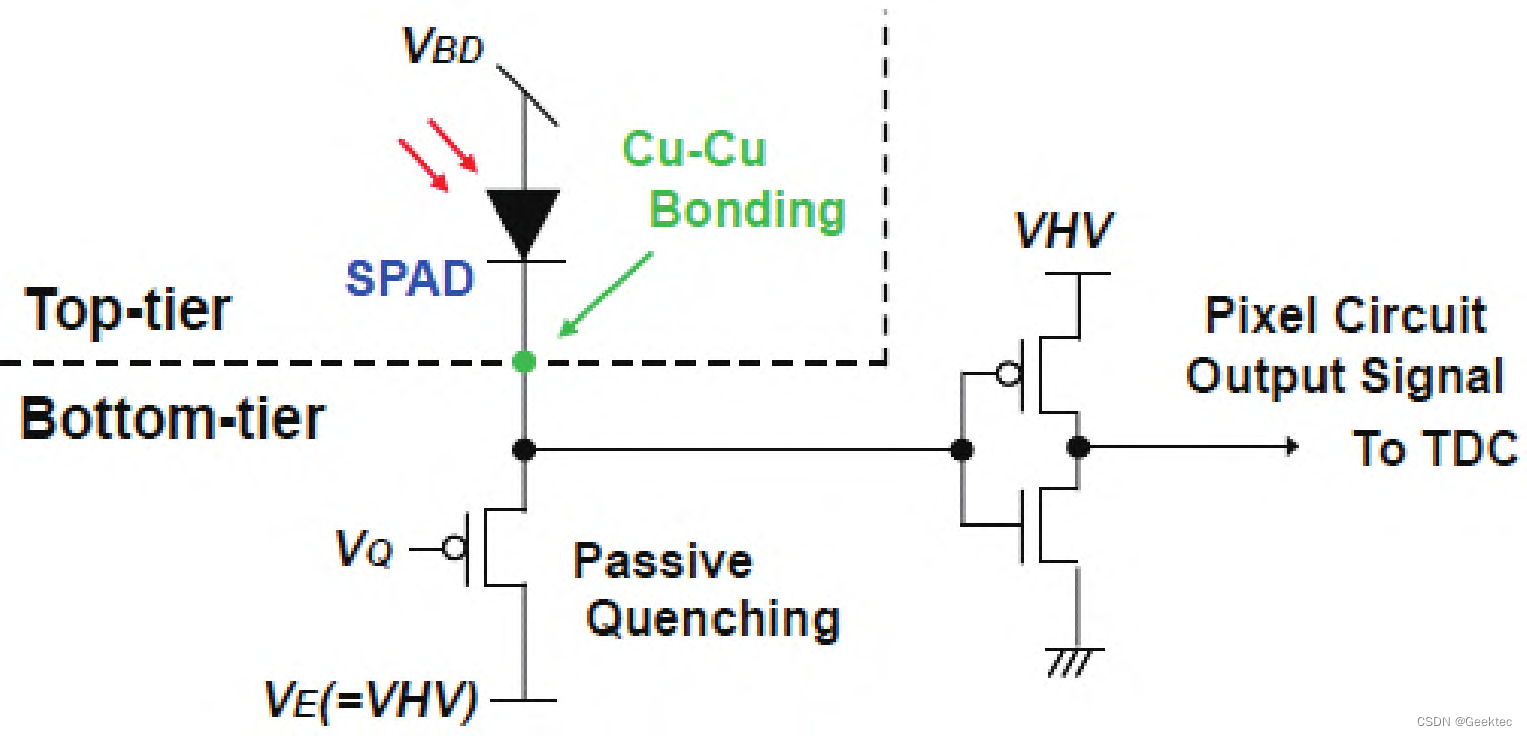

相比于前照式结构,背照式 SPAD 器件结构更有利于 三维堆叠集成,具有更 多 的优 势,下面将结合相关研究成 果进行具体介 绍 。 图 7 (a) 为日本索尼公司设计的 一 款 10 μm尺寸 的背照式 SPAD 器件[10] , 采用三维堆叠工艺, 上层芯片集成 SPAD 阵列,下层芯片集成像素电路阵列和 信号处理 电路,利用 Cu-Cu 混合键合的方式进行三维堆 叠 。采用 SPAD 和 电路分离 的方式可以提高像素填充因 子,并能够对两层芯片采用 的工艺分别进行优化,具有更 高的灵活度。

SPAD像素之间首次采用 了全沟槽 隔离(Full Trench Isolation , FTI) ,使像素 间 串扰 由 20% 降低 到 了 0.3% , 如 图 7(a) 所示[10] , 同时和底部金属连线组成围绕 SPAD 的 金属反射层,可 以将未触发雪崩的光子再次反射回来,提 高触发雪崩的概率 。 受益于背照式结构,雪崩 区深度可 以 做到 7 μm , 近红外探测效率得到进 一 步提升,940nm 波 长下 PDE 达到 14% 。

2021 年,索尼公司对上述结构做了进一步优化,实现 了一款 6 μm 尺 寸 的 背 照 式 SPAD 器 件,如 图 7 (b) 所 示[11] 。此 次优 化 除 了像素尺寸进 一 步缩小外,还 通 过 增

加 倒 金 字 塔 型 表 面 微 结 构 ( Pyramid Surface for Diffraction , PSD) 将微透镜汇 聚的光子进 一 步发散,增 加 光和硅的接触面积,使 940nm 波长 PDE 达到 20% 。

像素尺寸的微缩一直是图像传感器领域不断追求的 目标 。2022 年,索尼公司进 一 步将 背 照 式 SPAD 器件尺 寸缩小至 2.5 μm , 结构如 图 8(a) 所示[12] , 同时优化了表面 微透镜 的设计,使该 SPAD 峰值探测效率达到 76.1% , 940 nm 波长下探测效率达到 21.8% , 不 同尺寸 SPAD PDE 对 比如 图 8(b) 所示。

((a)2.5~3.3 μm结构;(b)不同尺寸 SPAD PDE[12] )

除了索尼公司以外,也有其他公司和研究机构投入大 量资源开展 SPAD 器件研 究 。 日本佳能公司通过掺杂调 节的方式设计 了一款 Charge-Focusing 型 SPAD 器件[13] , 可将雪崩区以外的光生载流子汇聚到雪崩 区,提高雪崩触 发概率,该结构可达到近似 100%填充因子的效果,同时保 持较小的雪崩区域,也有利于降低器件暗噪声水平。

关于 SPAD 器件 结 构的研究成果仍然在不断涌现, SPAD 器件尺寸相 比 于 CIS 图像传感器像素尺寸仍然有 一定差距,其尺寸的进一步微缩和器件性能的提升必将面 临新的问题和挑战。

2 单光子成像关键电路

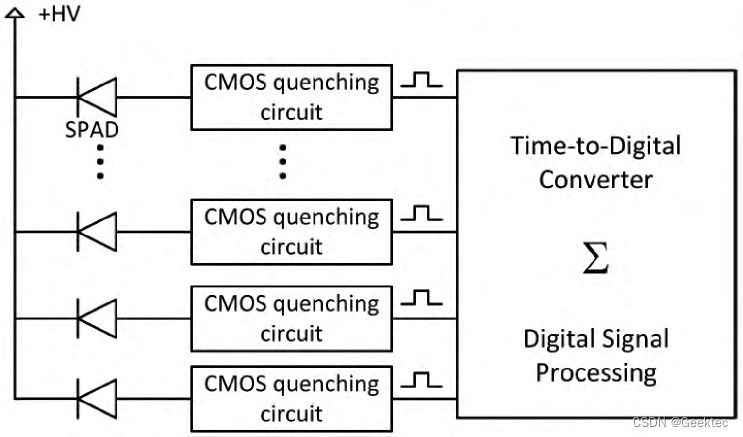

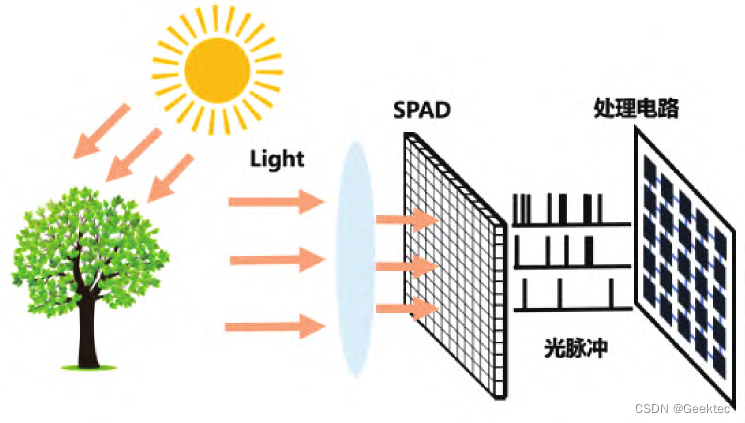

除了核心感光器件单光子雪崩二极管,单光子成像还 需要结合 同 SPAD相匹配的关键电路,包括像素淬灭电路和相关性检测等前端电路,以及进行时间分辨的时 间测量 或时间门控电路 。一个简单 的 SPAD 三维成像信号处理 流程示意图如图 9 所示[14] 。 下面将分别对涉及到的关键 电路进行介绍。

2.1 像素淬灭电路

当单光子雪崩二极管被触发雪崩后,如果没有外界 的 作用,将一直维持在雪崩状态,无法再进行单光子检测,且 过大的雪崩电流会使器件产生损耗,因此通常会将单光子 雪崩二极管与淬灭-恢复电路联合使用 。根据工作机制, 淬灭-恢复 电路可以分为被动式、主动式以及门控式三 种 。 下面将结合具体成果分别进行介绍。

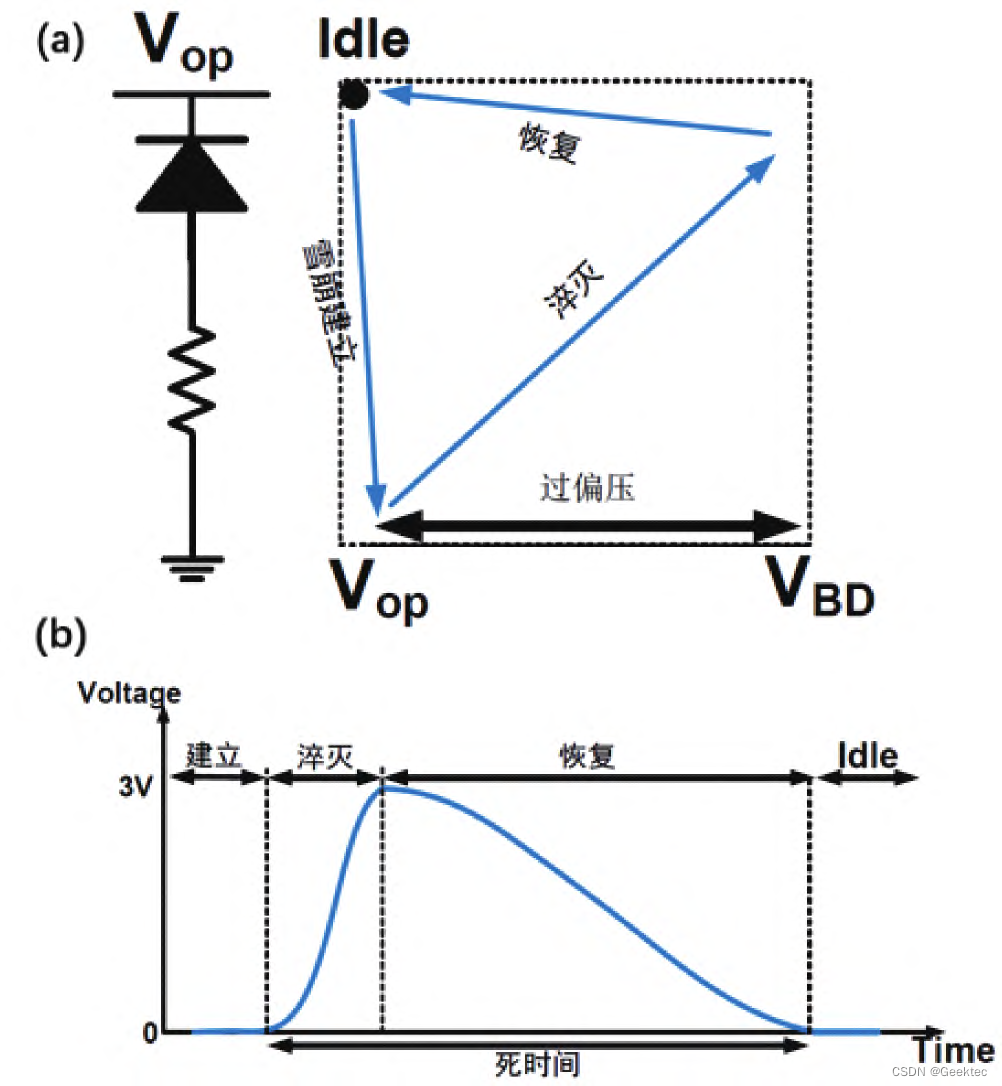

以被动淬灭-恢复 电路为例,分析其工作原理,最简 单 的被动淬灭-恢复 电路是将 SPAD 直接与一个较大阻 值 电 阻 串联,如 图 10(a) 所示[2] 。 当 SPAD 被触发雪崩,雪 崩电流流过淬灭 电 阻 时,电 阻上会产生足够大的压降,使 得 SPAD两端的偏置电压低于击穿电压,此时耗尽区的电 场强度不足以让载流子继续引发碰撞电离,因此雪崩过程 被淬灭 。在雪崩淬灭后,PN 结耗尽区的寄生 电容将通过 电阻缓慢充电到初始偏置电压,并具有再次进行单光子检 测 的能力 。对于电阻淬灭恢复 电路,恢复 时 间 由 RC 时 间 常数决定,R 为淬灭电阻阻值,C 为耗尽区寄生结电容。

雪崩二极管淬灭和恢复过程的持续时间又被称为死 时 间,如 图 10(b) 所示[2] , 处于死时间内的单光子雪崩二 极管不具有检测光子的能力。

在具体像素电路中,被动淬灭-恢复电路往往使用一 个 MOS 管 和 SPAD 串联的方式实现,如 图 11 所 示[11] 。 其 中,将 VQ 控 制 的 MOS 管 作 为 一 个 可 调 电 阻,实 现 SPAD 器件被动淬 灭 功 能 。 雪崩信号再经过 一个反相器 整形输出至外部电路。

较长的死时间会影响 SPAD计数效率,进而影响传感 器的成像动态范围,器件方面可以通过减小耗尽区寄生 电 容的方式降低死时 间,而在像素 电路方面,则可 以采用主 动淬灭-恢复电路来减小死时间,增加光子计数率。

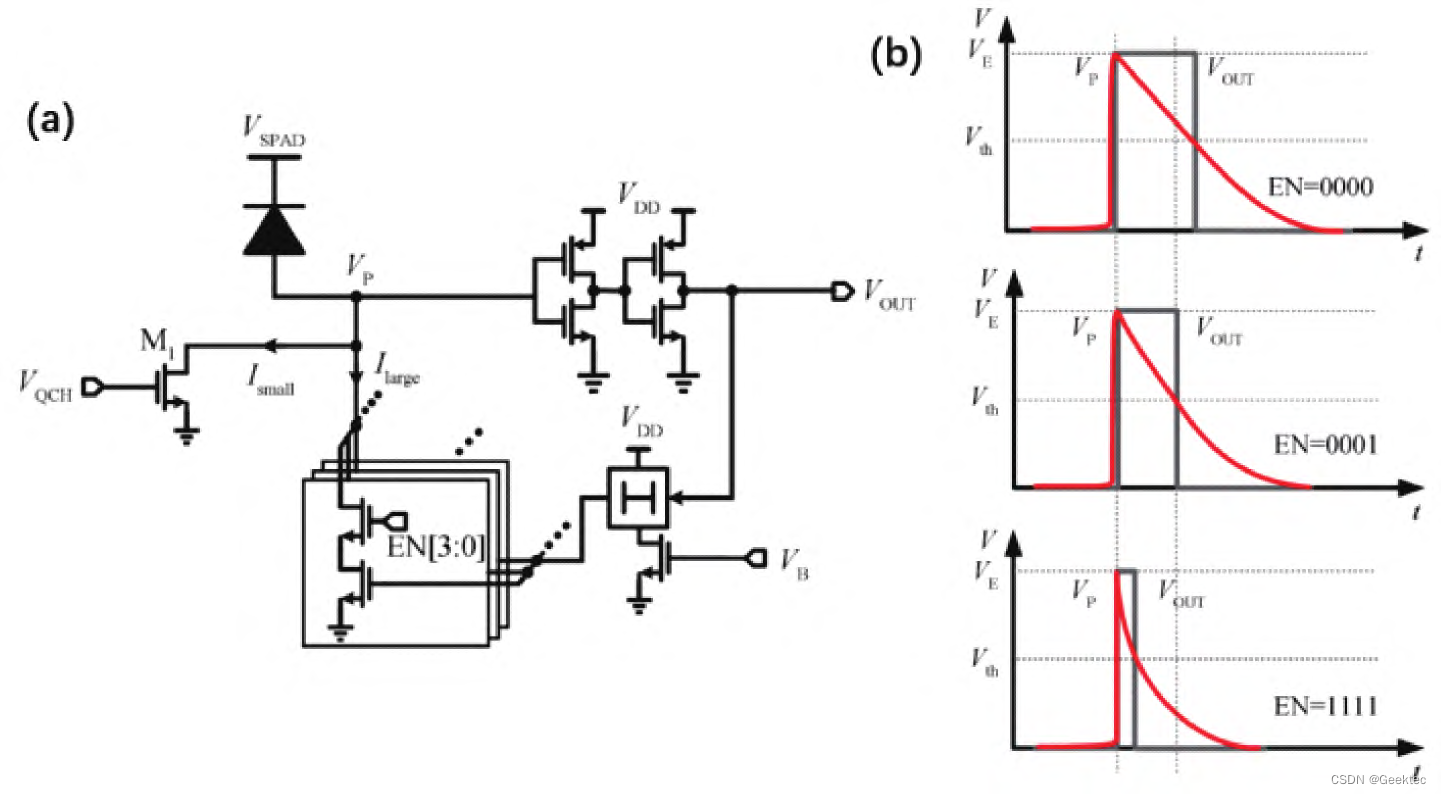

图 12(a) 为曹静等人设计的一款基于延迟链反馈回路的主动淬灭-恢复像素 电路[5] , 该 电路 由 M1 组成 的被动 支路和使能信 号 EN 控制 的主动支路 组成 。 当 SPAD 被 触发,VOUT 产生输 出信号,该信号在经过一个延时单元后, 将打开一个额外支路,加速 SPAD 恢复过程 。 图 12(b) 中 脉冲信号宽度可以反映死时 间 情 况,可 以 看 到,在 EN= 1111 , 即主动支路全部打开时,死时间被大幅缩小。

上述主被动像素淬灭电路均没有施加额外的控制信号,SPAD 处于 自 由运行(Free Running) 模 式,该模 式 下, 只要不 处 于 死 时 间,均 有 可能被触发雪崩 。 在 面 阵 型 SPAD 传感器 中,通常会对 SPAD 像素电路施加外部控制 信号,以根据传感器的工作状态周期性地使能或关闭 SPAD , 这种模式被称 为 门控(Gating) 模 式 。 门控模 式 的 SPAD像素电路仅在使能信号打开 时工作,可 以 降低像素 的功耗,避免不必要的检测。

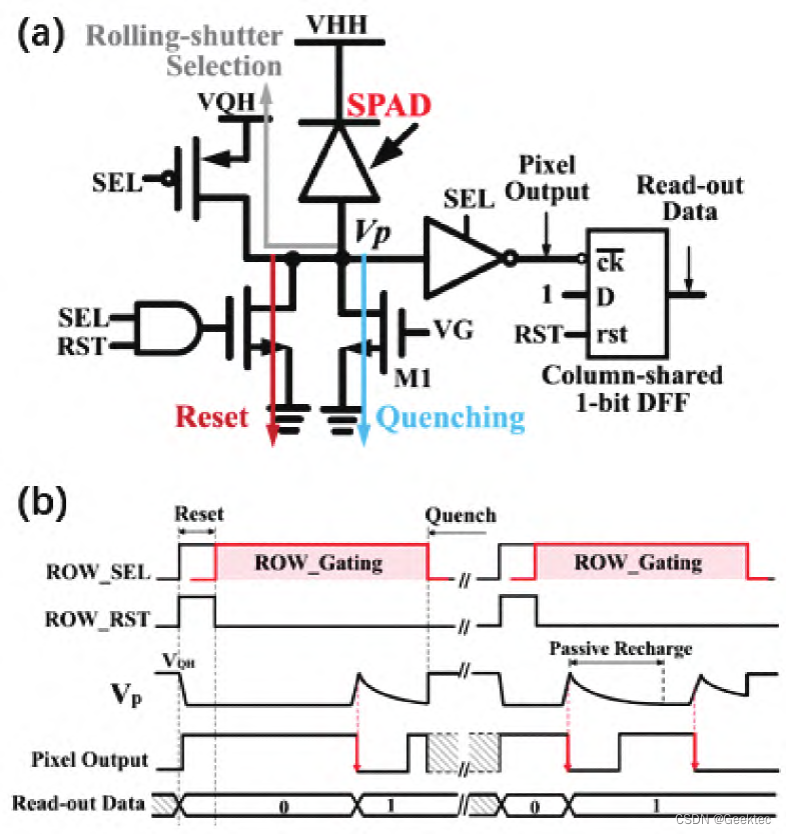

图 13(a) 为中国科学院半导体研究所杨旭等人设计 的一款结合被动淬灭和门控功能的 SPAD 像 素 电 路[15] 。 其 中 VG 控制 的 M1 可实现被动淬灭功能,SEL 为使能控 制信号,当 SEL 关 闭,SPAD 阳极将被偏置 到 VQH , 其两 端反 向偏 压 小于雪崩电压值,SPAD 处 于 关 闭 状 态 。 当 SEL 打开,同 时会有一个 RST 重置信号将 SPAD 阳极拉 到地,SPAD 处于工作状态,此 时如果 SPAD 被触发,将产 生一个雪崩信号,经过三态门输出至外部电路 。该像素 电 路的工作时序如图 13(b) 所示。

2.2 相关性检测电路

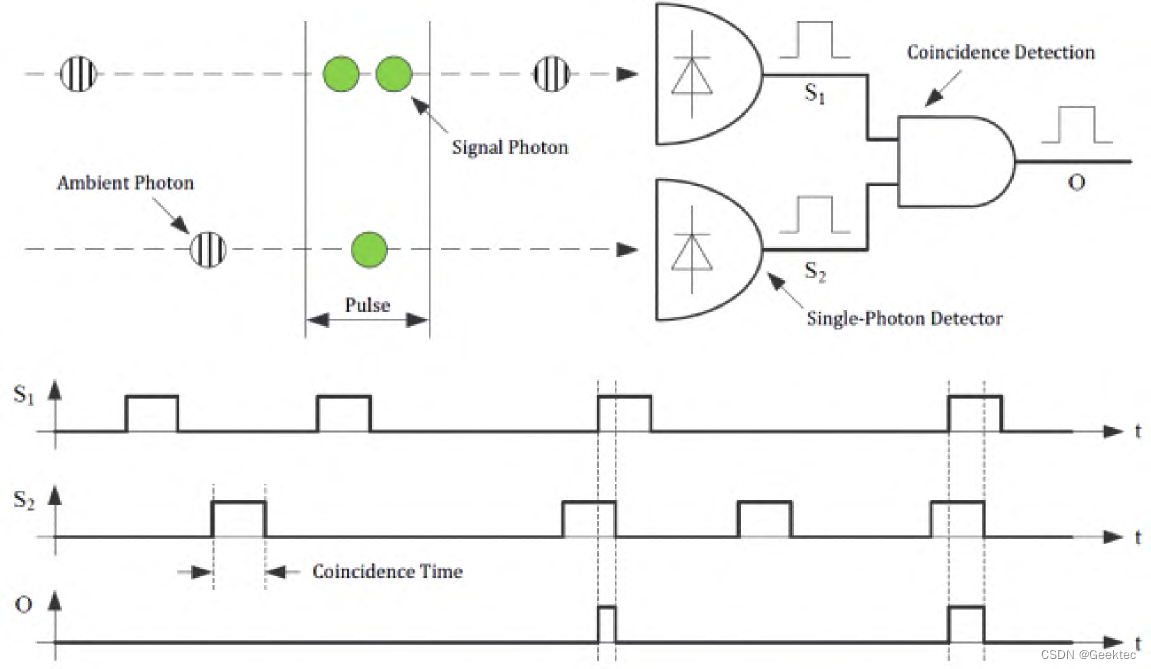

SPAD 三维成像需要结合主动光对物体进行探测,此 时环境光和暗噪声都将成为干扰信 号 。 相关性检测 (Co-incidence Detection , CD) 也称作重合检测或并发性检测, 是目前常用的抑制环境光干扰 的手段 。 基本原理为利用 环境光子随机分布、信号光子集中分布的特点,通 过 将2×2或 3×3 等多个像素构造成宏像素,将其输出信号合 并为一个输出信号,并设置一个时 间 窗 口(一般等于激光 脉冲宽度),在该窗口内各个像素同时开启,对到来 的光子 进行检测并记录个数,若达到设定阈值的情况,则认 定为 信号光子,进 行保存,反之则认为是环境光子,不进 行 保 存,从而达到抗环境光干扰的目的。

下面以一个基于与门的相关性检测电路为例,做进一 步说 明 。如 图 14 所 示[16] , 将 两 个 SPAD 组 成 一 个 宏 像 素,两个 SPAD 输 出通过一个与门进行相关性检测,仅 当 两个 SPAD 同时被触发时,宏像素才有脉冲信号输出 。通 过此种 方式可以减小环境光等背景信号干扰,提 高 信 噪比。

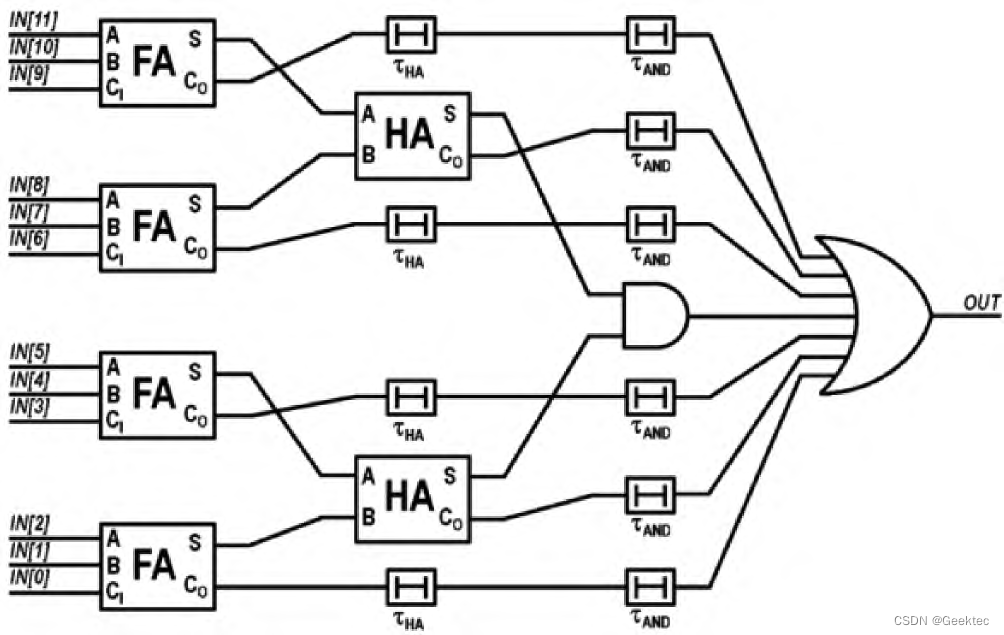

通过与门方式实现的相关性检测,电路 原理简单,但 当宏像素包含的 SPAD 个数增多,与门规模会变得非常庞 大,难以对任意两个输入进行检测 。 图 15 为 Niclass 等人 提出的一种基于加法器的相关性检测电路[17] , 该 电路 由 4个阶段 的逻辑 门 组成,IN[11:0] 是 宏 像 素 中 SPAD 输 出 经过整形后的脉冲信号,宽度为 4ns 或 8ns , 电路包含 4 个全加法器(FA) 、2 个半加法器( HA) 、1 个与 门和 1 个或 门,可实现任意两个 SPAD 输出间的相关性检测,当有两 个或多个 SPAD被触发时,该电路会有信号输出。

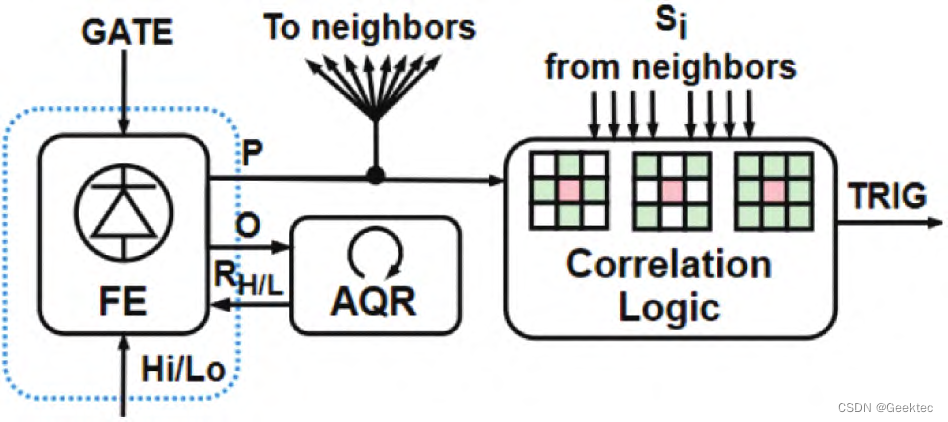

基于宏像素方式实现的相关性检测,会损失 图像分辨 率 。2022 年,意 大 利 的 Manuzzato 等人提出 一 种不损失 分辨率的相关性检测方法,如 图 16 所示[18] , 每一个 SPAD 初级输出信号都将给到 临近 SPAD , 而该 SPAD 最终输 出 也将经过临近 SPAD信号 的验证,只有当临近 SPAD 也有 触发时,该 SPAD 才会产生最终输出信号 。该 电路 的输 出 仍然 与 SPAD 一 一对应,因此并不损失图像传感器 的 分 辨率[18] 。

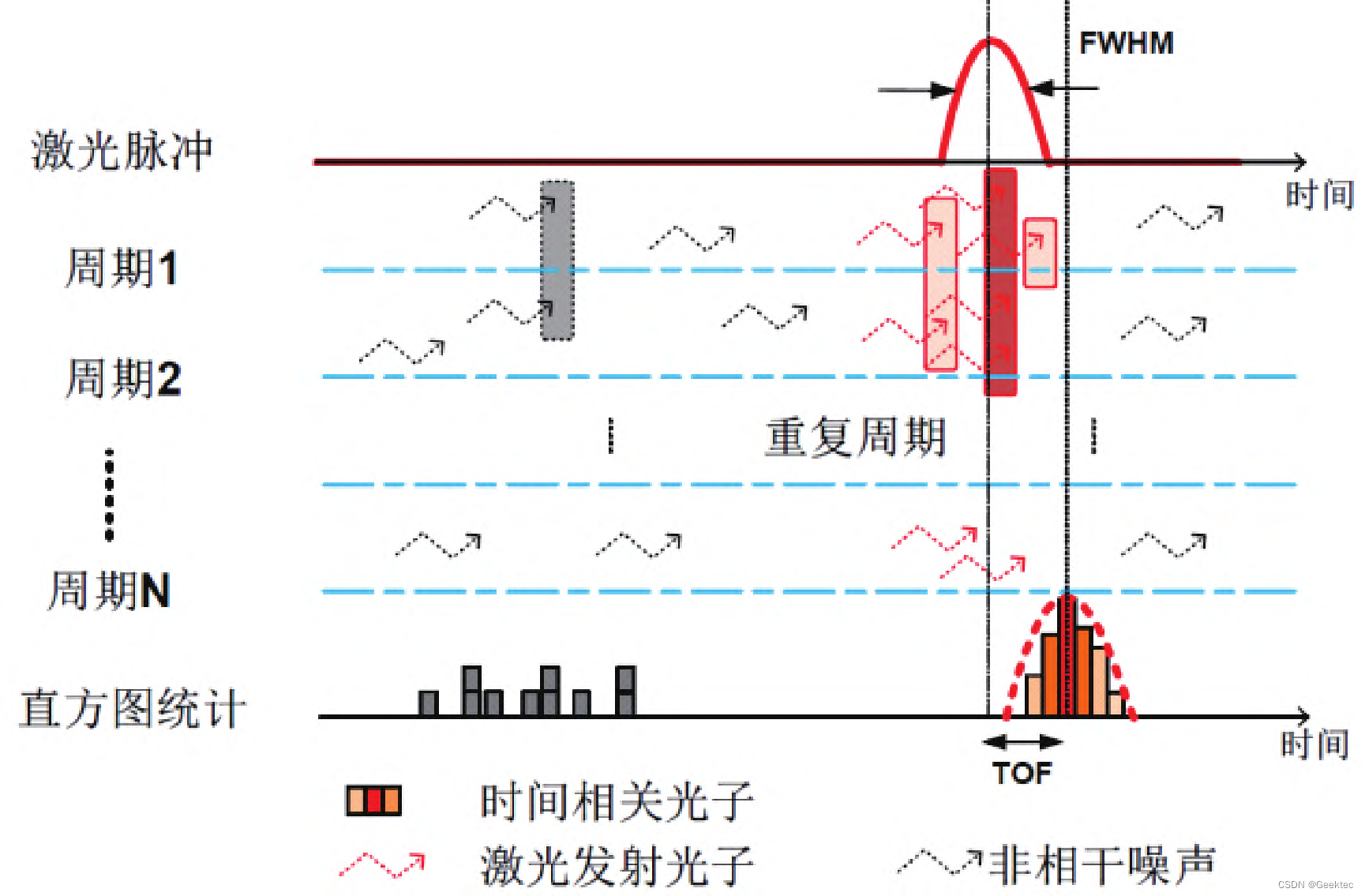

2.3 时间测量电路

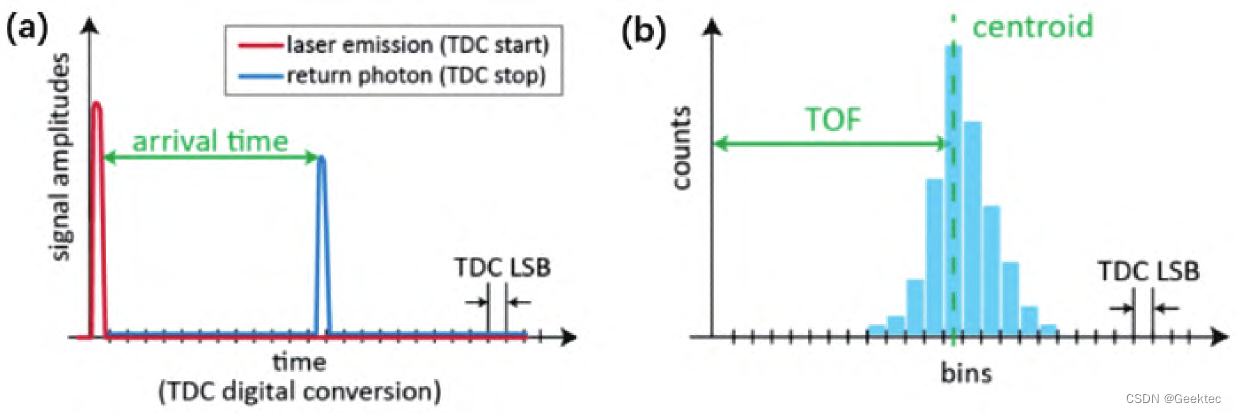

时 间 数 字 转 换 器 ( Time-to- Digital Converter , TDC) 可 以用来对时 间信 息进行测量,是单光子图像传感 器实现时间分辨成像的关键电路,其 原 理 如 图 17(a) 所 示[19] 。通过测量激光发射和返回之间的 时 间 差,计 算 得 到物体距离信息 。理论上进行一 次测量即可获得该时间 差,但在实际测量中,由于存在环境光和暗噪声等干扰信 号,通常会进行多次测量并进行直方图统计,进而从 统计 直方图中计算物体的距离信息,如 图 17(b) 所示。

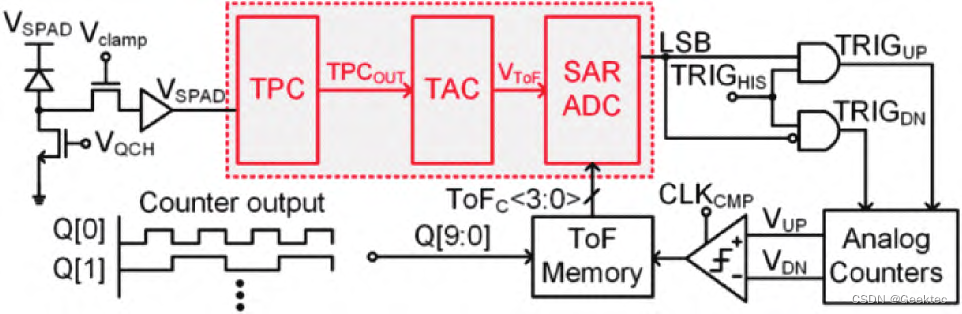

TDC 的实现方 式有很 多种,主要可 以 分 为模 拟 类 和 数字类,下面对其中的 一 些典型结构和研究成果进行介 绍 。 图 18 是韩国蔚山科学技术院 Su-Hyun Han 等人基 于模拟方式实现的一款 TDC 结构[20] , 通过时间模拟转换 器(Time to Analog Converter , TAC) 将接收到的时间信息 转换为模拟的电压信号,之后通过一个逐次逼近模数转换(Successive Approximation Register ADC , SAR ADC) 对电压信号进行量化 。 该 TDC 集成在 35 μm×35 μm 的 像素 单 元 内,耗 较 低,可 实 现 等 效 230 ps 的 时 间 分 辨率。

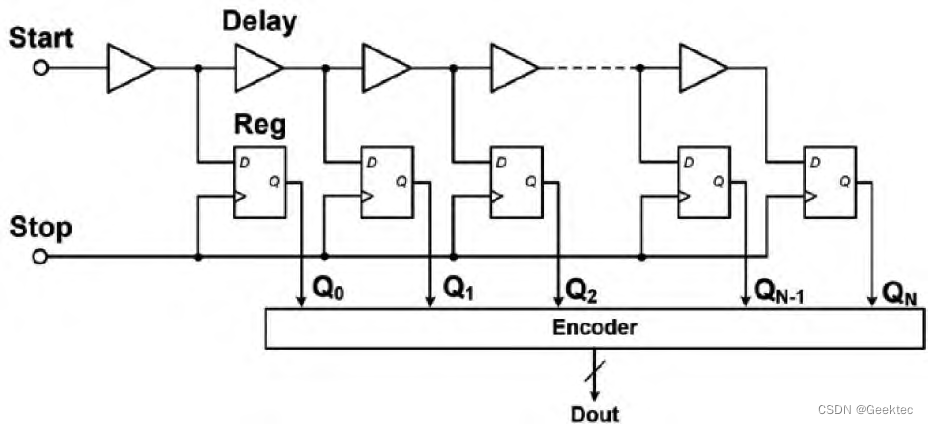

数字型 TDC 包 含 多 种 结 构,下 面 以 延 时 链 TDC 为 例,介绍数字型 TDC 的基本原理,如 图 19 所示[21] 。输入 Start 信号在多级延 时单元组成的延时链中传播,每经过 一个延时单元对应产生 一 个 延 时 信 号,然 后 由输入 Stop 信号对这组延时信号进行采样,输 出 N 位温度计码,再经 过译码器转 换 为 TDC 最终输出的二进制数字码 Dout 。 该结构 TDC 的时间测量分辨率取决于延时链中延时单元 的延时长度,常见 的延时单元包括反相器、缓冲器等 。 通 常来说,基于延时链 的 TDC 能够实现较高的采样率,且结 构简单,设计难度低,但它 的动态范围受限于延时链的级 数,也就是延时单元的数量 。一味地增加延时链级数会导 致 TDC抖动性能的恶化,从而 降低 TDC 线性度。

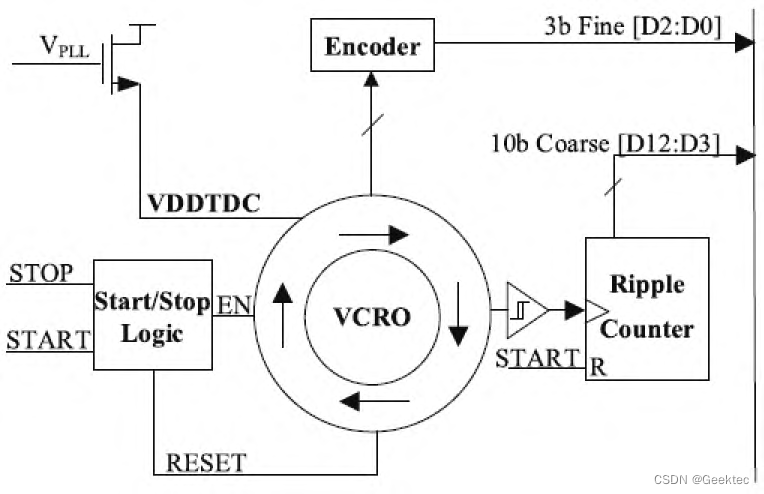

环形振荡器 TDC 结构 紧凑、精度较 高,图 20 为 西 安 电子科技大学胡进等人设计的 一 款基于环形 振 荡 器 的 TDC 结 构[22] 。 该 TDC 由 Start/Stop 逻辑 电 路、计 数 器、 压控环形振荡器和内部编码电路构成 。 Start/Stop 逻 辑 电路定义需要量化的时间间隔,由首尾相连的延迟单元构 成的压控环形振荡器仅在该时间间隔内打开 。 时 间量化分为两个部分,即粗量化和细量化 。为了实现粗量化,压控 振荡器的最后一个相位被连接至一个计数器,用来计数在量 化时间间隔内经历了多少个整数振荡周期。细量化则通过 对振荡器内部状态编码实现。该 TDC 可实现 200 ps 的时间 分辨率,微分非线性和积分非线性分别为+0.24/-0.29LSB 和+1.02/-2.53LSB。

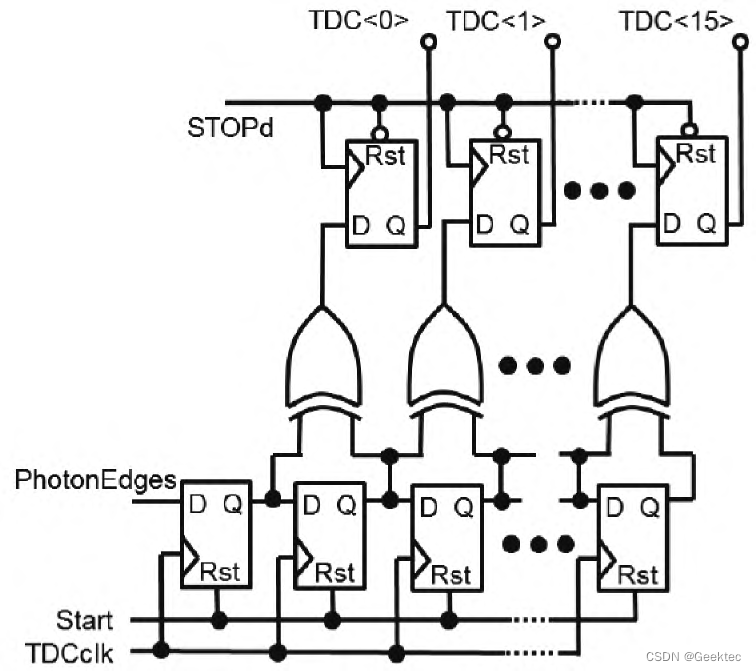

TDC对时 间信息进行量化后,按 照其 大 小“ 放置”在 相应 的 BIN 中,经过直方图统计,确 定 峰 值 位置,而 能够 实现上述片上直方图功能的 TDC 被称为直方图统计 型 TDC( Histogramming TDC , hTDC) 。 图 21 为英 国爱丁堡 大学 的 Hutchings 等人设计 的一款 hTDC[23] , 该 hTDC 包 含两条移位寄存器延迟链,寄存器延迟链长度对应直方 图 BIN 的个数,BIN 的 宽度由时钟信号 TDCclk 周 期 决 定, 可 以在 计 时 测 量 过 程 中 实 时 将 计 数 结 果 存 储 在 相 应 BIN 中。

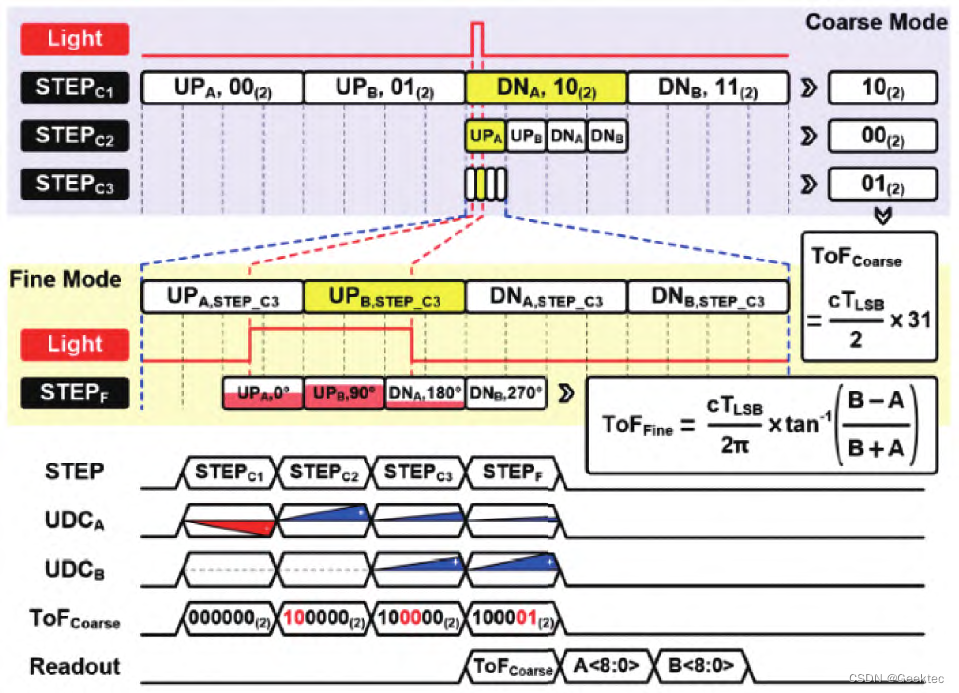

韩国蔚山科学技术院的 Park 等人采用分步逐次逼近 的方式实现了一款 hTDC , 原理如 图 22 所示[24] 。该hTDC 采用与 SAR ADC类似 的原理,通过累计不同时间范围内 的计数值,在时 间尺度上,按粗细分步得到回波信号峰值 位置 。该 hTDC 基于 110nm 工艺平 台,可集成于像素单 元 内部,能实现等效 100 ps 的时 间分辨率。

不 同结构 的 TDC 电路具有各自的特点和优势,在设 计图像传感器时,需要从时间分辨率、动态范 围、面积和功 耗等多维度综合考虑。

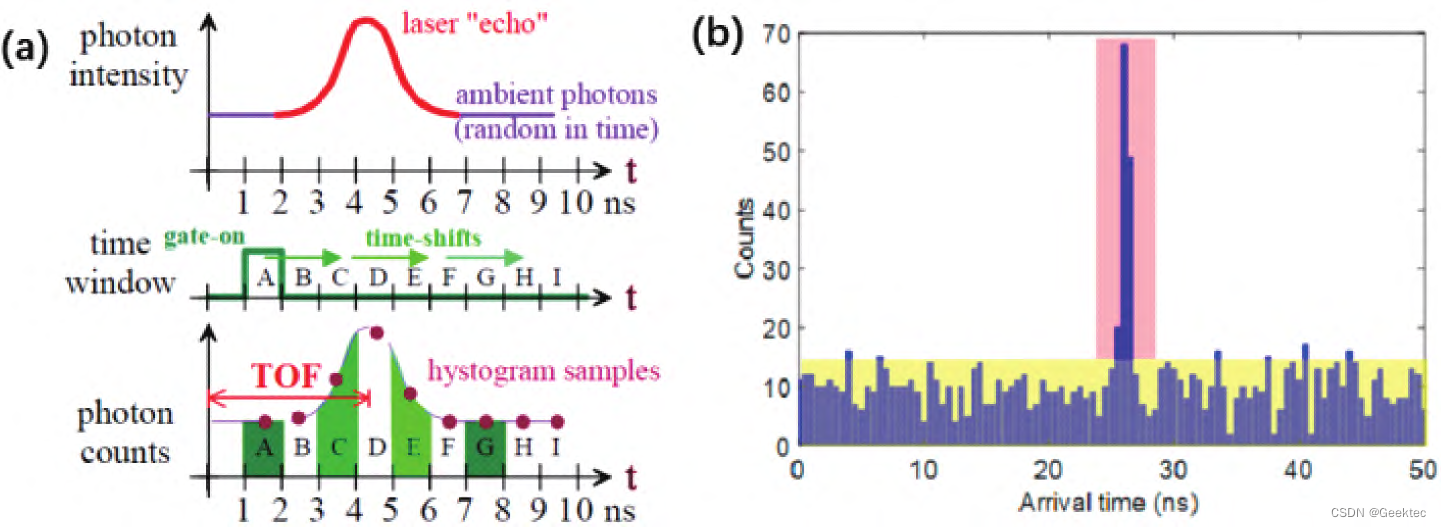

2.4 时间门控电路

基于 TDC方式的时间分辨成像,效率较高,但采用像 素级 TDC会降低填充因子,不利于像素大规模集成,而采 用列共享 TDC , 则很难兼容全局曝光模 式,并 且 TDC 电 路本身也存在死时间等问题 。 除此之外,基于单光子 的 时 间分辨成像,还有一种采用时间门控的光子计数法 。 其原 理如 图 23(a) 所示[25] , 通过一个随时 间逐步位移的门控信 号对门控时间内 SPAD 输 出进行计数,以扫描 的方式,经 直方 图 统 计,得到时间尺度上返回的信号光 子 信 息,如 图 23(b) 所示[25] 。 时 间 门控方法可以将 门控产生电路置 于像素阵列外部,不影响像素填充因子,相对而言,像素 电 路架构更简洁,有利于像素大规模集成,实现高分辨率 成像。

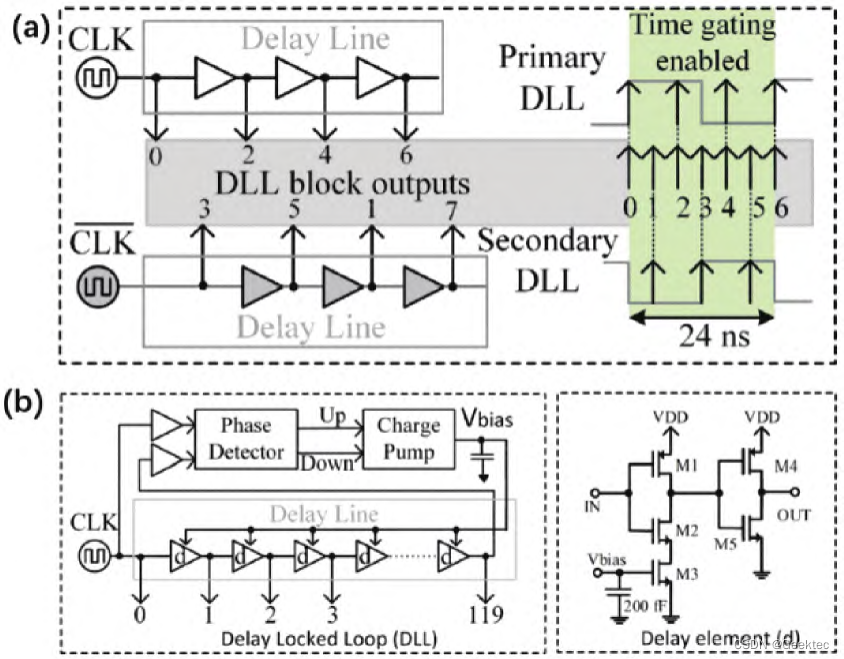

时间门控方式的关键是产生一个具有高时间分辨率 的 门控信号 。 除了片外给进以外,片上集成的时间 门控产 生 电路 通常基于延迟锁相环 (Delay Locked Loop , DLL) 实现。

图 24 为芬兰奥 卢 大 学 Ruokamo 等人实现的 一款用 于 SPAD三维成像的时间门控产生电路[26] , 该 电 路 由 两 级 DLL 组 成,采 用 周 期 为 24ns 的 参 考 时 钟,通 过 单 个 DLL 的 119 级延迟单元,产生 约 200 ps 的延迟信 号 。 两 级 DLL 分别采用反相时钟,最终可以产生约 100 ps 的 时 间 门控延迟信 号 。 该电路整体结构如图 24(a) 所 示 。 其 中,单个 DLL 由鉴相器、电荷泵和一个压控延 时链 组成, DLL 结构和延迟单元如图 24(b) 所示。

3 二维灰度单光子成像技术

前文对 SPAD 器件和单光子成像涉及的关键电路进 行 了介绍,下面将介绍基于 SPAD 和上述关键电路实现的 二维灰度和时间分辨单光子图像传感器,首先会介绍相应 的成像技术原理,之后介绍相关研究成果。

传统 的 CMOS 图像传感器通过对光信号进行光 电转 换,并对光电流积分得到光强信 息,之后进行模数转换和读 出 。基于 SPAD 的单光子成像技术与上述方式不同,通 过雪崩 效应实现对光子的快速检测,具有单光子级灵 敏度。

SPAD 二维灰度成像的基本原理 如 图 25 所 示,将入 射光视为在空间和时间上 随机离散分布的光子,经 SPAD 转换为随机离散的电学脉冲,其脉冲密度便对应了光强信 息 。通过对一定时 间 内 SPAD 输出的离散电学脉冲进行 计数,便可实现对光强 的检测,这一探测方式被称为单光子计数法 。 因此,SPAD 二维 图像传感器又被称为单光子 计数图像传感器[27] 。

((a)门控产生 电路;(b)DLL 与延迟单元电路[26] )

3.1 高分辨率二维灰度成像

2003 年,由苏黎世联邦理工学院的 Rochas 等人 实现 的首个 CMOS 工艺 兼 容 的硅基 SPAD 阵 列,像 素规模仅 为 4×8 , 像素尺寸为 75 μm[28] 。2005 年,瑞士洛桑联邦理 工学 院 的 Niclass 等人基于 0.8 μm HV CMOS 工艺 实现 了 32×32 分辨率 的 SPAD 阵列传感器[29] 。

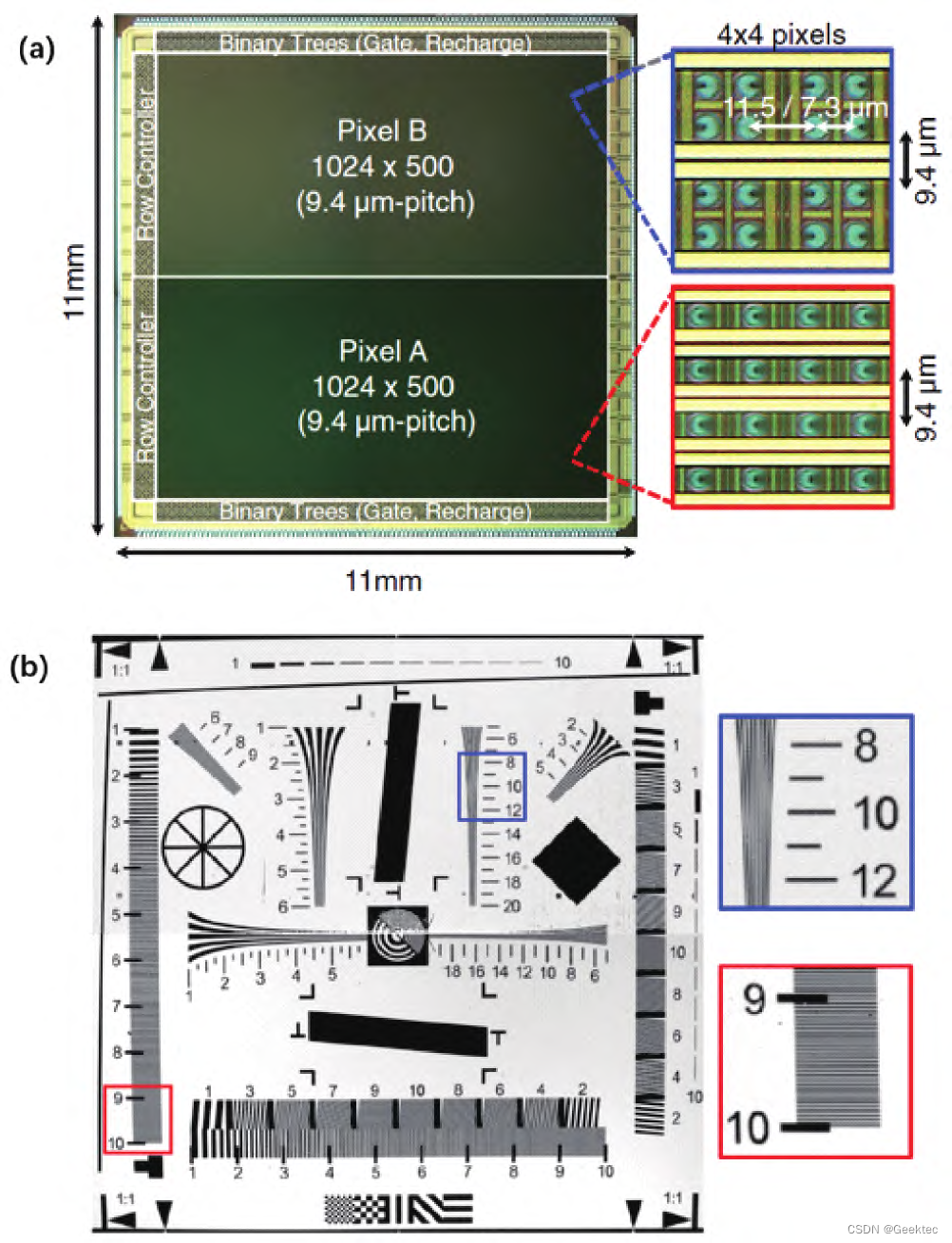

近年来,随着半导体工艺技术的飞速发展,国 内外 多 个研究机构和企业都投入了大量 资源开展 SPAD 器件及 像素阵列相关的研 究,并取得了一系列重要的研究成果。 2020 年,洛桑联邦理工学院的 Morimoto 等人基于180nm CMOS 工艺,首次突破 了 百 万像素 SPAD 图像传感器,芯 片显微照片如 图 26(a) 所示,二维灰度成像效果如图 26(b) 所示[30] 。该图像传感器分辨率为 1 024×1 000 , 像素尺寸 为 9.4 μm , 其 中类型 A 的像素电路仅包含 7 个 晶体管,而 类型 B 通过 2×2 共享部分像素电路的方式,平均每个像 素仅包含 5.75 个 晶体管。

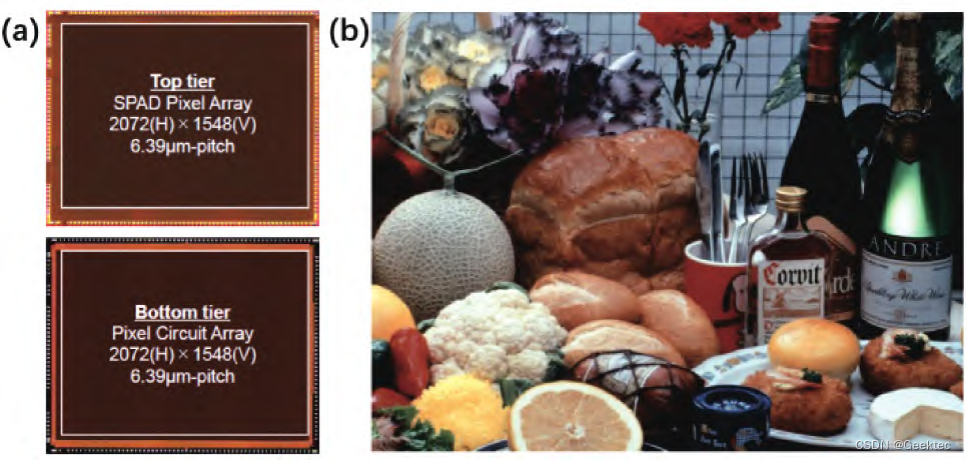

2021 年,日本佳能公司推出了 320 万像 素 SPAD 图像传感 器,芯片显微照片如图 27 (a) 所 示,成 像 效 果 如 图 27(b) 所示[31] 。该图像传感器采用三维堆叠工艺,上层 芯片基于 90nm 工艺,下层芯片基于 40nm 工艺,像素 阵 列规模达到 2 072×1 548 , 像素采用前面介绍的 Charge- Focusing 型 SPAD , 尺寸为 6.39 μm 。

((a)芯片图片;(b)成像结果[31] )

3.2 高动态二维灰度成像

SPAD 具有单光子级灵敏度,同 时基于单光子计数 的 成像方式不受满阱容量 限制,因此可以实现高动态成像。

洛桑联邦理工学 院 的 百万像素 SPAD 图像传感器通过双 曝光模式可以实现 108.1dB 高动态范 围成像[30] 。 意法半 导体 的 Dutton 等人基于 40nm 工 艺 实现 的 一款 96×40 分辨率 SPAD 图像传感器,动态范 围最高可到 109dB[32] 。 2019 年,英 国爱丁堡大学 的 Henderson 等人,基于三维堆 叠工艺实现 了一款 120dB 动态 范 围 SPAD 图像传感器, 分辨率为 256×256 , 像素尺寸为 9.2 μm[33] 。

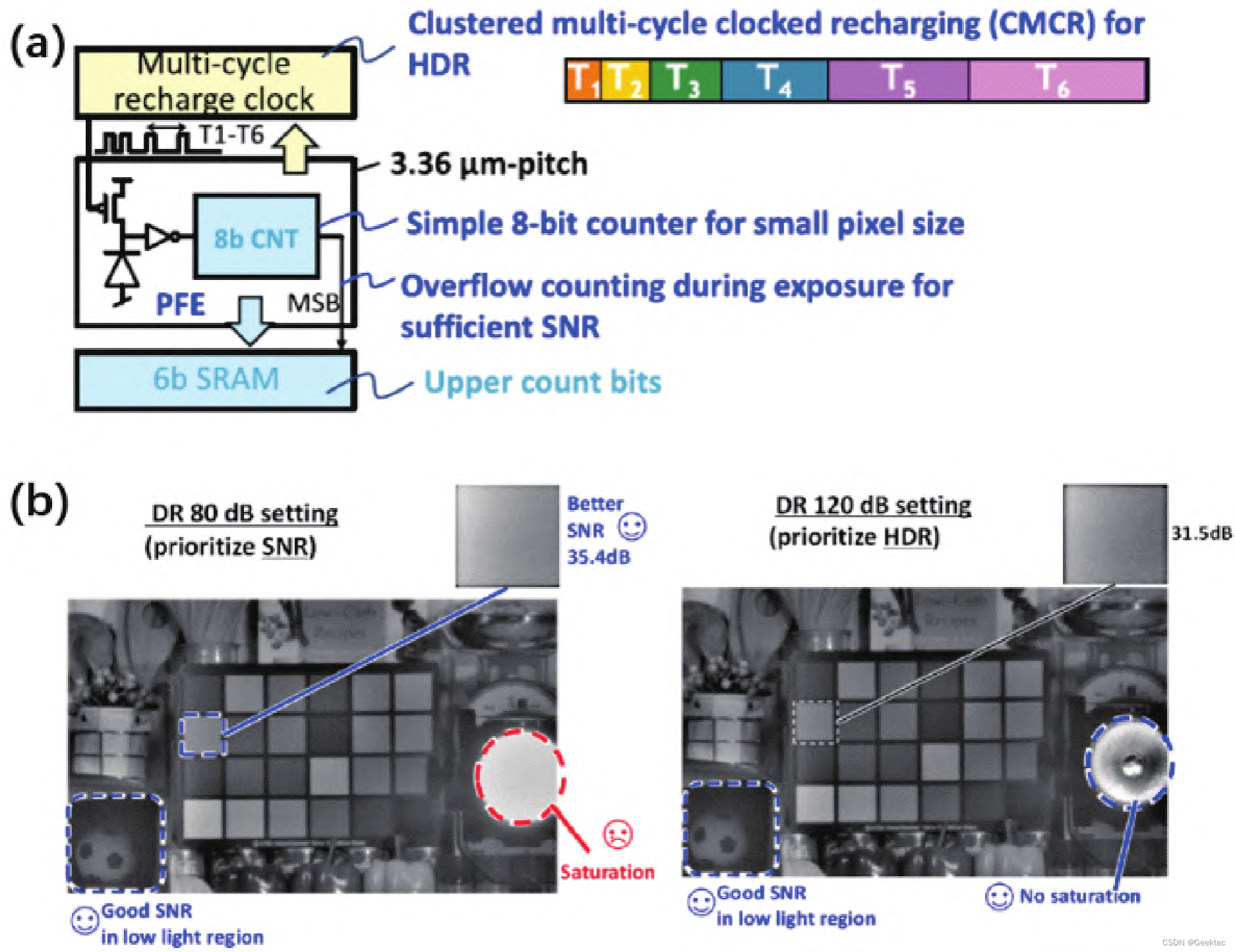

2024 年,索 尼 公 司 的 Takatsuka 等 人 基 于 90nm 和 22nm 三维堆叠工艺,利用多周期时钟复位和最高有效位 读 出技术实现 了 120dB 动态 范 围 SPAD 图像传感器,像 素 电路如 图 28(a) 所示,成像效果如 图 28(b) 所示[34] , 该 图 像传感器分辨率为 748×448 , 像素尺寸仅为 3.36 μm 。

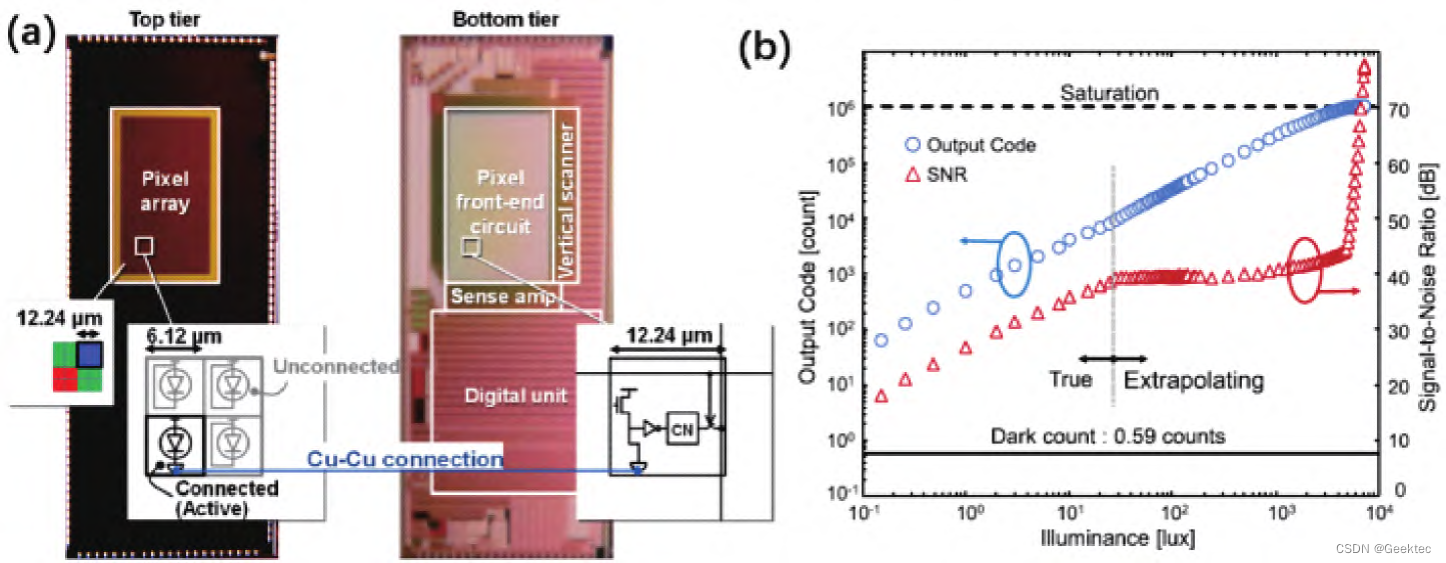

索尼公司的另一款 SPAD 图像传感器,如 图 29(a) 所 示,由 Ogi 等人设计,基于 90nm 和 40nm 三维堆叠工艺, 利用 9 位计数器和计数值外推技术,可 实现 124dB 的动 态范 围,测试结果如 图 29(b) 所示[35] 。

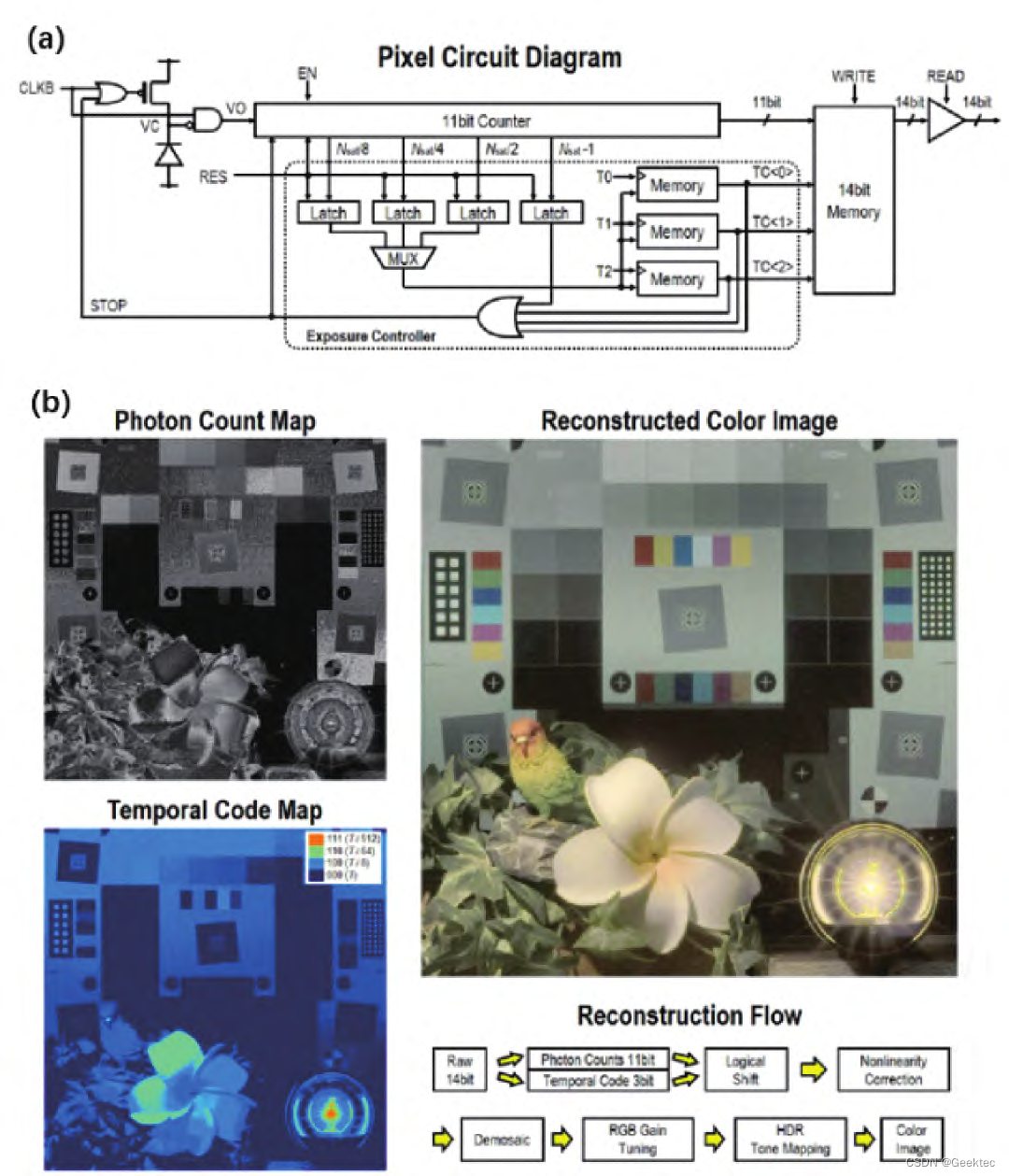

佳能公司利用 11 位计数器,结合自适应时钟复位技 术,提 出一款 143dB 高动态 SPAD 图像传感器 。 其像 素 电路如 图 30(a) 所示,高动态成像结果如图 30(b) 所示[36] ,该图像传感器分辨率为 960×960 , 像素尺寸为 9.5 μm , 同 样采用三维堆叠架构。

((a)高动态光子计数电路;(b)高动态成像[34] )

伴随工艺技术的不断进步,各公司和研究机构 的研 究 成果不断涌现,基于单光子成像技术的 SPAD 图像传感器 也在向更高分辨率和更高动态范围快速发展。

4 时间分辨单光子成像技术

SPAD 具有皮秒级的时间分辨率,可 以实现高精度 时 间分辨 成 像,采用的技术被称为时间相关单光子计数 (Time-Correlated Single Photon Counting , TCSPC) , 该 技术在光子计数的基础上发展起来,可以记录下光子 的到 达时 间,原理如 图 31 所示[2] 。 其利用环境光子造成 的触 发在时间上是随机分布的,而激光回波光子造成的触发具 有时 间相关性,在脉冲光强度较弱,重复频率较高时,通过 测量多个周期内的光子到达时间建立直方统计图,从而得 到回波光脉冲的准确波形,并与环境光造成的随机分布噪声相区分。

TCSPC 技术所使用的具体计时方法和关键电路在前 面已经进行了介绍,下面介绍基于 SPAD 实现的时间分辨 单光子成像技术在两个方 向 的应用,主要包括三 维 TOF (Time of Flight) 图像传感器和荧光寿命成像。

4.1 三维 TOF 图像传感器

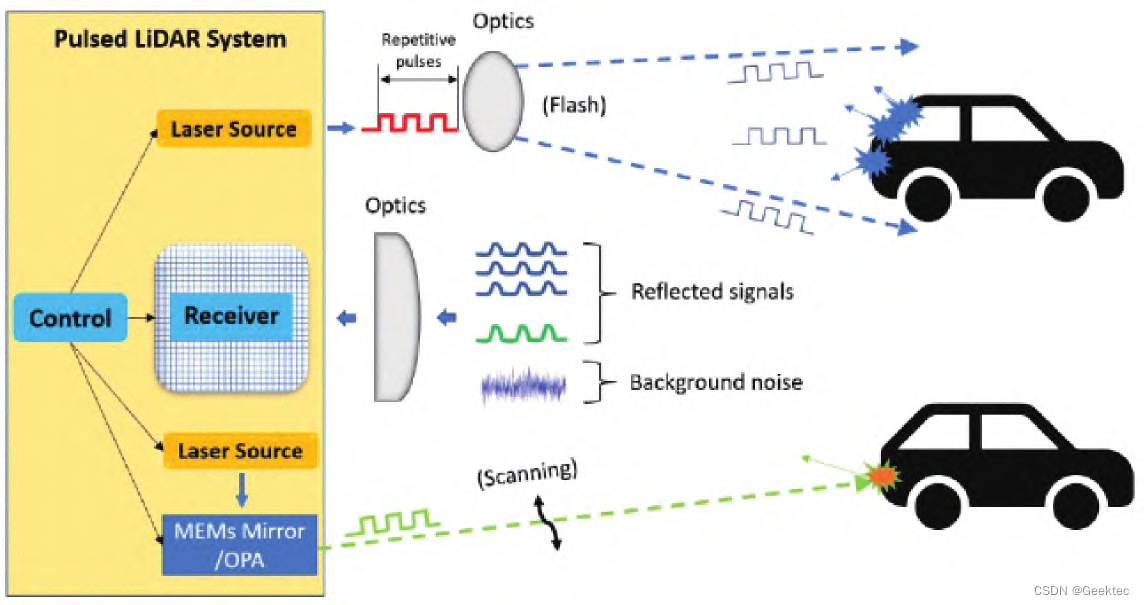

SPAD 三维成像主要采用直接飞行时间(Direct Time of Flight , D-TOF) 测距法,原理如 图 32 所示[37] , 通过测 量激光发射到传感器接收到激光回波信号的时间,确定物 体 的距 离 信 息 。 式 (2) 描述了飞行时间 T 与 距 离 D 的 关系:

D =1/2 c × T (2)

式中,c 为光速。三维 TOF 图像传感器具有广阔的应用前景,其 中一个重要的应用领域便是车载激光雷达(Light DetectionandRanging, LiDAR) [38] , 根据激光发射方式的不 同,三 维 TOF 成像系统可以分为 Flash 型和 Scanning 型, Flash型采用面发射激光,一次照亮整个场景,并采用面阵传 感器接收;Scanning型采用线发射激光对场景扫描,接收端可 以采用线阵传感器也可以采用面阵传感器。

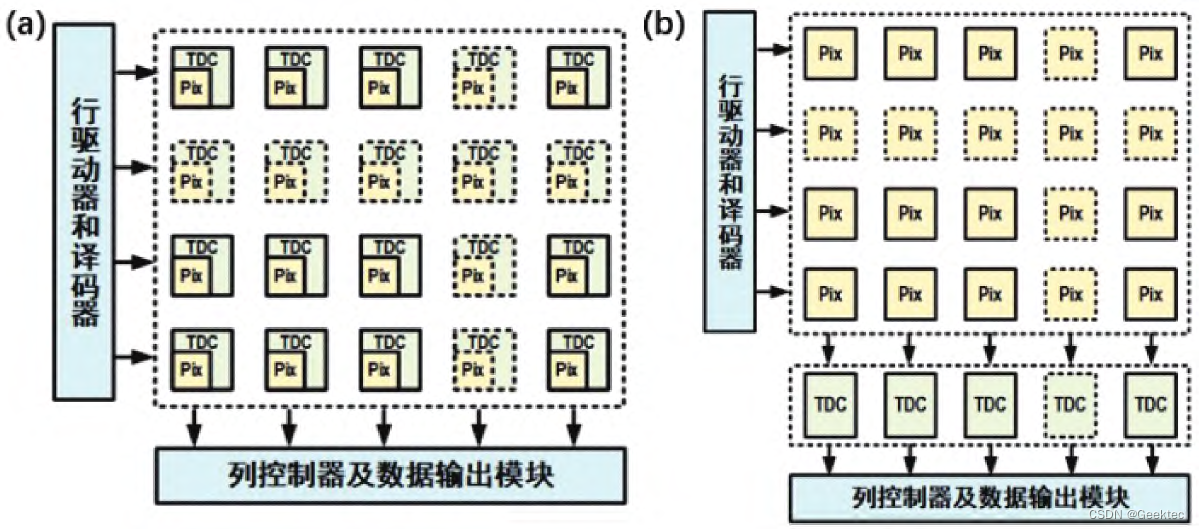

根据 TDC 位置 的不 同,TOF 图像传感器架构上分为 像素 级 TDC 架构和列共享式 TDC 架 构,如 图 33 所 示。 采用像素级 TDC , 传感器能够 以全局曝光的模式工作,可 配合面阵激光实现 Flash 三维成像,但 TDC 结构复杂、面 积较大,通常会导致像素的填充因子降低,采用三维堆叠 工艺可以一定程度避免此问题 。采用列共享式 TDC 架构 不影响像素填充因子,既可 以配合面 阵激光实现 Flash 三 维成像,也可 以配合线 阵激光实现 Scanning 扫描成像,但 帧率通常小于全局曝光的图像传感器。

((a)像素级 TDC架构;(b)列共享 TDC 架构)

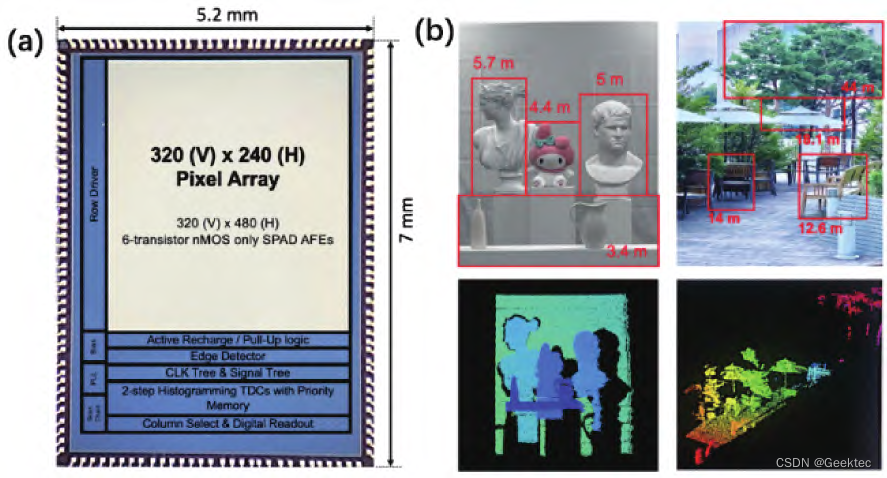

2019 年,代尔夫特理工大学 的张超等人基于 180nm 工艺实现了一款分辨率为 252×144 的 SPAD 三维 图像传 感器,采用共享 TDC方式,最远测距范 围为 50 m , 测距准 确度为 0.088 m[39] 。2024 年,韩 国成均馆 大 学 Minkyung Kim 等人基于 110nm 工艺,采用 6 个 NMOS 晶体管组成 的 SPAD像素 电路,结合列共享直方 图统计型 TDC , 实现 了分辨率为 320×240 、最远测距范 围为 48 m 的三维 图像 传感器,测距准 确度 为 0 . 057 m , 芯 片 照 片 如 图 34(a) 所 示,三维成像结果如图 34(b) 所示[40] 。

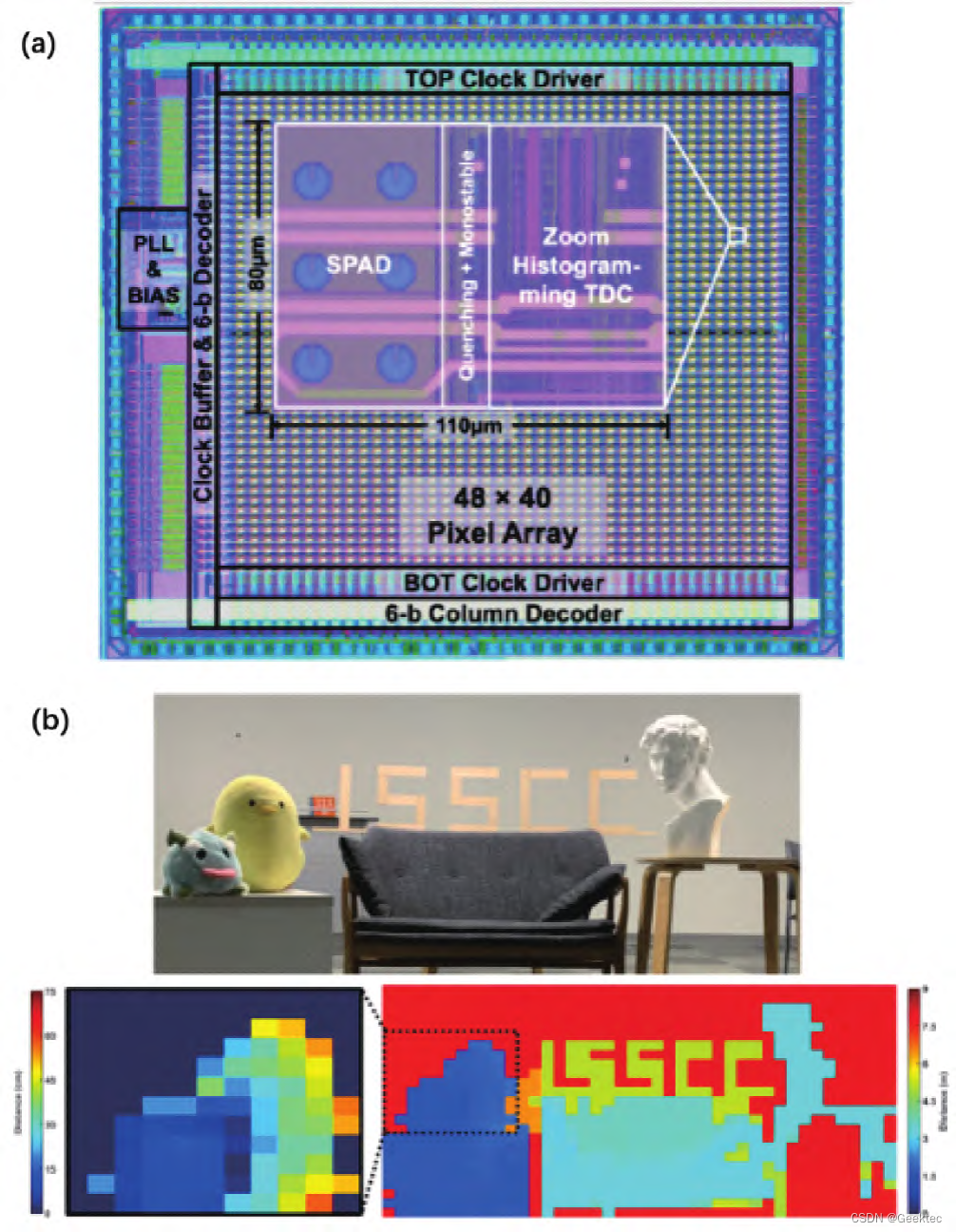

韩 国蔚山科学技术院的 Bumjun Kim 等人采用像 素 级直方 图 统 计 型 TDC 实现的 一 款分辨率为 48×40 的 Flash 型 SPAD 三维 图像传感器,芯 片 照 片 如 图 35(a) 所示,三维成像结果如图 35(b) 所示[41] 。该 图像传感器可实 现最远 96m 的测距范 围,测距准确度为 0.04m 。

((a)芯片照片;(b)三维成像结果[40] )

((a)芯片照片;(b)三维成像结果[41] )

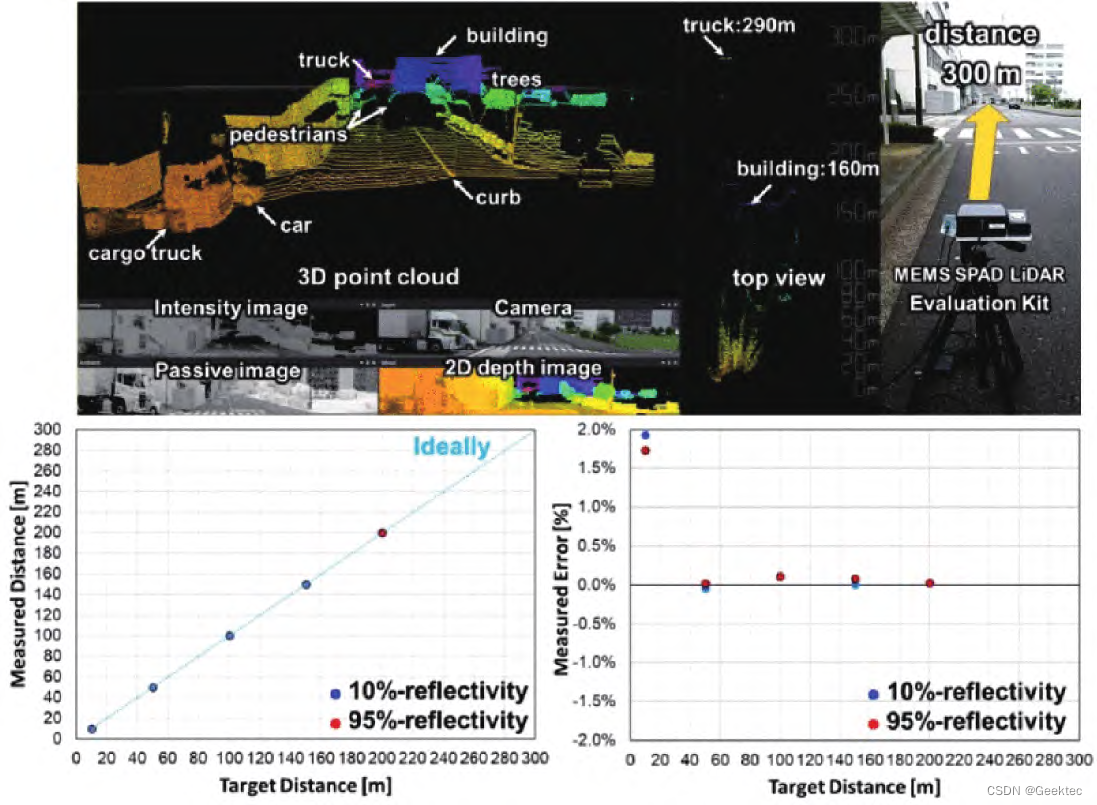

索尼公司基于三维堆叠工艺设计的 SPAD 三维 图像 传感器采用 Scanning 方式,可实现最远 150~200 m 的测 量距离,其测距准确度为 0.15~0.3m , 像素尺寸为10 μm , SPAD 阵列大小为 189×600 , 三维成像帧率为20fps , 成像 效果如 图 36 所 示[42] 。 在激光雷达应 用需求的驱动下,SPAD 三维成像技术在 向着更远探测距离和更高准确度 方向不断发展。

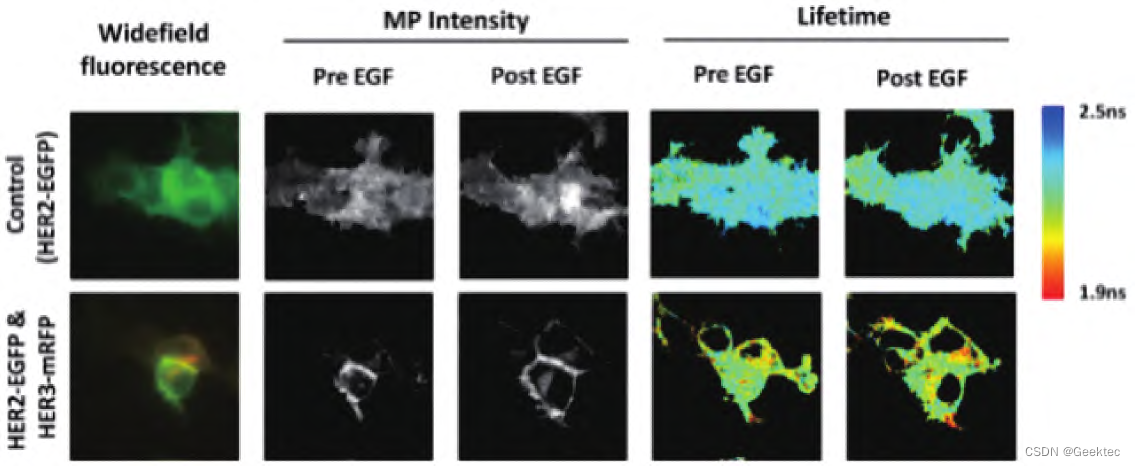

4.2 荧光寿命成像

SPAD 图像传感器所具有的时空分辨特性还能够实 现荧光寿命 成 像(Fluorescence Lifetime Imaging Micros- co py, FLIM) 。 荧光寿命成像技术被用来实现对微环境中 许多生化参量的定量测量,如细胞中折射率、黏度、温度、 pH 值的分布和动力学 的变化等,能十分灵敏地反映激发 态分子与周围微环境的相互作用及能量转移过程,成像效 果如 图 37 所示[43] , 在生物医学研究中具有非常重要的意 义 。SPAD 图像传感器能够探测非常微弱的光强(单光子 量级),且可以通过门控信号控制 SPAD 的工作状态,便于 对样品在时间和空间上进行采样和计算,最后得到高质量 成像效果,具有响应速度快、体积小、功耗低等优点[44] 。

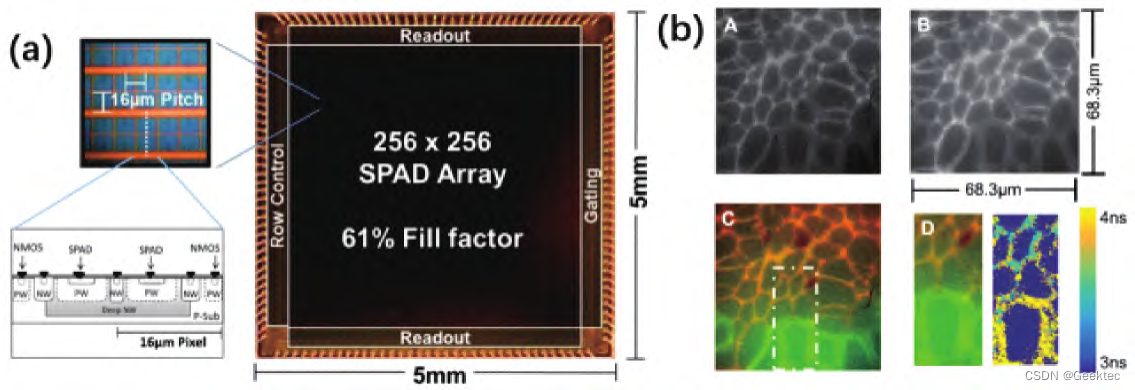

应用于 FLIM 成像 的 SPAD 图像传感器通常采用 时 间 门控方式,具体原理在前文中已经做了介绍 。2018 年, 英 国爱丁 堡 大 学 的 Gyongy 等人设计的 一 款分辨率为 256×256的 SPAD 图像传感器,如 图 38(a) 所示[45] , 该 图 像传感器基于 130nm CMOS 工艺,像素尺寸为 16 μm , 填充 因子为 61% , 最小 门控时 间宽度为 4ns , 其荧光寿命成 像结果如 图 38(b) 所示[45] 。

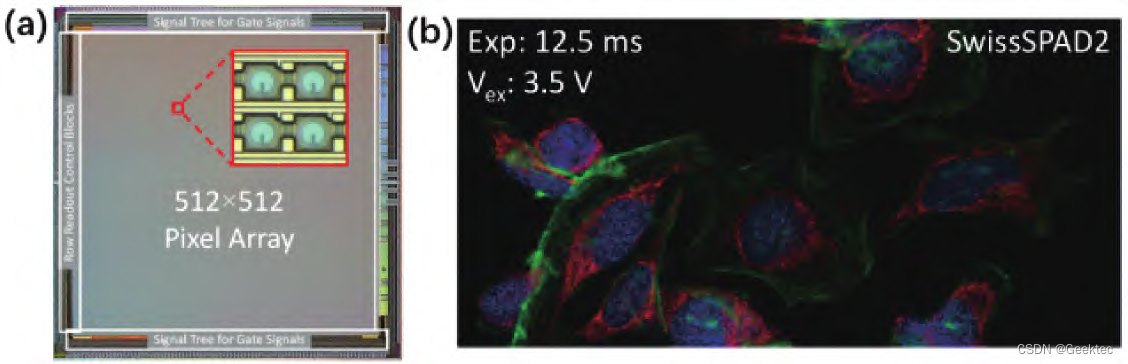

2019 年,瑞士洛桑联邦理工学 院 的 Ulku 等人设计 了 代号为“SwissSPAD2”的单光子 图像传感器 。 该 图像传感 器基于 180nm CMOS 工艺,分辨率为 512×512 , 填充 因 子为 10.5% , 最大成像 帧率 为 97.7kfps(1bit) , 最 小 门控 时 间为 5.75ns , 芯片照片如 图 39(a) 所示,FLIM 成像结果 如 图 39(b) 所示[46] 。

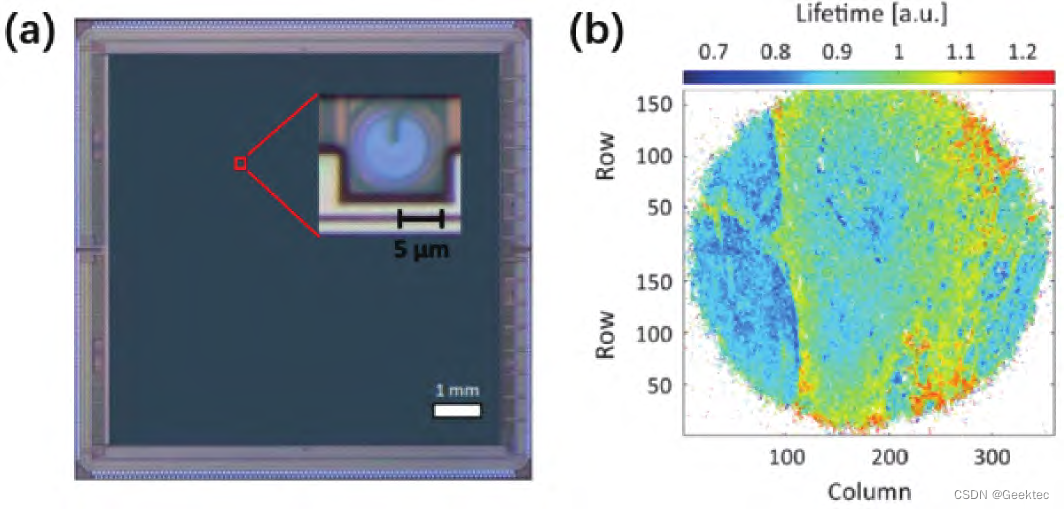

2022 年,同样是瑞士洛桑联邦理工学院的 Wayne 等 人,在 上述基础上实现了 一 款 代 号 为“ SwissSPAD3 ”的 SPAD 图像传感器,该传感器分辨率为 500×500 , 最 小 门 控时 间缩短至 1ns , 最大成像 帧率为 49.8kfps , 芯片照片 如 图 40(a) 所示,FLIM 成像 结果如 图 40(b) 所示[47] 。 随 着相关技术 的进 步,SPAD 荧光寿命成像也在快速发展, 其成像速度和成像精度必将得到进一步提升。

5 结 语

单光子图像传感器具有灰度成像、深度成像和荧光寿 命成像等多种视觉信 息获取 能力,同时具有高灵敏度、高 动态范围和高时 间分辨率 的优越性 能 。 随着工艺技术的 飞速发展,SPAD 器件尺寸越来越小,器件性 能逐步提升。 三维堆叠工艺的引入,也使像素器件和电路性能可 以分别 优化,SPAD 单光子成像技术 的优越性能逐步得到充分利 用,像素分辨率、动态范围以及测距范围等不断提升,展示出了巨大的应用潜力,未来必将在实际场景中越来越 多地 看到 SPAD 图像传感器的身影。

789

789

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?