- 题目:INTACT: A 96-Core Processor With Six Chiplets 3D-Stacked on an Active Interposer With Distributed Interconnects and Integrated Power Management

- 时间:2021

- 期刊:JSSC

- 研究机构:法国CEA-LETI

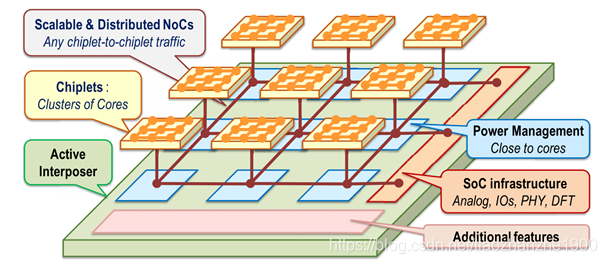

1 introduction

first CMOS active interposer integrating

- power management without any external components

- distributed interconnects enabling any chiplet-to-chiplet communication

- system infrastructure, design-for-test, and circuit IOs

- 题目:A 7-nm 4-GHz Arm-Core-Based CoWoS Chiplet Design for High-Performance Computing

- 时间:2020

- 期刊:JSSC

- 研究机构:TSMC

1 introduction

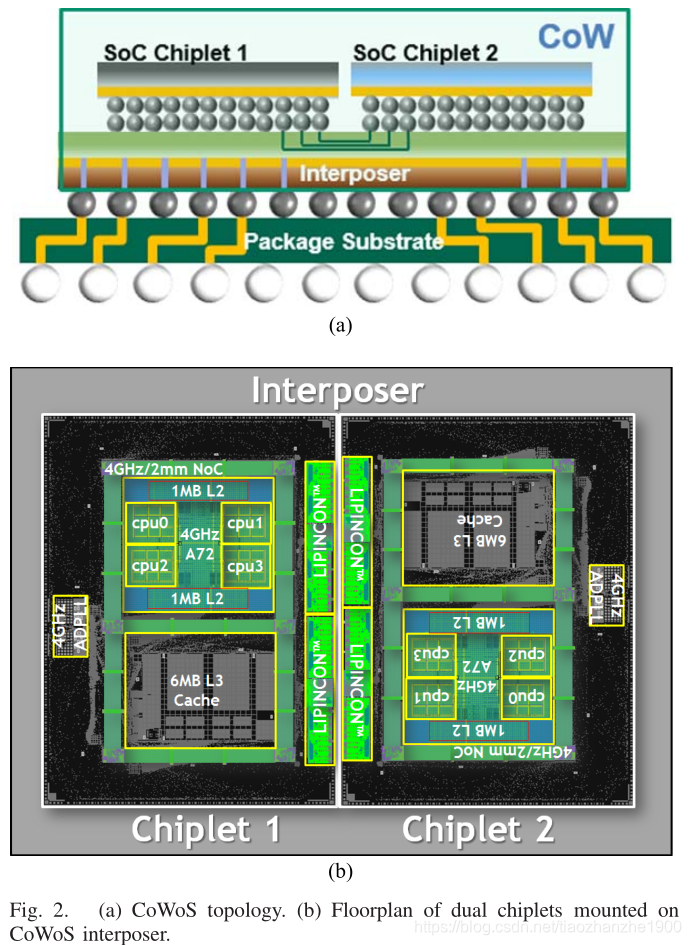

We present a dual-chiplet interposer-based system-in-package (SiP) octo-core processor using Chip-on-Wafer-on-Substrate (CoWoS) technology

本篇论文的主要贡献(三大目标)

- 4GHz的ARM核,用于高性能计算

- validate the design and operation of the on-die bidirectional interconnect mesh bus above 4.0 GHz for 2-mm long flop-to-flop transfers

- 基于CoWoS interposer的chiplet片间互联,带宽达到了8Gbps和0.56pJ/b

由上图可以看出,每个chiplet是4个A72的ARM核,interposer上放了两个chiplet,chiplet之间是 Low-voltage-In-Package-INterCONnect (LIPINCON)的并行接口,vdd、gnd等信号通过TSV孔直接连到package substrate

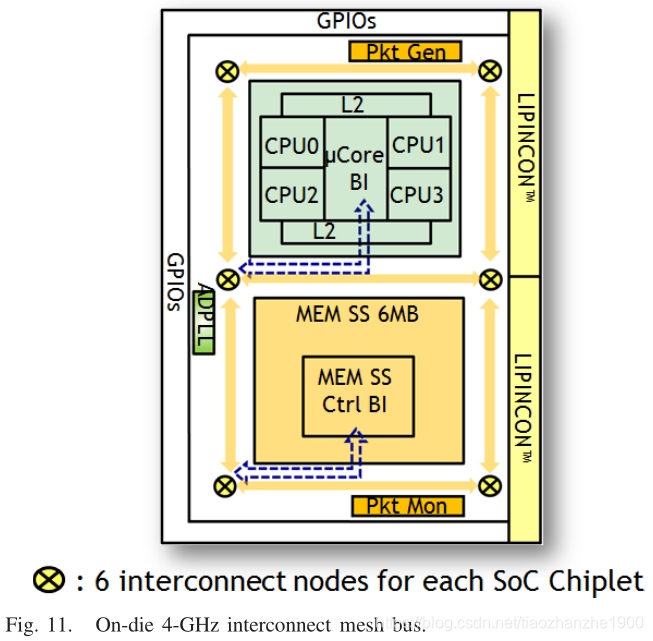

2 互联

片上部分:每个chiplet有6个双向的互联节点,mesh buss宽1968bit,在Metal-12和Metal-13中使用三重间距的P256 (256纳米间距)金属层进行布线。相邻导线方向相反,以最大限度地减少耦合。

片间互联:物理层采用了LIPINCON,实现点对点通信,LIPINCON引用自A 16 nm 256-bit wide 89.6 GByte/s total bandwidth in-package interconnect with 0.3 V swing and 0.062 pJ/bit power in InFO package 2016 Hot Chips

3933

3933

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?