一、为什么要用Serdes

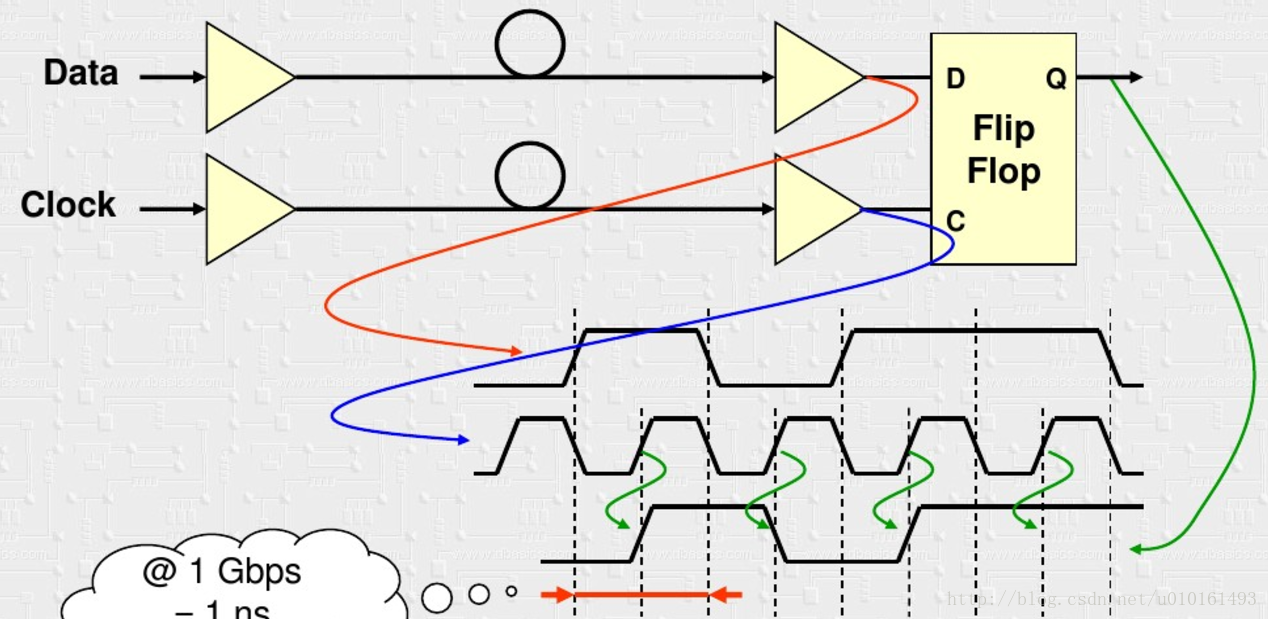

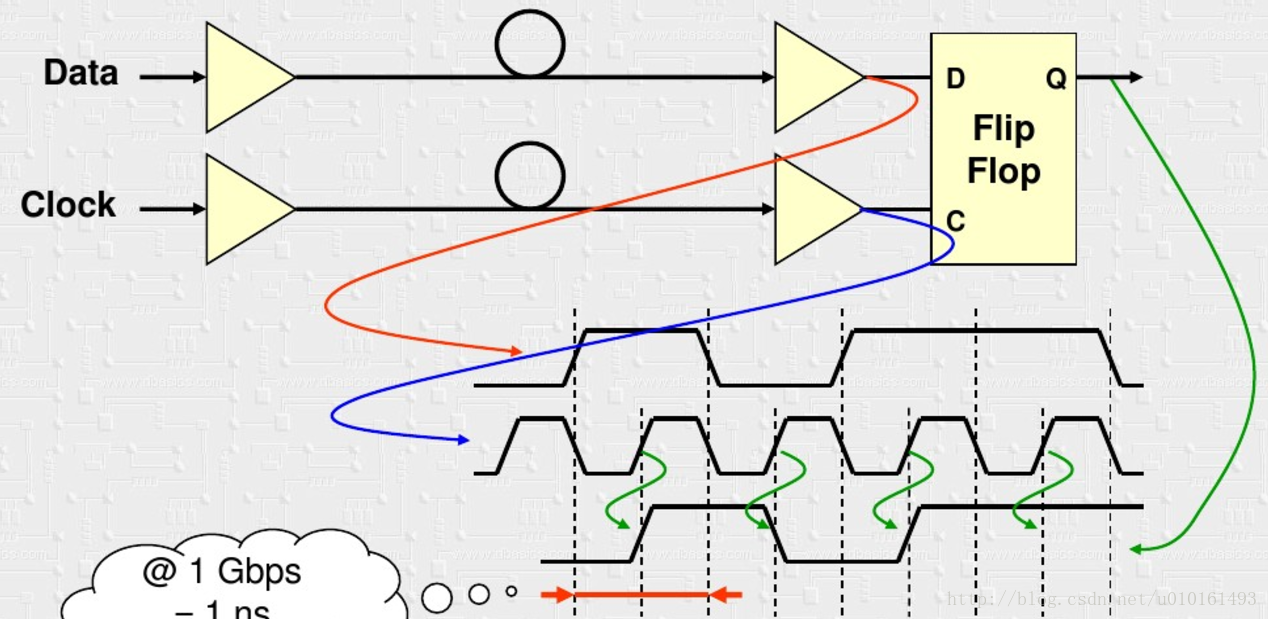

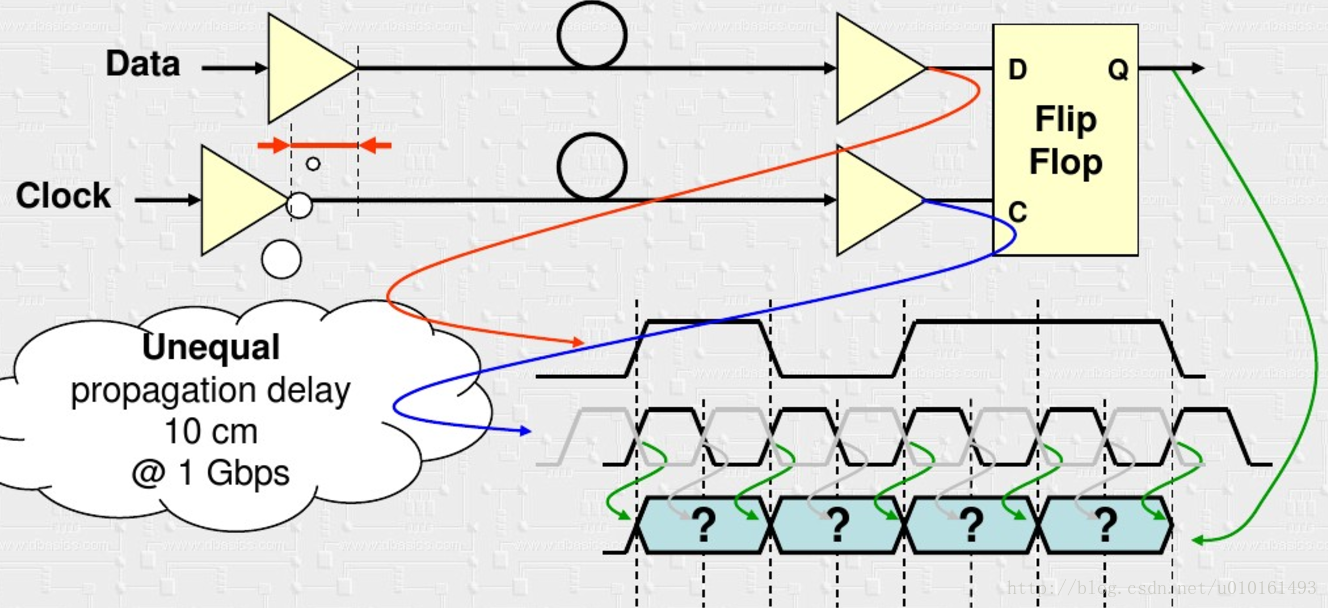

传统的源同步传输,时钟和数据分离。在速率比较低时(<1000M),没有问题。

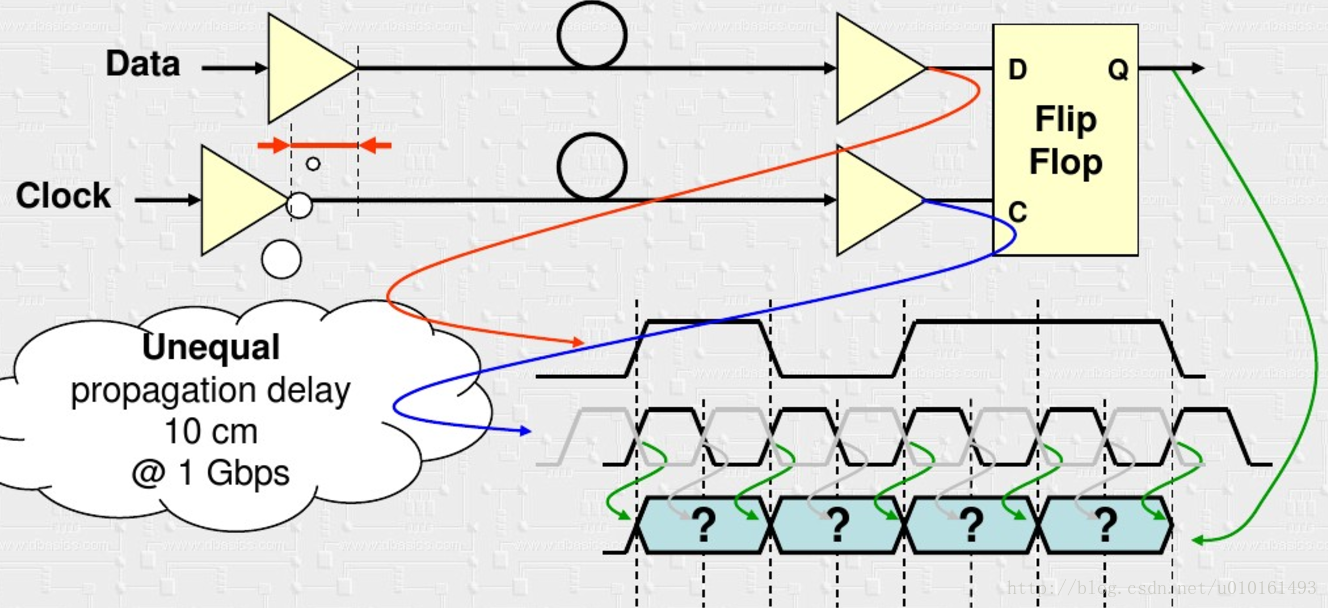

在速率越来越高时,这样会有问题

由于传输线的时延不一致和抖动存在,接收端不能正确的采样数据,对不准眼图中点。

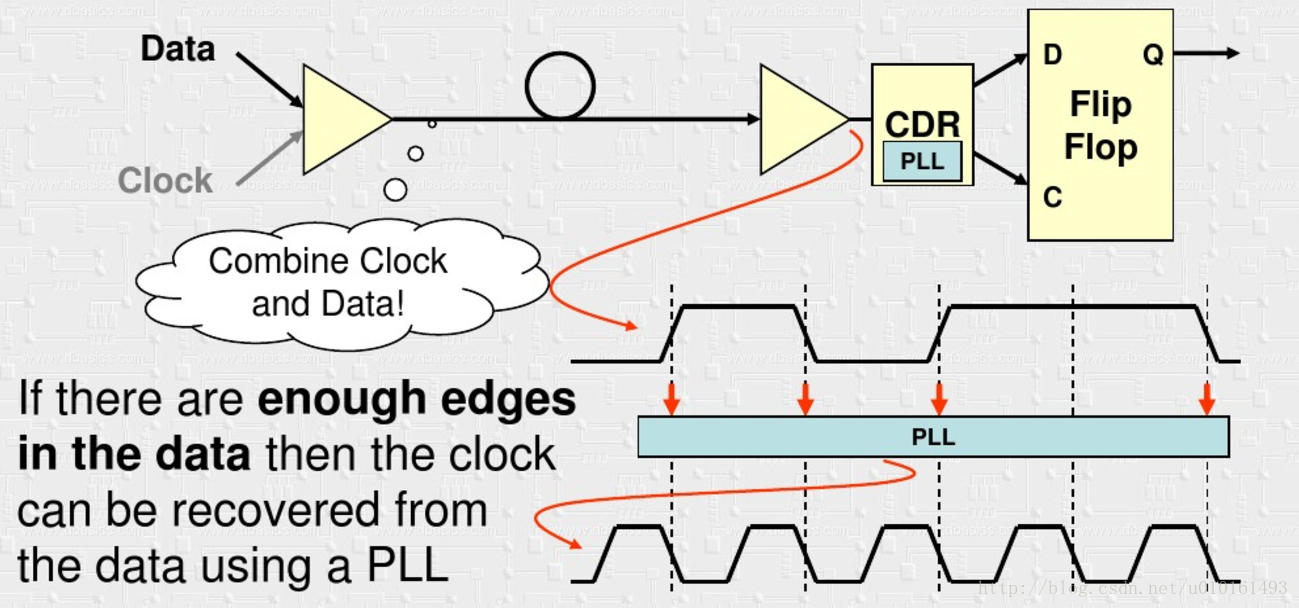

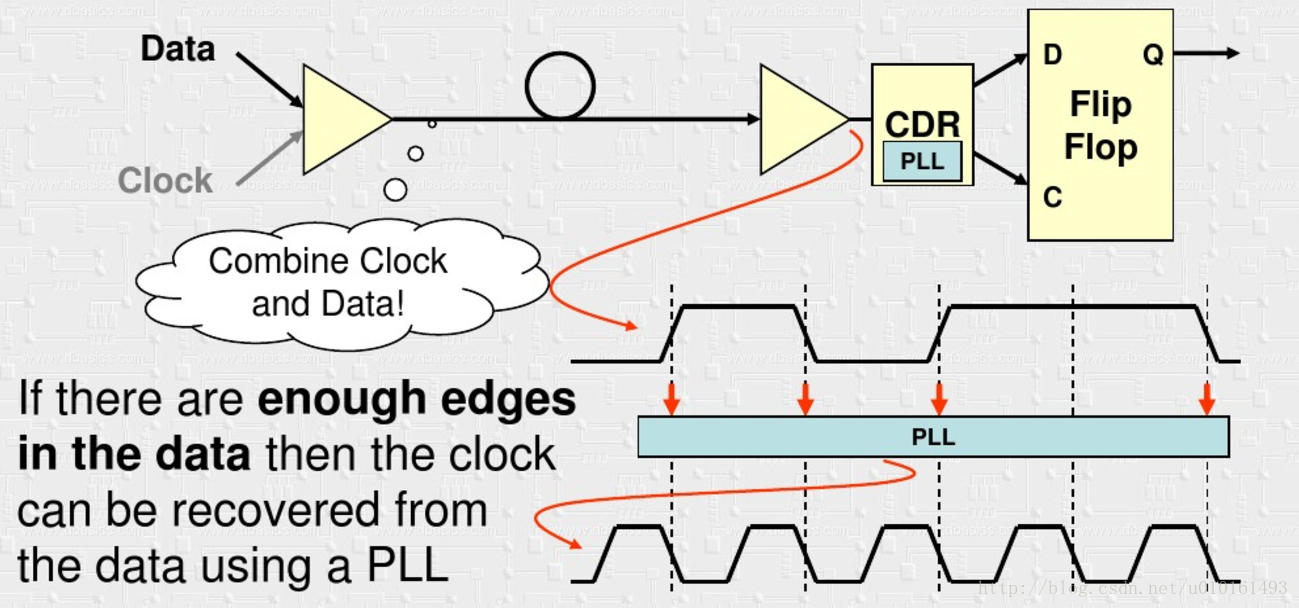

然后就想到了从数据里面恢复出时钟去采样数据,即CDR

这样就不存在延迟不一致的情况,有轻微的抖动也不会

传统的源同步传输,时钟和数据分离。在速率比较低时(<1000M),没有问题。

在速率越来越高时,这样会有问题

由于传输线的时延不一致和抖动存在,接收端不能正确的采样数据,对不准眼图中点。

然后就想到了从数据里面恢复出时钟去采样数据,即CDR

这样就不存在延迟不一致的情况,有轻微的抖动也不会

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?