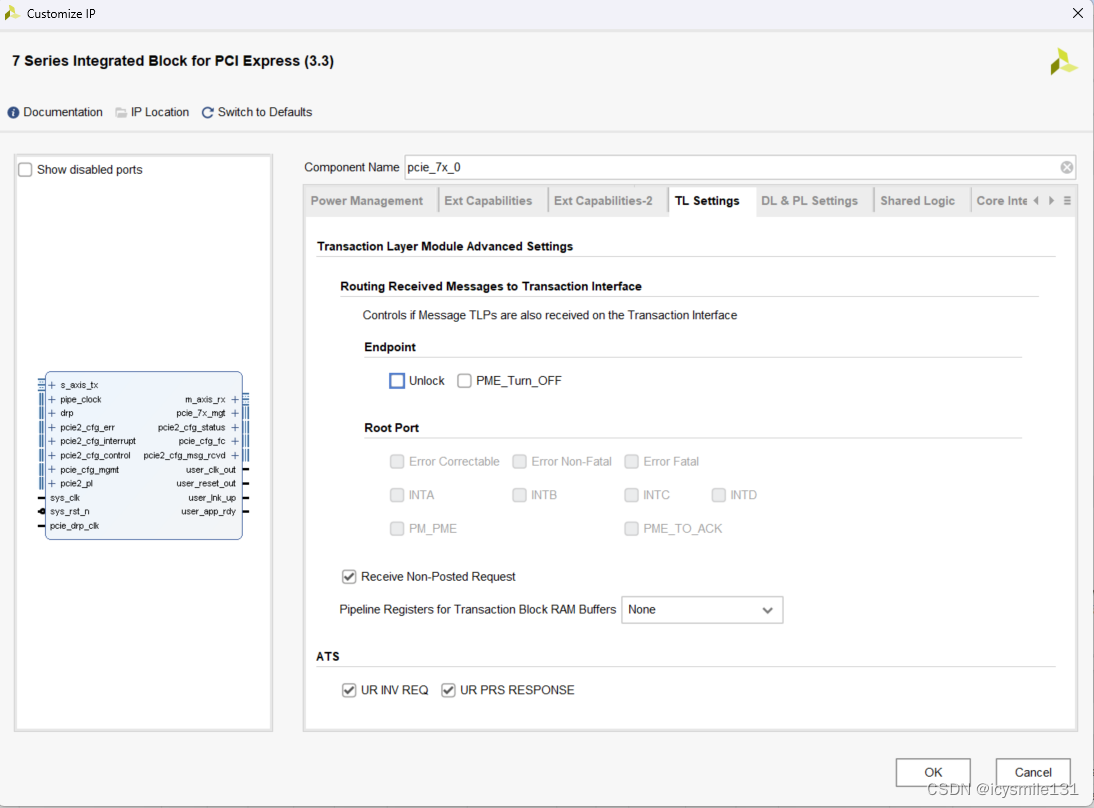

1 TL Settings

Transaction Layer (TL)设置只在Advanced模式下有效。

-

Endpoint:

- Unlock and PME_Turn_Off Messages: 与端点的电源管理相关,允许发送解锁和电源管理事件关闭消息。

-

Root Port:

- Error Messages: Error Correctable(错误可纠正)、Error Non-Fatal(错误非致命)、Error Fatal (错误致命)等消息,这些与PCIe总线的错误处理和报告有关。

- Assert/Deassert INT Messages: 中断信号的发送和清除机制,包括INTA、INTB、INTC、INTD。

- Power Management Messages: 与电源管理相关的事件消息,如PM_PME(电源管理事件)和PME_TO_ACK(电源管理事件确认)。

-

Receive Non-Posted Request (Non-Posted Flow Control):

- rx_np_req 信号用于防止用户应用程序缓冲非发布TLP。当rx_np_req被声明时,会向集成块请求一个非发布的TLP。此信号不能与rx_np_ok一起使用。每次rx_np_req被声明时,都会在接收接口上显示一个TLP;而每次rx_np_ok被取消声明时,用户应用程序需要缓冲最多两个额外的非发布TLP。

-

Pipeline Registers for Transaction Block RAM Buffers: 为事务缓冲区选择启用的流水线寄存器。流水线寄存器可以在事务块RAM缓冲区的写路径或读写路径上启用。

-

ATS (Address Translation Services):

- UR_INV_REQ: 如果选中此框,IP核会将收到的ATS Invalidate请求消息视为不支持的请求。如果未选中此框,IP核将传递收到的ATS Invalidate请求消息。

- UR_PRS_RESPONSE: 如果选中此框,IP核会将收到的ATS页面请求组响应消息视为不支持的请求。如果未选中此复选框,IP核将传递收到的ATS PRG响应消息。

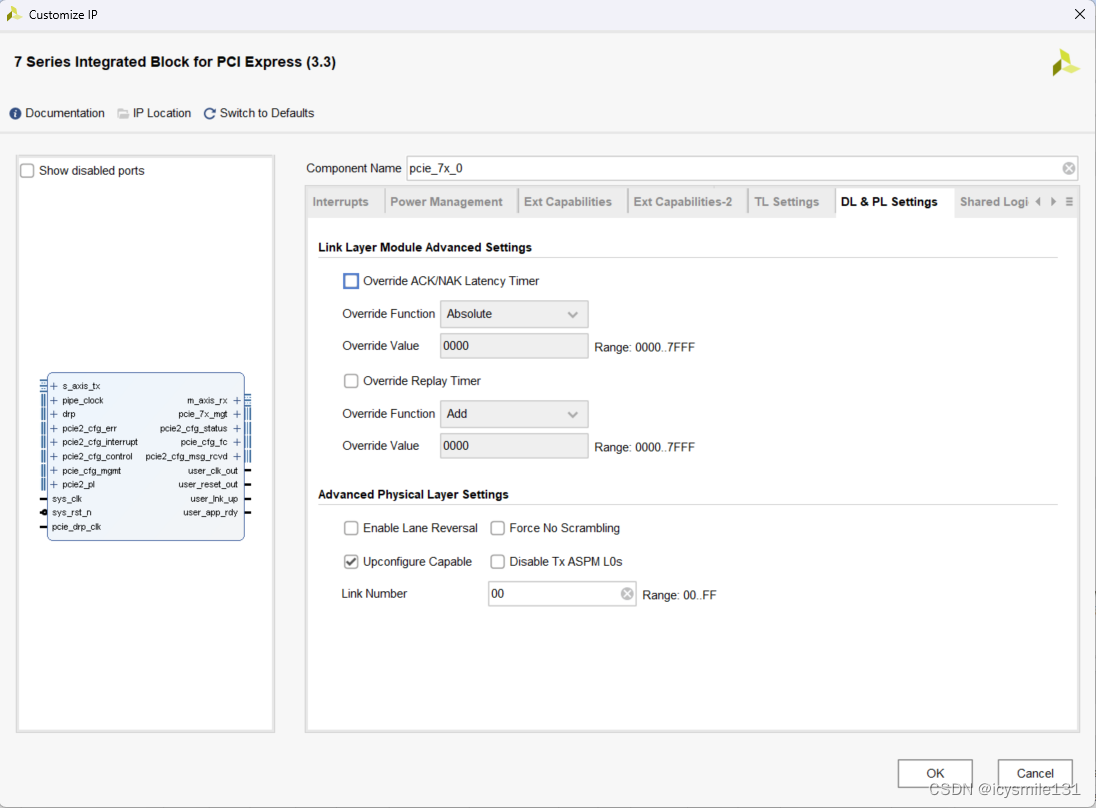

2 DL and PL Settings

“DL和PL设置”页面也仅在“高级模式”下可用。这表明,除了事务层设置外,还有与数据链路层(DL)和物理层(PL)相关的更高级设置。

2.1 Link Layer Module

- Override ACK/NAK Latency Timer: 勾选此选项后,用户可以覆盖设备中设置的ACK/NAK延迟计时器值。使用此功能可能会使ACK超时值不符合PCI Express基础规范2.1版。这通常用于执行高级调试操作。

警告:仅当Xilinx技术支持指导时,才应修改默认属性。

- ACK Latency Timer Override Function: 此设置决定了设备如何使用覆盖值相对于设备中的ACK/NAK延迟计时器值。选项包括“Absolute”(绝对值)、“Add”(增加)和“Subtract”(减少)。前两个设置可能会导致ACK超时值不符合PCI Express基础规范2.1版。

- ACK Latency Timer Override Value: 此设置根据是否启用了ACK延迟计时器覆盖功能来确定设备使用的ACK/NAK延迟计时器值。内置表值取决于设备的协商链路宽度和编程的MPS(最大有效载荷大小)。

- Override Replay Timer: 勾选此选项后,用户可以覆盖设备中设置的重放计时器值。使用此功能可能会使重放超时值不符合PCI Express基础规范2.1版。这也通常用于执行高级调试操作。

警告:仅当Xilinx技术支持指导时,才应修改默认属性。

- Replay Timer Override Function:这个设置决定了设备如何使用覆盖值来修改设备内的重放计时器值。可选项有“Absolute”(绝对值)、“Add”(增加)和“Subtract”(减少)。选择“Absolute”或“Add”可能会导致重放超时值不符合PCI Express基础规范2.1版。

- Replay Timer Override Value:此设置根据是否启用了重放计时器覆盖功能来确定设备使用的重放计时器值。内置表值取决于设备的协商链路宽度和编程的MPS(最大有效载荷大小)。

必须确保最终的超时值不会溢出15位的超时值范围。

2.2 Advanced Physical Layer

- Enable Lane Reversal: 勾选此选项后,将启用通道位置翻转(Lane Reversal)功能。这是一个可选功能,旨在解决PCB布局中可能出现的通道错序连接问题,以提高信号质量。

- Force No Scrambling: 此选项仅用于诊断目的,在正常设计中绝不应启用。设置此位将导致数据扰码器关闭,以便可以分析串行数据流。

- Upconfigure Capable: 若取消勾选,则在链路训练期间,该端口将被宣传为“不可进行配置升级(Not Upconfigure Capable)”。 这意味着该端口不支持在已建立的链路宽度和速度上进行进一步的配置升级。

- Disable TX ASPM L0s: 当勾选此选项时,会阻止设备发送器进入L0s状态。

对于连接7系列FPGA与任何Xilinx组件的链路,建议禁用TX ASPM L0s。

- Link Number: 指定设备在链路训练期间的TS1和TS2有序集合中宣传的链路号。仅用于下游模式(downstream facing mode,即设备作为下游设备时的模式)。

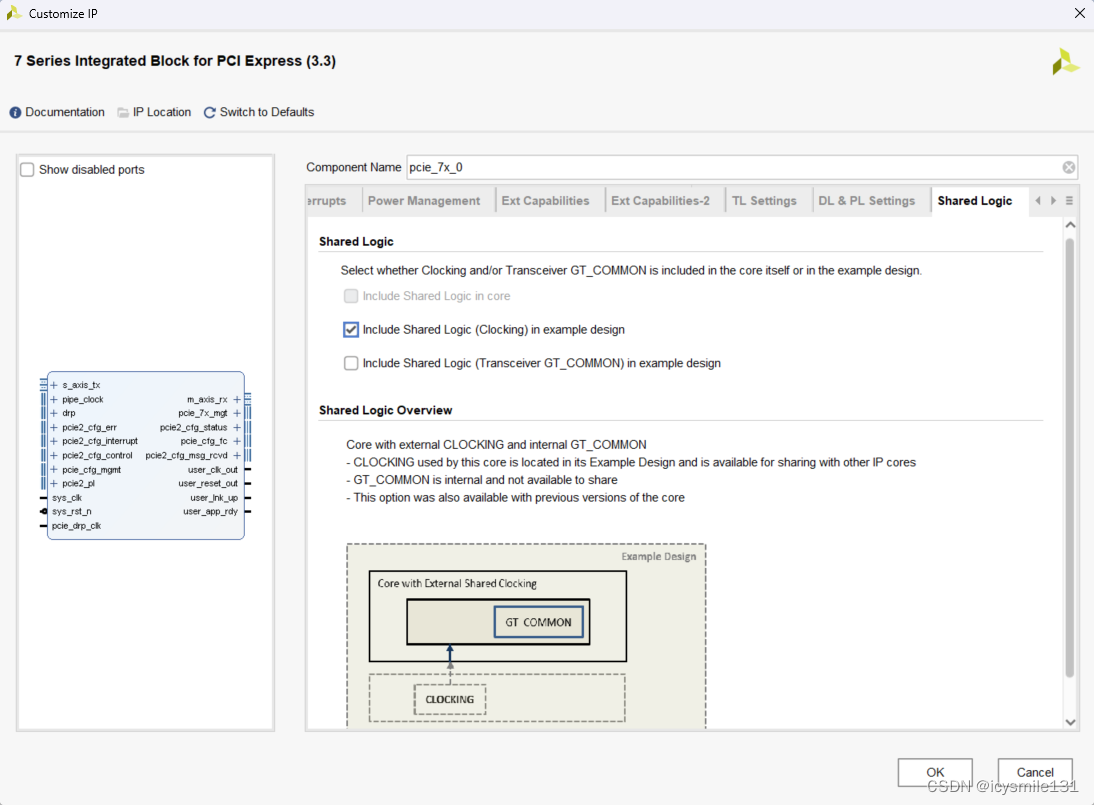

3 Shared Logic

通过选择此页面上的一个或多个选项,可以在多个实例化之间共享通用块。

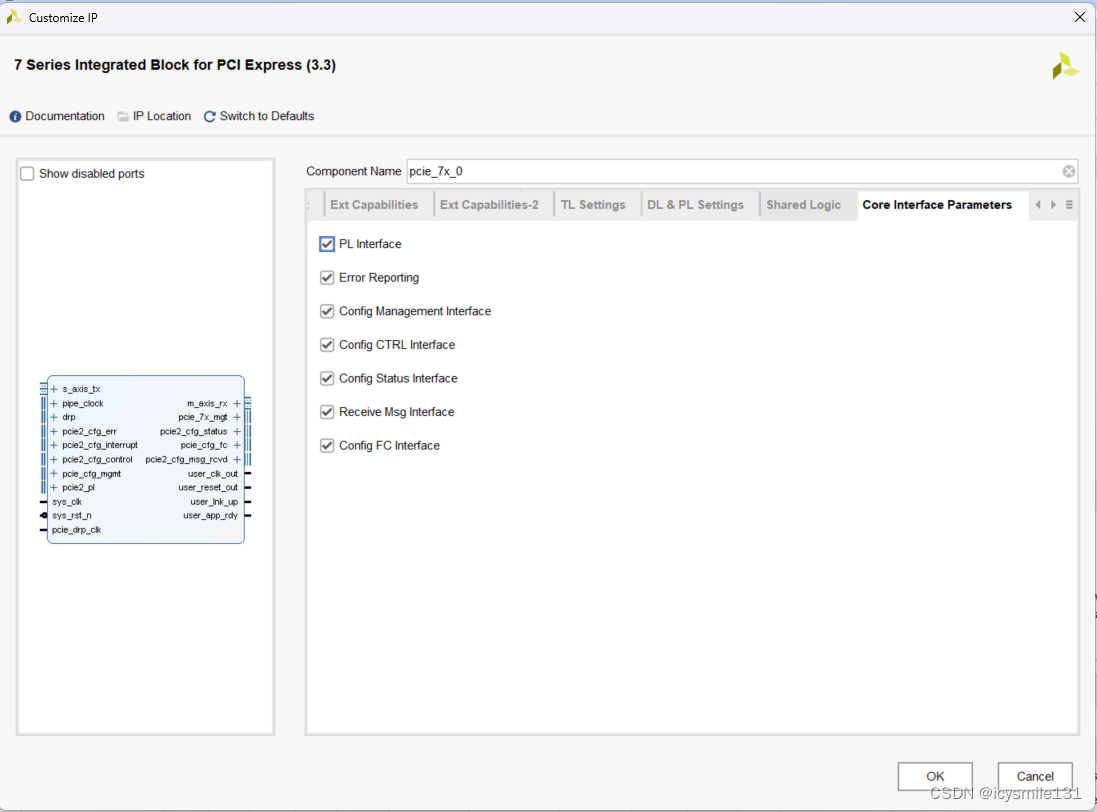

4 Core Interface Parameters

可以选择要使用的IP核接口参数。默认情况下,所有端口都会引出。

在某些情况下,如果某些接口未使用,您可能会选择禁用它们。当接口被禁用时,它们会从IP核顶部移除。对于典型用例,不要禁用接口。仅在特殊情况下禁用端口。

PL Interface

当你禁用物理层(PL)接口选项时,以下端口将从IP核中移除。这个选项允许你检查链路和链路伙伴的状态,并控制链路状态。被移除的端口包括:

- pl_sel_lnk_rate(选择的链路速率)

- pl_sel_lnk_width(选择的链路宽度)

- pl_ltssm_state(链路训练和状态机状态)

- pl_lane_reversal_mode(通道翻转模式)

- pl_phy_lnk_up(物理链路状态)

- pl_directed_link_change(定向链路更改)

- pl_directed_link_width(定向链路宽度)

- pl_directed_link_speed(定向链路速度)

- pl_directed_link_auton(定向链路自主协商)

- pl_tx_pm_state(发送电源管理状态)

- pl_rx_pm_state(接收电源管理状态)

- pl_link_upcfg_cap(链路升级配置能力)

- pl_link_gen2_cap(链路Gen2能力)

- pl_link_partner_gen2_supported(链路伙伴是否支持Gen2)

- pl_initial_link_width(初始链路宽度)

- pl_upstream_prefer_deemph(上游是否偏好去加重)

- pl_downstream_deemph_source(下游去加重源)

- pl_directed_change_done(定向更改完成)

- pl_transmit_hot_rst(发送热重置)

- pl_received_hot_rst(接收热重置)

Error Reporting

当你禁用错误报告选项时,以下与PCIe Gen2 IP核的用户应用程序错误报告接口相关的端口将从核心中移除:

- cfg_err_malformed(格式错误的配置请求)

- cfg_err_cor(可纠正的配置错误)

- cfg_err_ur(不支持的请求错误)

- cfg_err_ecrc(错误的ECRC)

- cfg_err_cpl_timeout(完成超时错误)

- cfg_err_cpl_abort(完成中止错误)

- cfg_err_cpl_unexpect(意外的完成错误)

- cfg_err_poisoned(中毒的TLP错误)

- cfg_err_acs(ACS违规错误)

- cfg_err_atomic_egress_blocked(原子出口被阻止错误)

- cfg_err_mc_blocked(多播被阻止错误)

- cfg_err_internal_uncor(内部不可纠正错误)

- cfg_err_internal_cor(内部可纠正错误)

-

cfg_err_posted(张贴请求错误)

- cfg_err_locked(锁定请求错误)

- cfg_err_norecovery(无法恢复的错误)

- cfg_err_cpl_rdy(完成就绪错误)

- cfg_err_tlp_cpl_header(TLP完成头错误)

- cfg_err_aer_headerlog(AER头日志错误)

- cfg_aer_interrupt_msgnum(AER中断消息编号)

- cfg_err_aer_headerlog_set(AER头日志设置错误)

- cfg_aer_ecrc_check_en(AER ECRC校验使能)

- cfg_aer_ecrc_gen_en(AER ECRC生成使能)

Config Management Interface

当你禁用配置管理接口选项时,以下端口将从端口中移除。这些信号用于读取和写入配置空间寄存器。被移除的端口包括:

- cfg_mgmt_do(数据输出)

- cfg_mgmt_di(数据输入)

- cfg_mgmt_byte_en(字节使能)

- cfg_mgmt_dwaddr(双字地址)

- cfg_mgmt_wr_rw1c_as_rw(将RW1C寄存器作为RW写入的使能)

- cfg_mgmt_wr_readonly(写入只读寄存器的使能,通常用于调试)

- cfg_mgmt_wr_en(写使能)

- cfg_mgmt_rd_en(读使能)

- cfg_mgmt_rd_wr_done(读/写完成信号)

Config CTRL Interface

当你禁用配置控制(CTRL)接口选项时,以下端口将从IP核中移除。这些信号允许用户应用程序和IP核之间进行广泛的信息交换。被移除的端口包括:

- cfg_trn_pending(事务挂起指示)

- cfg_pm_halt_aspm_l0s(停止ASPM L0s状态的电源管理暂停)

- cfg_pm_halt_aspm_l1(停止ASPM L1状态的电源管理暂停)

- cfg_pm_force_state_en(强制进入特定电源管理状态的使能)

- cfg_pm_force_state(强制的电源管理状态)

- cfg_dsn(数据源编号)

- tx_cfg_gnt(发送配置授权)

- rx_np_ok(接收非发布事务确认)

- rx_np_req(接收非发布事务请求)

- cfg_turnoff_ok(关闭确认)

- cfg_pm_wake(电源管理唤醒)

- cfg_pm_send_pme_to(发送PME到的位置)

- cfg_ds_bus_number(下游总线编号)

- cfg_ds_device_number(下游 设备编号)

- cfg_ds_function_number(下游功能编号)

Config Status Interface

-

cfg_status(状态寄存器)

- cfg_command(命令寄存器)

- cfg_dstatus(设备状态寄存器)

- cfg_dcommand(设备命令寄存器)

- cfg_lstatus(链接状态寄存器)

- cfg_lcommand(链接命令寄存器)

- cfg_dcommand2(设备命令2寄存器,用于PCI Express的扩展功能)

- cfg_pcie_link_state(PCIe链接状态)

- cfg_pmcsr_powerstate(电源管理控制状态寄存器的电源状态)

- cfg_pmcsr_pme_en(电源管理事件使能)

- cfg_pmcsr_pme_status(电源管理事件状态)

- cfg_received_func_lvl_rst(接收到的功能级别重置)

- cfg_to_turnoff(即将关闭指示)

- cfg_bus_number(总线编号)

- cfg_device_number(设备编号)

- cfg_function_number(功能编号)

- cfg_bridge_serr_en(桥接错误报告使能)

- cfg_slot_control_electromech_il_ctl_pulse(插槽控制的机电信号或脉冲控制)

- cfg_root_control_syserr_corr_err_en(启用或禁用可纠正的错误)

- ,cfg_root_control_syserr_non_fatal_err_en(启用或禁用非致命错误)

- cfg_root_control_syserr_fatal_err_en(启用或禁用致命错误)

- cfg_root_control_pme_int_en(启用或禁用电源管理事件中断)

- cfg_aer_rooterr_corr_err_reporting_en(启用或禁用可纠正的错误报告)

- cfg_aer_rooterr_non_fatal_err_reporting_en(启用或禁用非致命错误报告)

- cfg_aer_rooterr_fatal_err_reporting_en(启用或禁用致命错误报告)

- cfg_aer_rooterr_corr_err_received(指示是否已接收到可纠正的错误)

- cfg_aer_rooterr_non_fatal_err_received(指示是否已接收到非致命的错误)

- cfg_aer_rooterr_fatal_err_received(指示是否已接收到致命的错误)

- cfg_vc_tcvc_map(虚拟通道到物理通道的映射配置)

- tx_buf_av(传输缓冲区可用的指示信号)

- tx_err_drop(指示传输错误导致的数据包丢弃的信号)

- tx_cfg_req(发送配置请求)

Receive Msg Interface

当禁用“接收消息接口”选项时,以下端口将从核心中移除。这些信号通常与从链路接收到的可解码消息、与数据相关的参数以及接收到的消息类型有关。

- cfg_msg_received(消息已被接收的信号)

- cfg_msg_data(接收到的消息数据的信号)

- cfg_msg_received_err_cor(接收到可纠正错误的消息)

- cfg_msg_received_err_non_fatal(接收到不致命错误的消息)

- cfg_msg_received_err_fatal(接收到致命错误的消息)

- cfg_msg_received_assert_int_a (接收到消息后触发中断a的声明)

- cfg_msg_received_deassert_int_a(接收到消息后取消触发中断a的声明)

- cfg_msg_received_assert_int_b (接收到消息后触发中断b的声明)

- cfg_msg_received_deassert_int_b(接收到消息后取消触发中断b的声明)

- cfg_msg_received_assert_int_c (接收到消息后触发中断c的声明)

- cfg_msg_received_deassert_int_c(接收到消息后取消触发中断c的声明)

- cfg_msg_received_assert_int_d (接收到消息后触发中断d的声明)

- cfg_msg_received_deassert_int_d(接收到消息后取消触发中断d的声明)

-

cfg_msg_received_pm_pme:(接收到了一个与电源管理相关的PME消息)

-

cfg_msg_received_pme_to_ack(表示PCIe设备接收到一个需要确认的PME消息)

-

cfg_msg_received_unlock(表示接收到了一个解锁消息)

-

cfg_msg_received_pm_as_nak(表示设备接收到一个它不能处理或不支持的电源管理请求并返回一个NAK响应)

Config FC Interface

当禁用“配置流控制(FC)接口”选项时,以下与PCIe Gen2核心的配置流控制相关的端口将从IP核中移除:

-

cfg_fc_ph(Posted Header(PH)流控制信用)

-

cfg_fc_pd(Posted Data(PD)流控制信用)

-

cfg_fc_nph(Non-Posted Header(NPH)流控制信用)

-

cfg_fc_npd(Non-Posted Data(NPD)流控制信用)

-

cfg_fc_cplh(Completion Header(CPLH)流控制信用)

-

cfg_fc_cpld(Completion Data(CPLD)流控制信用)

-

cfg_fc_sel(选择不同类型的流控制信用)

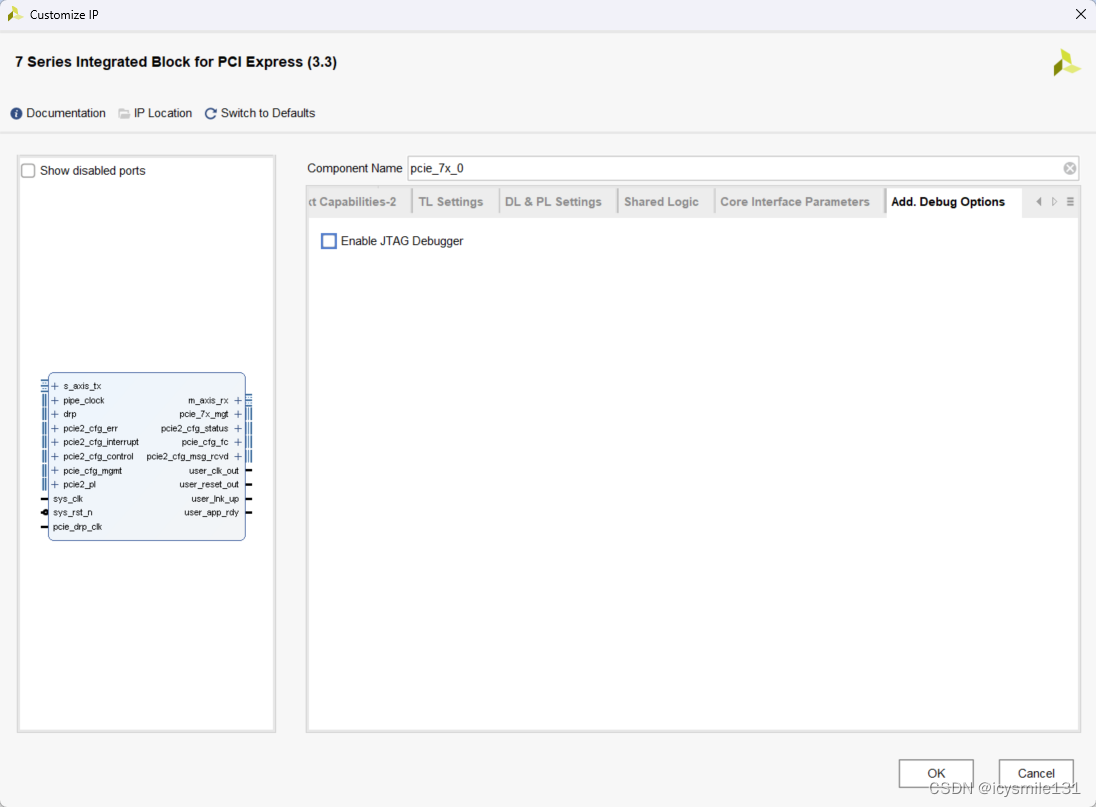

5 Add. Debug Options

关于“启用JTAG调试器以进行调试”的选项,这是为了提供硬件级别的调试支持。JTAG(Joint Test Action Group)是一个国际标准,用于测试和调试电子设备,特别是集成电路。启用这个选项将允许开发者通过JTAG接口连接调试器,对PCIe设备进行低级别的调试和分析。

该特性为以下方面提供了调试的可用性:

-

在IP核顶部集成PCIe调试选项:这个选项允许在用户设计中包含必要的PCIe调试功能。这意味着用户可以将专门的调试接口集成到他们的设计中,以便于在开发或故障排除过程中捕获和分析PCIe核心的行为。

-

外部时钟的使用:此功能假定将使用一个外部时钟源。在调试过程中,一个稳定的时钟源是至关重要的,因为它能确保时序的准确性和可预测性,这对于分析和诊断问题至关重要。

-

LTSSM(Link Training and Status State Machine)状态转换:这个功能可以展示从链路建立开始的所有LTSSM状态转换。LTSSM是PCIe中负责管理链路训练和状态的关键状态机。通过观察这些状态转换,开发人员可以了解链路是如何初始化、训练和进入稳定状态的,这对于解决链路层的问题至关重要。

-

PHY复位FSM(有限状态机)转换:此功能展示了PCIe解决方案IP使用的内部状态机(即PHY复位FSM)的转换情况。PHY是PCIe的物理层,负责数据的实际传输。通过监视PHY复位状态机的转换,开发人员可以洞察PHY层的行为和任何可能的问题。

-

接收器检测:这个功能显示了所有成功完成接收器检测的通道。接收器检测是PCIe链路建立过程中的一个重要步骤,它确保每个通道都能正确地接收数据。通过查看哪些通道成功通过了接收器检测,可以帮助定位可能存在的通道或连接器问题。

1549

1549

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?