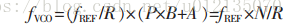

相关公式:

1、

限制条件: ((B>=3)||(B = 1))&&(B>A)

2、 N = (P × B) + A

where P can be 2, 4, 8, 16, or 32

1)Prescaler,

The prescaler of the AD9520 allows for two modes of operation

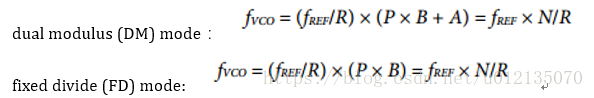

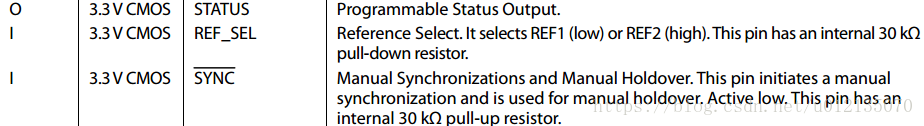

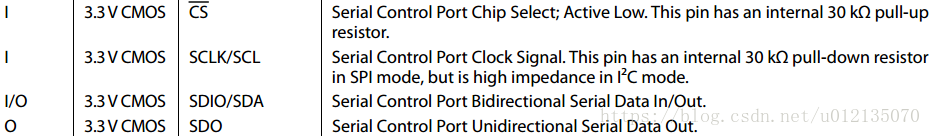

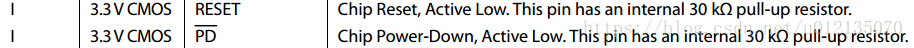

管脚描述:

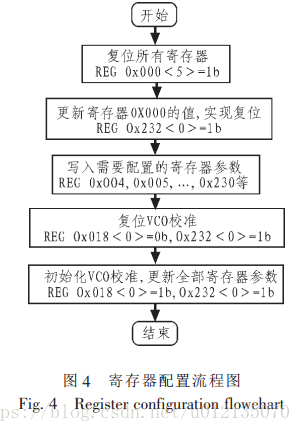

寄存器:

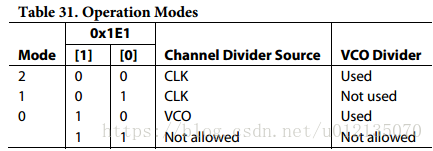

1、0x1E1<1:0> => 设置时钟源

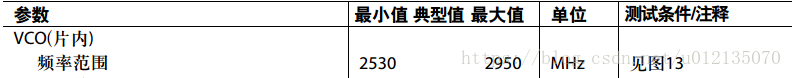

Table 31 shows how the VCO, CLK, and VCO divider are selected. 0x1E1[1:0] selects the channel divider source and determines whether the VCO divider is used. It is not possible to select the VCO without using the VCO divider.

2、PLL Reference Inputs:Either a differential or a single-ended reference must be specifically enabled. All PLL reference inputs are off by default. The differential input and the single-ended inputs share two pins, REFIN (REF1)/REFIN (REF2). The desired reference input type is selected and controlled by 0x01C (see Table 49 and Table 53[DATASHEET]).

Crystal mode is nearly identical to differential mode. The user enables a maintaining amplifier by setting the Enable XTAL OSC bit, and putting a series resonant, AT fundamental cut crystal across the REFIN/REFIN pins.

Manual switchover is performed either through Register 0x01C or by using the REF_SEL pin.

3、Reference Divider R:The reference inputs are routed to the reference divider, R. R (a 14-bit counter) can be set to any value from 0 to 16,383 by writing to 0x011 and 0x012. (Both R = 0 and R = 1 give divide-by-1.)

注意事项: 1)The output of the R divider goes to

本文详细介绍了AD9520时钟发生器的PLL配置,包括限制条件、参考分频器R、VCO/VCXO反馈分频器N的设置,并强调了VCO分频器在频率划分中的作用。还提到了如何通过EEPROM进行配置存储,以及在配置过程中应注意的事项,如占空比限制和错误检查。同时,提供了配置示例和常见问题解决方案。

本文详细介绍了AD9520时钟发生器的PLL配置,包括限制条件、参考分频器R、VCO/VCXO反馈分频器N的设置,并强调了VCO分频器在频率划分中的作用。还提到了如何通过EEPROM进行配置存储,以及在配置过程中应注意的事项,如占空比限制和错误检查。同时,提供了配置示例和常见问题解决方案。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

2563

2563

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?