注意interleaving和out of order的区别:

一个burst请求是一个transaction,假设transaction的burst length=5。那么数据通道对于一个transaction来说会有5个transfer。假设2个transaction的ID分别为ID0和ID1。每个transaction之间的transfers分别为:ID0_0、ID0_1、ID0_2、ID0_3、ID0_4,每个transfer对应一个beat。

out of order:

ID请求序列:ID0、ID0、ID0、ID1、ID1、ID1。

返回数据:ID0、ID1、ID0、ID1、ID0、ID1。

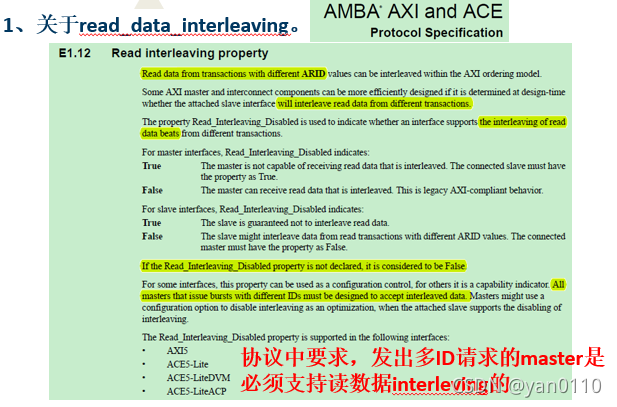

interleaving:

ID0_0、ID1_0、ID1_1、ID1_1、ID0_2、ID1_2、ID0_3、ID1_3、ID0_4、ID1_4......

axi4 后写数据不支持interleaving,因为没了WID信号。

简单说了,乱序是salve返回master请求的out of order特性,但这个slave可以是广义上的,一般总线会完成这个功能;而间插(interleaving)读返回数据,按找不同ID交织出现。比如:ID0 ID1 ID0 ID1....。乱序和间插都有深度,一般乱序深度比间插大的多。上面那个例子就是间插深度为2的情况。

1499

1499

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?