VHDL基础——状态机篇(1)

Moore型

输出只取决于当下的状态,用枚举类型来表示状态可以提高程序的可读性:

type state is (state1,state2,state3);

假设此时有一个状态机有三个状态,s0(000),s1(001),s2(010)。起始状态为s0,同时在din信号的作用下,改变其状态值。din=1时:s0->s1->s2->s0。在din=0时,保持原有状态。

有两种书写格式,推荐使用第二种。

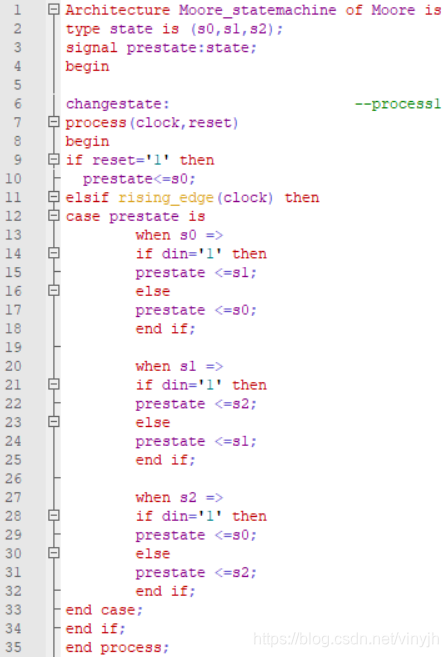

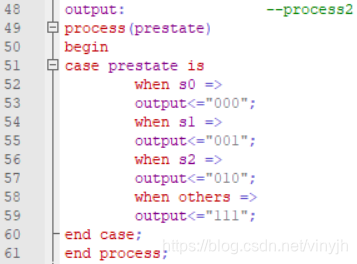

法1:两个process:一个进程用以状态的转移,一个进程用以判断输出。

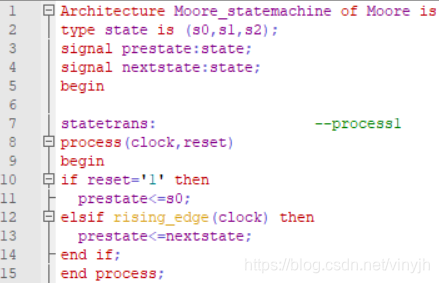

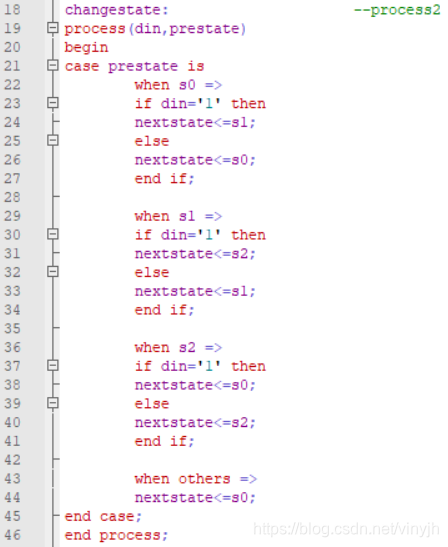

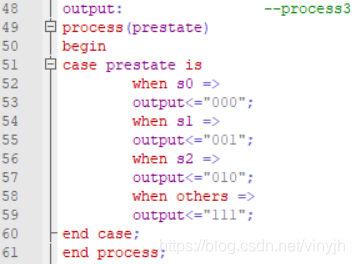

法2:三个进程:一个进程用以状态的存储;一个进程用以状态的改变;第三个进程用以判断输出(2和3可以合并成一个)

本文深入探讨了VHDL中Moore型状态机的设计原理,重点讲解了如何使用枚举类型来表示状态,以及两种不同的状态机实现方法,包括状态转移和输出判断的过程。

本文深入探讨了VHDL中Moore型状态机的设计原理,重点讲解了如何使用枚举类型来表示状态,以及两种不同的状态机实现方法,包括状态转移和输出判断的过程。

2017

2017

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?